#### Université de Montréal

# Parallelization of SAT on Reconfigurable Hardware An Architectural Exploration of Techniques

Par

Teodor Ivan

Département d'informatique et recherche opérationnelle Faculté des arts et des sciences

Mémoire présenté à la Faculté des arts et des sciences en vue de l'obtention du grade de Maître ès sciences (M.Sc.) en informatique

Avril, 2013

© Teodor Ivan, 2013

#### Résumé

Quoique très difficile à résoudre, le problème de satisfiabilité Booléenne (SAT) est fréquemment utilisé lors de la modélisation d'applications industrielles. À cet effet, les deux dernières décennies ont vu une progression fulgurante des outils conçus pour trouver des solutions à ce problème NP-complet. Deux grandes avenues générales ont été explorées afin de produire ces outils, notamment l'approche logicielle et matérielle.

Afin de raffiner et améliorer ces solveurs, de nombreuses techniques et heuristiques ont été proposées par la communauté de recherche. Le but final de ces outils a été de résoudre des problèmes de taille industrielle, ce qui a été plus ou moins accompli par les solveurs de nature logicielle. Initialement, le but de l'utilisation du matériel reconfigurable a été de produire des solveurs pouvant trouver des solutions plus rapidement que leurs homologues logiciels. Cependant, le niveau de sophistication de ces derniers a augmenté de telle manière qu'ils restent le meilleur choix pour résoudre SAT. Toutefois, les solveurs modernes logiciels n'arrivent toujours pas a trouver des solutions de manière efficace à certaines instances SAT.

Le but principal de ce mémoire est d'explorer la résolution du problème SAT dans le contexte du matériel reconfigurable en vue de caractériser les ingrédients nécessaires d'un solveur SAT efficace qui puise sa puissance de calcul dans le parallélisme conféré par une plateforme FPGA. Le prototype parallèle implémenté dans ce travail est capable de se mesurer, en termes de vitesse d'exécution à d'autres solveurs (matériels et logiciels), et ce sans utiliser aucune heuristique. Nous montrons donc que notre approche matérielle présente une option prometteuse vers la résolution d'instances industrielles larges qui sont difficilement abordées par une approche logicielle.

Mots-clés: SAT, solveur matériel, solveur matériel parallèle sur FPGA

#### **Abstract**

Though very difficult to solve, the Boolean satisfiability problem (SAT) is extensively used to model various real-world applications and problems. Over the past two decades, researchers have tried to provide tools that are used, to a certain degree, to find solutions to the Boolean satisfiability problem. The nature of these tools is broadly divided in software and reconfigurable hardware solvers. In addition, the main algorithms used to solve this problem have also been complemented with heuristics of various levels of sophistication to help overcome some of the NP-hardness of the problem. The end goal of these tools has been to provide solutions to industrial-sized problems of enormous size. Initially, reconfigurable hardware tools provided a promising avenue to accelerating SAT solving over traditional software based solutions. However, the level of sophistication of software solvers overcame their hardware counterparts, which remained limited to smaller problem instances. Even so, modern state-of-the-art software solvers still fail unpredictably on some instances.

The main focus of this thesis is to explore solving SAT on reconfigurable hardware in order to gain an understanding of what would be essential ingredients to add (and discard) to a very efficient hardware SAT solver that obtains its processing power from the raw parallelism of an FPGA platform. The parallel prototype solver that was implemented in this work has been found to be comparable with other hardware and software solvers in terms of execution speed even though no heuristics or other helping techniques were implemented. We thus show that our approach provides a very promising avenue to solving large, industrial SAT instances that might be difficult to handle by software solvers.

**Keywords**: SAT, hardware solver, FPGA parallel SAT solver

## **Table of Contents**

| Chapter 1 – Introduction                                         | l  |

|------------------------------------------------------------------|----|

| 1.1 Software SAT Solvers                                         | 1  |

| 1.2 Reconfigurable Computing and FPGA                            | 2  |

| 1.3 Objectives of the Current Work                               | 4  |

| 1.4 Contributions                                                | 5  |

| 1.5 Organization                                                 | 5  |

| Chapter 2 – The Boolean Satisfiability Problem                   | 6  |

| 2.1 Problem Representation                                       | 6  |

| 2.2 A Variant of the Davis-Putnam Algorithm                      | 8  |

| 2.3 Enhancements over the Basic DP-Variant                       | 10 |

| 2.3.1 Pure Literal Assignment Rule                               | 10 |

| 2.3.2 Non-Chronological Backtracking and Dynamic Clause Addition | 11 |

| 2.3.3 Dynamic Decision Variable Ordering                         | 11 |

| 2.4 Incomplete Algorithms                                        | 12 |

| Chapter 3 – Hardware Architectures for Solving SAT               | 14 |

| 3.1 Some History – The Boolean Analyzer                          | 14 |

| 3.2 Instance Specificity – The First Generation of Solvers       | 16 |

| 3.3 Application Specificity – Software/Hardware Hybrid Solvers   | 22 |

| 3.4 Application Specificity – Modern Solvers                     | 26 |

| 3.5 Summary and Analysis of Hardware SAT Solvers                 | 33 |

| Chapter 4 – The Evaluation Platform                              | 38 |

| 4.1 Introducing a DP-Based Solver                                | 39 |

| 4.2 Encoding a SAT Problem Instance                              | 40 |

| 4.3 Disjunction, Inclusion and Implication – Solving SAT         | 41 |

| 4.4 Solution Space Exploration.                                  | 44 |

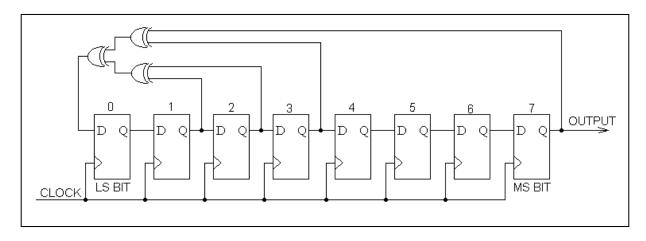

| 4.5 LFSR and Pseudo-randomness in Variable Decision              | 46 |

| 4.6 Some Remarks                                                 | 47 |

| Chapter 5 – Experimental Results                                 | 48 |

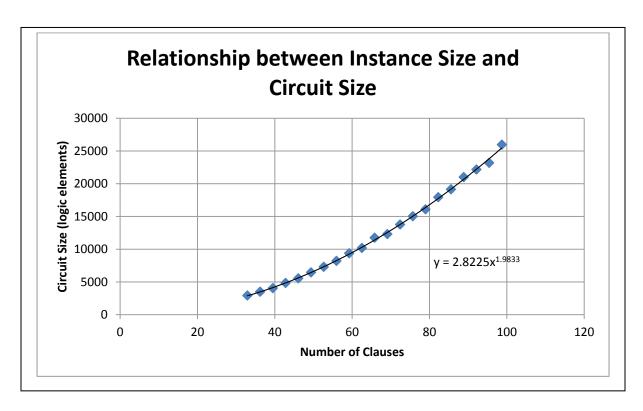

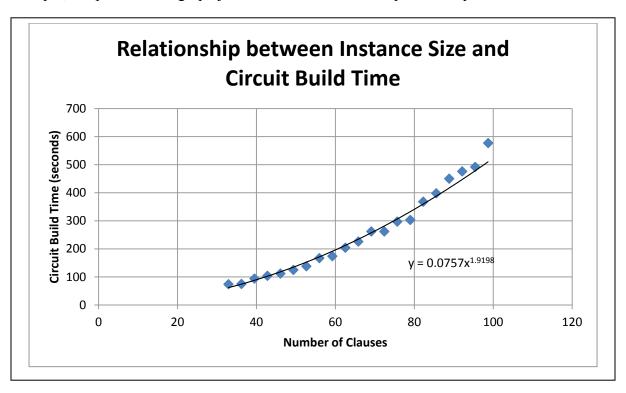

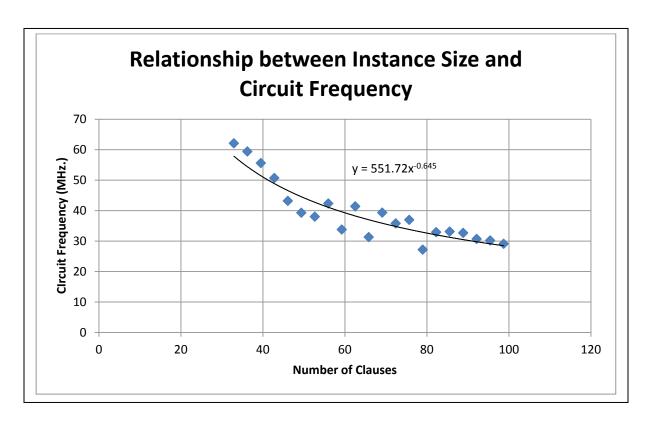

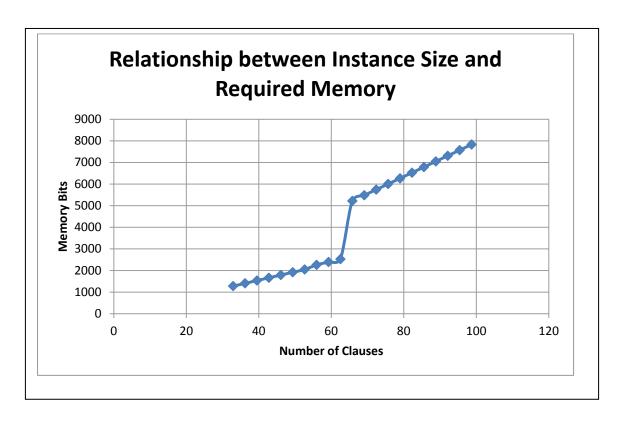

| 5.1 Regression Analysis – Rules of Thumb                         | 50 |

| 5.2 Comparison between Hardware and Software                   | 54 |

|----------------------------------------------------------------|----|

| 5.3 Comparison with other Solvers                              | 56 |

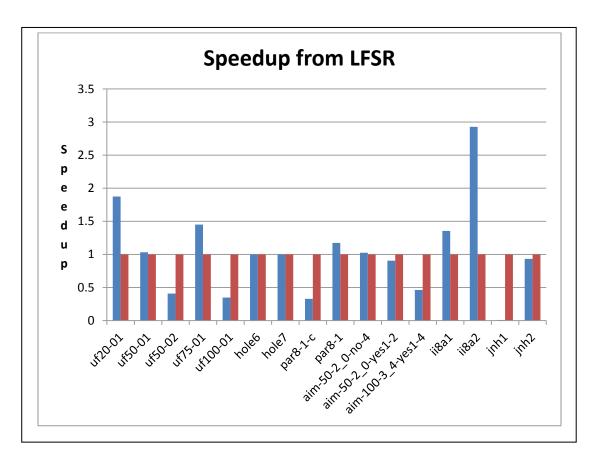

| 5.4 Effect of Pseudo-Randomness on SAT Resolution              | 59 |

| 5.5 Computing All Implications in One Clock Cycle              | 61 |

| Chapter 6 – Conclusion and Future Work                         | 64 |

| 6.1 A Review of Our Contributions                              | 65 |

| 6.2 Future directions – Eliminating Memory Altogether and More | 66 |

## **List of Tables**

| Table 1: Summary of hardware SAT solvers                                             | 35 |

|--------------------------------------------------------------------------------------|----|

| Table 2: Characteristics of circuits used in the regression analysis                 | 50 |

| Table 3: Comparison between HW and SW versions of our DP-like solver                 | 56 |

| Table 4: Comparison of HW version of our solver with other HW solvers                | 57 |

| Table 5: Run-time comparison of HW version of our solver with MiniSAT                | 58 |

| Table 6: Comparison of HW version of our solver with other HW solvers cont'd         | 58 |

| Table 7: Comparison between binary and LFSR decision modes (clock cycle counts)      | 59 |

| Table 8: Improvement in performance by calculating all implications in 1 clock cycle | 62 |

## **List of Figures**

| Figure 1: Basic FPGA design flow [12]                                                    | 3  |

|------------------------------------------------------------------------------------------|----|

| Figure 2: A 5-clause 7-variable formula                                                  | 7  |

| Figure 3: Representation of a Boolean formula φ                                          | 7  |

| Figure 4: Pseudo-code of a DP-like algorithm                                             | 8  |

| Figure 5: GSAT incomplete SAT algorithm [1]                                              | 12 |

| Figure 6: WSAT incomplete SAT algorithm [1]                                              | 13 |

| Figure 7: Logical designs of the BA and of its processing register [3]                   | 15 |

| Figure 8: Suyama et al. flow of logic circuit synthesis [9]                              | 16 |

| Figure 9: Zhong et al. hardware SAT solver architectures [15], [21]                      | 18 |

| Figure 10: Platzner et al. FSM-based architecture [8]                                    | 19 |

| Figure 11: High-level view the architectures proposed by Abramovici et al. [2], [22]     | 21 |

| Figure 12: Dandalis et al. SAT deduction engine and clause module details (bottom) [14]  | 23 |

| Figure 13: Leong et al. GSAT hardware implementation [4]                                 | 24 |

| Figure 14: Datapath of Leong et al. WSAT core [16]                                       | 25 |

| Figure 15: Configuware/Software SAT solver proposed by Sousa et al. [5]                  | 26 |

| Figure 16: Sousa et al. clause pipeline [5]                                              | 27 |

| Figure 17: Skliarova and Ferrari's matrix based solver architecture [13]                 | 28 |

| Figure 18: Safar et al. SAT solver architecture [7]                                      | 29 |

| Figure 19: Safar et al. 5-stage pipelined solver [6]                                     | 30 |

| Figure 20: Gulati et al. solver architecture (top) and decision engine FSM (bottom) [11] | 31 |

| Figure 21: Kanazawa and Maruyama WSAT based solver [10]                                  | 32 |

| Figure 22: DNF of formula φ                                                              | 38 |

| Figure 23: High-level model of a DP-based SAT solver                                     | 39 |

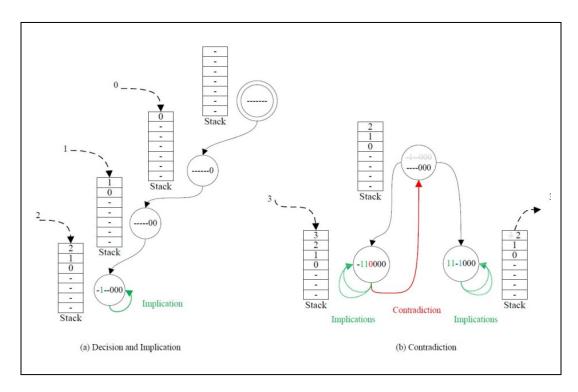

| Figure 24: Operation of DP-like solver                                                   | 45 |

| Figure 25: Example of an 8-bit LFSR                                                      | 46 |

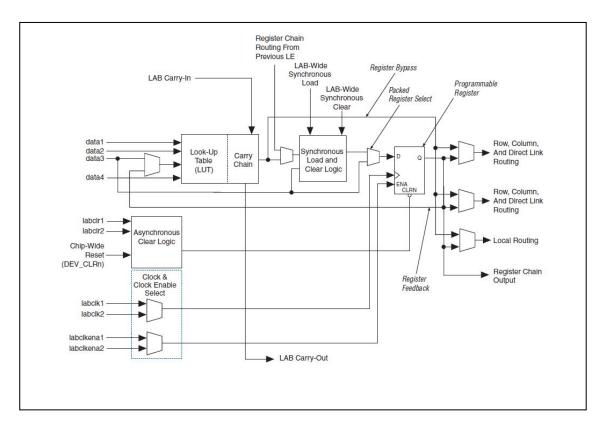

| Figure 26: Cyclone II logic element                                                      | 49 |

| Figure 27: Relationship between an instance's size and its associated circuit size       | 52 |

| Figure 28: Relationship between an instance's size and its associated circuit build time | 53 |

| Figure 29: Relationship between an instance's size and its associated circuit frequency  | 54 |

| Figure 30: Memory requirements (ROM and stack) of the DP-like solver           | 55 |

|--------------------------------------------------------------------------------|----|

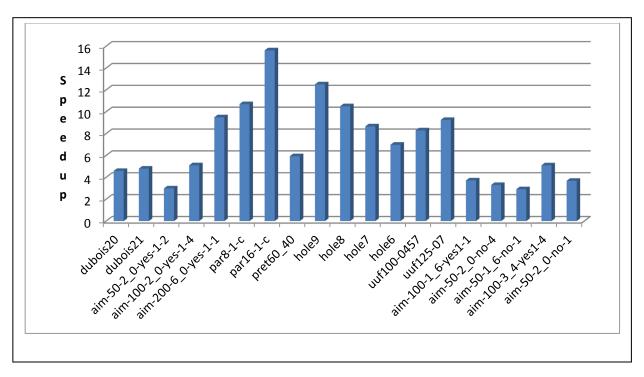

| Figure 31: Speedup obtained from using LFSR in variable decision assignments   | 60 |

| Figure 32: Speedup obtained from computing all implications in one clock cycle | 63 |

#### **List of Abbreviations**

ALU Arithmetic and Logical Unit

ASIC Application Specific Integrated Circuit

BA Boolean Analyzer

BCP Boolean Constraint Propagation

CAD Computer aided design

CDCL Conflict-driven-clause-learning

CNF Conjunctive normal form

DIMACS Centre for Discrete Mathematics and Theoretical Computer Science

DNF Disjunctive Normal Form

DP Davis-Putnam

FPGA Field programmable gate array

FSM Finite State Machine

HDL Hardware Description Language

I/O Input-Output

IC Integrated circuit

LE Logic Element

LFSR Linear Feedback Shift Register

LUT Look-up table

MB Megabytes

MHz Megahertz

MOM Maximum Occurrences in Clauses of Minimum Size

OPB On-chip Peripheral Bus

PLB Processor Local Bus

RAM Random Access Memory

ROM Read-only memory

SAT Boolean satisfiability problem

UPT Average time to resolve implications or detect a conflict

VHDL Very High Speed Integrated Circuit Hardware Description Language

## $\vec{A}$ Yaroslava Chtompel

## Acknowledgments

I would like to express my profound gratitude to Professor El Mostapha Aboulhamid for enabling me to pursue my studies in his laboratory where I have gained a great deal of technical and other knowledge in these past few years. I would also like to take this opportunity to thank my family, and in particular my wife Yaroslava, for their support, help and encouragement, without which I would surely not have been able to finish my work.

## **Chapter 1 – Introduction**

The Boolean Satisfiability problem (SAT) is considered to be fundamental in the field of computation. As SAT is NP-complete [26], it is computationally intractable as there exists no known polynomial time algorithm capable of solving problem instances with 3 or more variables per clause (unlike instances with 2 variables in each clause [27]). It should also be noted that SAT's importance is further highlighted by the fact that it was discovered to be at the core of the study of the NP-completeness of computational complexity theory. For example, Richard Karp showed [28] that there exists a polynomial time many-one reduction from SAT to 21 combinatorial and graph computation problems (e.g. KNAPSACK, EXACT\_COVER) thereby implying that these problems are NP-complete as well.

From an applied standpoint, SAT is used to model various real-life problems and applications such as automated reasoning, computer aided design (CAD), computer-aided manufacturing, machine vision, robotics, integrated circuit (IC) design and computer architecture design [29] despite its computational hardness. In addition, SAT has also been known to play a role in a great variety of decision and optimization problems which can be thought of as its extensions. Indeed, these problems either use SAT as a core problem solving engine or employ some of its various techniques and methods. Examples of such problems include the Satisfiability Modulo Theories, pseudo-Boolean constraints, maximum satisfiability, model counting and Quantified-Boolean Formulas [30].

#### 1.1 Software SAT Solvers

The tools used to provide solutions to SAT instances are mainly software-based. The past two decades have seen a vertiginous improvement in the ability of these solvers. One of the main driving forces behind the advancement of these SAT solvers has been the SAT Solver Competition [31], a recurring event that is geared toward the objective evaluation of the current progress of state-of-the-art SAT solving techniques. Examples of such successful solvers include GRASP [32], CHAFF [33] and MiniSAT<sup>1</sup>. There exists a multitude of features

<sup>1</sup> Solver site: http://minisat.se

fundamental to the efficiency and fast execution speed of these tools, the four main of which are conflict-driven clause learning (CDCL), random search restarts, Boolean constraint propagation (BCP) by use of lazy data structures and conflict-based adaptive branching [34]. To further challenge the limits of SAT solving, researchers have continued to discover and implement additional performance enhancing techniques such as random restart strategies and conflict clause minimization. These methods have augmented the level of sophistication and complexity of modern SAT solvers. However, it should be noted that despite this rapid advancement there is still some ambiguity in the research community as to the relative usefulness and interactions of all these features as well as to the reasons why software SAT solvers fail to generate solutions on many problem instances [34].

#### 1.2 Reconfigurable Computing and FPGA

Alternatively to software-based solutions, SAT may be analyzed by means of reconfigurable hardware using field programmable gate arrays (FPGAs). Indeed, in the past decade, reconfigurable computing based on FPGA devices has matured into a stable discipline that has provided solutions to computing problems that feature substantial advantages over those offered by traditional multi-purpose processors. In addition to the fact that FPGA devices offer increased flexibility as they can be reconfigured, they are also able to generate, by means of their extensive parallelism, very fast application execution times. It is not uncommon to see accelerations of several orders of magnitude over general purpose processors even though circuit clock speeds are orders of magnitude lower [35]. Other added benefits of reconfigurable devices are their low power consumption and reduced energy (each application's circuitry is optimized for the problem at hand) as well as reduction in component count and size, improved time-to-market and upgradeability [35].

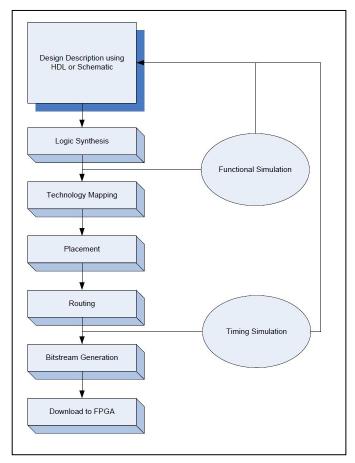

A general overview [12] of the basic FPGA design methodology is illustrated in Figure 1. Initially, a designer will describe the circuit hardware using either a hardware description language (HDL) or a schematic editor. Next, logic synthesis deals with the generation of a netlist of logic gates and other blocks present in FPGA devices that is independent of the intended FPGA technology. At this point, the designer can make use of a functional simulation tool to ensure of the logical correctness of the circuit. Following logic synthesis, the

Figure 1: Basic FPGA design flow [12]

previously obtained generic netlist is used to obtain a specialized circuit of look-up tables (LUTs) as it is mapped towards a specific FPGA LUT-based architecture. This process attempts to minimize the FPGA area, the circuit delay and the power consumption as much as possible [36]. During the placement step, physical resources of the FPGA device are selected for the specialized netlist by means of an optimal strategy. Placement is extremely important for maximal circuit frequency and power consumption as it directly influences a circuit's routability [37]. The next step of the design methodology is routing, a difficult process as it is limited to the particular FPGA device's resources such as wires, programmable switches and multiplexers [12]. Finally, before allowing a CAD tool to generate the bitstream necessary to program the FPGA, a timing simulation may be performed to ensure that circuit timing constraints are met. Of course, as errors and bugs are discovered during simulations, the designer may review the circuit's schematic or HDL code in order to correct them.

#### 1.3 Objectives of the Current Work

The Boolean satisfiability problem is inherently massively parallel. As detailed below, verifying that a particular problem clause is satisfied can be done independently of the verification of all other remaining clauses with the only limiting factor being the number of evaluation units available. As such, it is natural to assume that SAT would map very well to FPGAs given their ability to perform many computations in parallel. However, an FPGA board has several limitations and restrictions that impact the amount of parallelism extracted when mapping a problem. Examples of this include the amount of on and off-chip memories that are available, the maximal frequencies at which reading from these memories is possible as well as their number of physical read ports. Thus, one of our principal objectives has been to explore and evaluate the impact of FPGA on-chip memory on SAT resolution as well as the different trade-offs necessary to garner maximal parallelism for execution speed. To characterize these issues, a solver prototype was implemented using VHDL and targeted to an Altera Cyclone II DE2-70 FPGA board. In addition, a software counterpart with an identical execution model was also developed and used to simulate the hardware on problem instances.

As SAT instances come in many shapes and sizes, a focus of the current work has been to allow for many of them to be analyzed easily. Therefore, a secondary objective of this work has been to take advantage of the reconfigurability of the FPGA device so as to create hardware that is specialized (in terms of the size of the resulting circuit) to the problem at hand. This also allows for simpler, tailored solutions that avoid complex control and other structures and whose theoretical limitations are imposed not by the solver's design but by FPGA capacity.

Finally, an important objective of our work has been to identify, explore and evaluate suitable parallelization techniques applicable to the Boolean satisfiability problem. In particular, the methodology used in the experimental section of this work rests heavily upon evaluating potential solutions in one clock cycle. In addition, one of our goals in developing this prototype was to identify bottlenecks and other problem areas in order to propose a solution that would pave the way towards the development of a mature, efficient solver capable of tackling industrial-size instances comprising millions of variables and clauses.

#### 1.4 Contributions

This work has brought forth four main contributions which are listed below.

- One of the most important contributions of this work is the exploration of the various techniques and methods that can be applied when solving SAT on FPGA.

- A testing platform composed of an HDL synthesizable model and a Java software simulator of a hardware SAT prototype relying solely on FPGA parallelism for execution speed was built and characterized.

- Trouble areas that restrict the use of FPGAs in SAT solving have been identified. Examples of these limitations include the limited size of on-chip memory as well as the use of registers (which effectively play the role of a multi-port random access memory (RAM) but claim a large amount of hardware resources).

- We quantify our technique by means of simulation using problems from the DIMACS<sup>2</sup> set and present comparisons with results available from other state-of-the art hardware and software solvers.

#### 1.5 Organization

This thesis is organized as follows. Chapter 1 has offered an introduction to the Boolean Satisfiability problem as well as to reconfigurable computing and FPGAs. The objectives, contributions and organization of this thesis were also presented. Chapter 2 will describe the Boolean Satisfiability problem, the Davis-Putnam-like (DP-like) algorithm used in this work as well as some of its possible enhancements. Chapter 3 presents the various hardware architectures that are employed in solving SAT, beginning with an older Boolean Analyzer (BA) machine and ending with fairly recent hardware solvers. A summary of these tools is presented at the end of the chapter. Chapter 4 will detail the testing platform created to assess our solver prototype and Chapter 5 will present the experimental results obtained during the testing phase. The work will conclude with Chapter 6 as a discussion and future research directions are given.

5

<sup>&</sup>lt;sup>2</sup> Obtained from http://www.cs.ubc.ca/~hoos/SATLIB/benchm.html

## **Chapter 2 – The Boolean Satisfiability Problem**

The Boolean Satisfiability problem is one of determining whether or not a given Boolean formula  $\varphi$  can evaluate to true. As stated beforehand, SAT is an NP-complete problem as the fastest known algorithms that can solve it require an asymptotically exponential amount of time in the size of  $\varphi$  to either find a solution or to assert that no solution exists. In addition, it is almost impossible to claim that faster algorithms exist although nobody has yet proven the contrary [38].

When considering an formula  $\phi$  of a SAT instance in conjunctive normal form (CNF), one must take into account three components or sets [29]:

- A set of variables  $x_0, x_1, ..., x_n$ , where n is the number of variables of  $\varphi$ .

- A set of literals. A literal is an appearance of variable x as either itself or its negation  $\overline{x}$  (for example  $x_1$  and  $\overline{x_1}$  are the two possible literals of variable  $x_1$ ).

- A set of m distinct clauses:

- Each clause consists of disjunctions of literals combined with the or (V) logical connective.

- ο The whole Boolean formula  $\varphi$  consists of conjunctions of clauses combined with the and (Λ) logical connective.

To satisfy the Boolean formula  $\varphi$  is to determine if a variable assignment exists such that the conjunctive normal form of  $\varphi$  evaluates to true. Figure 2 below illustrates an example<sup>3</sup> of a Boolean formula  $\varphi$  featuring 5 clauses (represented by  $\gamma_-$ ) and 7 variables. This example will also be used in subsequent chapters for illustrative purposes.

#### 2.1 Problem Representation

SAT is usually expressed in conjunctive normal form. However, an equivalent way of expressing SAT is the disjunctive normal form (DNF). By using De Morgan's law<sup>4</sup> of duality,

6

<sup>&</sup>lt;sup>3</sup> Example borrowed and adapted from: http://www.cs.cmu.edu/~mtschant/15414-f07/lectures/grasp-ex.pdf

<sup>&</sup>lt;sup>4</sup> http://en.wikipedia.org/wiki/De Morgan's laws

one can easily obtain one form from the other by simply inverting all literal polarities ( $\overline{x}$  becomes x and vice-versa) and by replacing all V logical connectives with  $\Lambda$  logical connectives. In this manner,  $\overline{\phi}$  is obtained from  $\phi$ .

A variable is represented in a clause by a literal which can be either false or true. A variable can also not have any influence on a clause because neither of its literals is present. For example, clause  $\gamma_2$  in Figure 2 has two literals which are true ( $x_2$  and  $x_5$ ) whereas all other variables are absent. To represent problem clauses, three variable states are needed: present as true, present as false and not present. Thus, 2 bits are required to express this information: "10", "01" and "11". The "00" state is not necessary and therefore it is not used. Figure 3 illustrates this encoding on the previous 5 clauses of formula  $\varphi$ . The matrix is read from right to left and from top to bottom. Each row represents a clause and each column represents a variable. For example, the first row of Figure 3 represents the first clause,  $\gamma_0$ , and

$$\begin{cases}

\gamma_{0} = (x_{4} \lor x_{3} \lor x_{1} \lor x_{0}) \\

\gamma_{1} = (\overline{x_{4}} \lor x_{3} \lor x_{1} \lor x_{0}) \\

\gamma_{2} = (x_{5} \lor x_{2}) \\

\gamma_{3} = (x_{6} \lor \overline{x_{3}} \lor x_{0}) \\

\gamma_{4} = (\overline{x_{6}} \lor \overline{x_{3}} \lor x_{1})

\end{cases}$$

$$\varphi(x_{0}, x_{1}, x_{2}, x_{3}, x_{4}, x_{5}, x_{6}) = \gamma_{4} \land \gamma_{3} \land \gamma_{2} \land \gamma_{1} \land \gamma_{0}$$

Figure 2: A 5-clause 7-variable formula

```

("10")

("10")

("11")

("10")

("11")

("10")

("11")

("01")

("10")

("10")

("10")

("10")

("11")

("11")

("11")

("11")

("11")

("11")

("11")

("01")

("11")

("01")

("11")

("10")

("11")_{-}

```

Figure 3: Representation of a Boolean formula φ

the rightmost column displays literal information for variable  $x_0$ .

#### 2.2 A Variant of the Davis-Putnam Algorithm

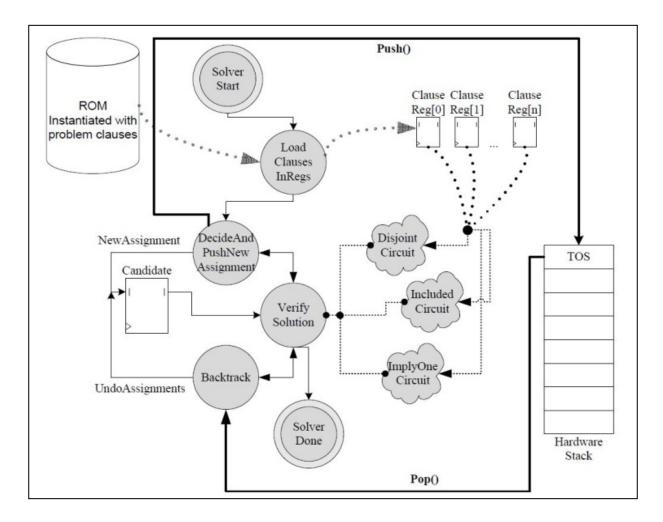

The method used in this work to solve SAT is based on the classical Davis-Putnam algorithm [39]. This resolution-based, backtracking procedure is described by the pseudo-code of Figure 4. The procedure uses a two-dimensional vector termed the Candidate that uses the 3-state encoding scheme discussed above. A stack (last-in-first-out data structure) is also required for backtracking purposes whenever erroneous assignments are made. Lines 4 - 9 represent the initialization section. At line 4, the Candidate is initialized as all its variable positions are assigned "11" to represent the fact that they are free. Lines 5 and 6 show that the stack is

```

1: Procedure DP-Variant

2: Input: A set of clauses \Gamma, a set of variables \Psi

3: Output: SAT if all clauses of \Gamma evaluate to true, UNSAT otherwise

4: Candidate ← all variables free;

5: Stack ← empty;

6: TOS \leftarrow -1; // top of the stack

7: \upsilon \leftarrow -1:

8: Candidate(0) \leftarrow '0';

9: Stack.push(0);

10: while(true)

11: if SAT(\Gamma) then

12: return SAT;

13: else if CONTRADICTION(\Gamma) then

14: if Stack.empty then

return UNSAT:

15:

16: else

17:

TOS \leftarrow Stack.pop;

RESET_ASSIGNS(Candidate, TOS);

18:

Candidate(TOS) \leftarrow '1';

20: else if ONE_IMPLICATION(Candidate) then

21: ASSIGN_IMPLICATION(Candidate);

22: else

23: \upsilon \leftarrow \text{NEXT\_FREE\_VAR}(\text{Candidate}, \Psi);

24: Candidate(\upsilon) \leftarrow '0';

25: Stack.push(υ);

26: end if;

27: end while:

```

Figure 4: Pseudo-code of a DP-like algorithm

initially empty and the top of the stack (TOS) is initialized to -1. At line 7, the temporary variable index v also receives -1 as staring value. Lines 8 and 9 indicate that the procedure starts by first deciding to assign '0' to  $v_0$ . Inside the procedure's only while-loop, there are four main sections.

The first section spans lines 22 - 25. Here new decisions are made regarding the assignment of the current next available free variable (obtained from the auxiliary procedure NEXT\_FREE\_VAR(Candidate,  $\Psi$ )). These variables are termed decision variables and are different from implication variables (described shortly). As soon as the index of the next free variable is determined, it is used as an index into the Candidate vector where '0' is assigned as a first (arbitrary) try. This index is pushed onto the stack so that the procedure can keep track of the decisions it has made.

The second section of the loop is formed by lines 20 and 21. Here the implications of the decisions made in the first section above are determined. As the procedure makes decisions, more and more literals receive assignments in clauses. At a certain point, a clause can become a unit clause when it has only one literal that is yet unassigned in the Candidate and all Candidate its other literals are false. For example, ("11")("11")("01")("01")("01")("01") would cause  $\gamma_0$ ,  $\gamma_1$  and  $\gamma_2$  to become unit as all three clauses have only one remaining literal, namely  $x_4$ ,  $\overline{x_4}$  and  $x_5$  respectively and all their other literals are assigned false. Focusing only on  $\gamma_0$ , the implication of having previously assigned x3 to be false is that variable x4 in the Candidate must be assigned '1' so that the clause is satisfied. This assignment is carried out by the auxiliary function ASSIGN\_IMPLICATION(Candidate). This section implements the unit clause rule (also called BCP) which is an important feature that helps to augment the resolution of partial solutions so that the search space is pruned. Moreover, it is important to note that index 4 is not pushed onto the stack as  $x_4$  is an implied variable and not a decision variable.

The next section spans lines 13 - 19. Contradictions are found by the CONTRADICTION( $\Gamma$ ) auxiliary procedure. These arise when the function has found one clause to be false as all its literals evaluate to false. Continuing with the partial Candidate solution ("11")("11")("01")("01")("01")("01") from above after implying variable  $x_4$

to '1' we find that  $\gamma_1$  is now false. Inside this third section, at line 17 the stack is popped and the TOS receives the index of the last decision variable which in this case is 3. All assignments beyond this point (including the offending assignment on  $x_4$ ) are reset by RESET\_ASSIGNS(Candidate, TOS). Since '0' did not work as a decision on  $x_3$  '1' is now tried. Index 3 is not pushed onto the stack this time because both possibilities have been exhausted for variable  $x_3$ . Line 14 determines if the problem is unsatisfiable. As the DP-Variant procedure proceeds through the problem's search space, it will examine both possibilities for all decision variables. As both these possibilities are unsatisfactory, the procedure backtracks to earlier and earlier decisions. If all decision variables have been tried in both polarities unsuccessfully, the stack will be empty. This means that no matter what decisions are made on any decision variable, it is impossible to satisfy all clauses and the problem is unsatisfiable.

The last section includes lines 11 and 12 where the SAT( $\Gamma$ ) auxiliary procedure is invoked to determine if all clauses have been satisfied. If all clauses are true or satisfied, the DP-Variant procedure terminates with satisfiable (SAT) as answer. If at least one clause is not yet satisfied SAT( $\Gamma$ ) returns false. A clause can be unsatisfied in two cases. In the first, it can be neither false nor true as not all of its variables have yet received an assignment (considering the example of Figure 2, this situation would arise for clause  $\gamma_0$  after only  $x_0$  and  $x_1$  would receive "01" or false as assignments; the clause still requires more assignments to be resolved). In the second case, the clause is false because all of its variables evaluate to false. For example, Candidate ("11")("01")("11")("01")("01")("11")("11") would render clause  $\gamma_2$  false because  $x_5$  and  $x_2$  are both false.

## 2.3 Enhancements over the Basic DP-Variant

The basic procedure described in the previous section leaves room for improvement by means of several techniques and heuristics that have been proposed by researchers over the years. Some of the more important of these features are described in this section.

#### 2.3.1 Pure Literal Assignment Rule

The pure literal assignment rule consists of examining all literals of clauses that are not yet satisfied and determining if there are any that occur in only one polarity (i.e. either true or

false) in all the problem's clauses. The variable that is associated with this literal can thus be assigned '1' if all literals in the remaining unsatisfied clauses are true or '0' if they are false. This method, paired with the unit clause rule described above, are termed reduction methods as they increase the resolution of the partial solution and permit the simplification of the Boolean formula (by satisfying all clauses in which the variable is present) [40].

#### 2.3.2 Non-Chronological Backtracking and Dynamic Clause Addition

The backtracking that is described higher for the DP-Variant procedure is of a chronological nature. In other words, if a contradiction arises, the procedure pops the stack and uses that index to try a different solution. As long as the contradiction is present, the stack is popped and eventually the offending decision is found and the contradiction is resolved. However, the contradiction may not have been caused by the last decision made. Introduced by Marques-Silva and Sakallah in [32], GRASP is a search algorithm that features a more sophisticated method of backtracking and pruning the search space. An analysis is performed on the clauses involved in contradictions so that the level of the actual decision variable responsible for the erroneous situation is identified. In addition, it is also possible to construct one or more conflict clauses (that are added to the initial Boolean formula) that prevent future repetition of the same conflict.

#### 2.3.3 Dynamic Decision Variable Ordering

The DP-Variant procedure described in this chapter makes use of a simple static method of deciding which variable is picked for the next decision as the next free variable is always selected. However, it is also possible to determine during execution which variable should be chosen so that the maximum number of variable implications are generated in an effort to identify contradictions quickly. In [18], Suyama et al. use two heuristics to improve the execution time of their implementation of the Davis-Putnam procedure. The first is termed Maximum Occurrences in Clauses of Minimum Size (MOM). Simply put, this method attempts to find the variable that occurs in most clauses that have only two unassigned literals. The intuition is that choosing and assigning this variable will create many unit clauses. The second heuristic used to dynamically select decision variables is called Experimental Unit

Propagation (EUP). This technique is computationally more intensive as for each unassigned variable both '0' and '1' are tried in parallel. The variable that gives rise to the most unit clauses is hence selected.

#### 2.4 Incomplete Algorithms

The algorithm presented here is a complete method. In other words, given a SAT instance, the algorithm is always able to either find a solution or report that no solution exists.

SAT can also be solved by a different approach. An incomplete SAT solving algorithm is one that can find a satisfying assignment but can never declare the instance unsatisfiable. Unlike the DP-Variant procedure whose main approach is exhaustive branching (decision variables) and backtracking, incomplete algorithms most often use stochastic local search. These algorithms are greatly superior than DP-based approaches on some problem instances [1]. Two of the most important incomplete algorithms that have been highly successful in solving SAT by using local search are GSAT [41] and WSAT (or Walksat) [42].

GSAT, whose algorithm is given in Figure 5, initially begins with a random truth assignment for all variables. It then tries to greedily flip variable assignments that would create the greatest decline in the number of unsatisfied clauses. This is repeated either until a solution has been found or until MAX-FLIPS has been reached. The whole procedure is

```

: A CNF formula F

Input

Parameters: Integers MAX-FLIPS, MAX-TRIES

: A satisfying assignment for F, or FAIL

Output

begin

for i \leftarrow 1 to MAX-TRIES do

\sigma \leftarrow a randomly generated truth assignment for F

for j \leftarrow 1 to MAX-FLIPS do

if \sigma satisfies F then return \sigma

// success

v \leftarrow a variable flipping which results in the greatest decrease

(possibly negative) in the number of unsatisfied clauses

Flip v in \sigma

return FAIL

// no satisfying assignment found

end

```

Figure 5: GSAT incomplete SAT algorithm [1]

repeated MAX-TRIES times [1].

WSAT, shown in Figure 6, further focuses the search by looking in unsatisfied clauses when selecting the variable to flip (the clause from which this variable is chosen is also selected randomly). The "freebie move" is performed when the algorithm finds a variable whose flipping does not cause any currently satisfied clauses to become unsatisfied. If no such variable exists, with a predetermined probability, a random literal is flipped in the randomly chosen unsatisfied clause and with the remaining probability a variable in this same clause is flipped in such a way that the "breakout count", or the number of currently satisfied clauses that become unsatisfied, is minimized. The parameter p which controls the frequency of nongreedy moves has been empirically found, for various related problem instances, to sometimes have an optimal value. For example, for random 3-SAT formulas, this parameter should be set to 0.57.

```

Input

: A CNF formula F

Parameters: Integers MAX-FLIPS, MAX-TRIES; noise parameter p \in [0, 1]

: A satisfying assignment for F, or FAIL

Output

begin

for i \leftarrow 1 to max-tries do

\sigma \leftarrow a randomly generated truth assignment for F

for j \leftarrow 1 to max-flips do

if \sigma satisfies F then return \sigma

// success

C \leftarrow an unsatisfied clause of F chosen at random

if \exists \ variable \ x \in C \ with \ break-count = 0 \ then

// freebie move

else

With probability p:

// random walk move

v \leftarrow a variable in C chosen at random

With probability 1 - p:

// greedy move

v \leftarrow a variable in C with the smallest break-count

Flip v in \sigma

return FAIL

// no satisfying assignment found

end

```

Figure 6: WSAT incomplete SAT algorithm [1]

### **Chapter 3 – Hardware Architectures for Solving SAT**

Generally, there have been two kinds of architectures that have been explored by researchers when implementing hardware SAT solvers, namely instance-specific and application-specific approaches. Instance-specific solvers have their circuits specialized for the problem at hand and thus need to be recompiled or reconfigured before every execution. Application-specific solvers feature a more general construction and can solve all SAT instances without needing to be recompiled. There are benefits and caveats to both these approaches such as long compilation times for the former and access to memory for the latter. A very comprehensive review focusing on detailed architectural aspects as well as on programming models is presented by Skliarova and Ferrari in their 2004 work [40]. There seems to have been a gradual shift towards instance specificity from application specificity. This chapter will therefore take a historical approach at presenting relevant previous works.

#### 3.1 Some History – The Boolean Analyzer

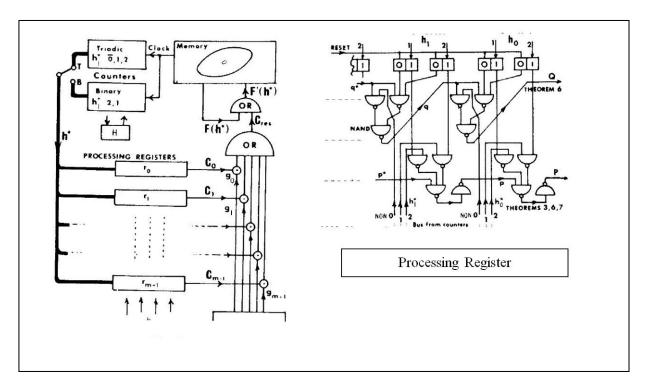

Perhaps one of the earliest attempts at utilizing specialized hardware to treat Boolean equations and formulas was undertaken in 1968 by Antonin Svoboda as he proposed a Boolean Analyzer (BA) [3] capable of producing all the prime implicants of a Boolean formula given the Disjunctive Normal Form (DNF) of its complement. Svoboda's main goal in building the BA was to achieve accelerations over the then fastest general purpose computers which displayed execution times much longer than acceptable. The author identifies some the factors responsible for BA accelerations as being the parallel processing of a large number of Boolean terms and the reduction of Boolean information processing to a repetition of the same operation whose result is only a single bit of information. In order to parallelize the design and achieve accelerations considering the factors mentioned above, the author makes use of triadic and binary counters, a main memory where information for each term is stored, logic gate control and special processing registers that are able to evaluate Boolean terms in parallel. Figure 7 shows the logical organizations of the BA (left) and of the processing register (right). Essentially, the BA uses the triadic counter to generate all 3<sup>n</sup> possible candidate solutions for a Boolean function  $\overline{y}$  of n variables. This triadic counter is necessary to express the three possible states that a variable can find itself in in a given

Figure 7: Logical designs of the BA and of its processing register [3]

minterm: assigned true, assigned false or not present. For example, consider the following 4-variable Boolean formula  $\overline{y}$  taken from Svoboda's 1968 work [3]:

$$\overline{y} = \ x_2 \ \overline{x}_1 \ \overline{x}_0 \ + \ \overline{x}_2 \ x_1$$

There are two minterms which are encoded using a ternary scheme as follows: 0122 and 0210. To represent the fact that the variable is not present (for example,  $x_3$  does not appear anywhere in the formula) 0 is used. If the variable is present as itself (for example  $x_2$  in the first minterm), 1 is used. Finally, if the variable is present in its negated form ( $\overline{x}_0$  in the first minterm) 2 is used. Therefore, in order to be able to represent these 3 states, 2 bits are needed.

Candidates are checked against the terms of  $\overline{y}$  to find disjunction points. If a candidate solution is disjoint from all terms of  $\overline{y}$  it is not included in it but is included in y. The memory is used to store intermediate and final results for each candidate examined. The binary counter is used by the BA during its solving of Boolean equations (not shown here).

The BA is attempting to solve a very difficult problem which is harder than SAT and as such is unsuitable for tackling any SAT instances modeling real-life applications whose sizes sometimes exceed millions of variables. Because the BA is examining all possible terms

of a Boolean formula as opposed to all possible minterms, its search space is composed of  $3^n$  possibilities instead of  $2^n$ . The universe of possible solutions is explored in a brute-force manner and therefore has a time complexity which is exponential. In addition, there is also an explosion in the amount of memory resources needed as they also grow in exponentially.

#### 3.2 Instance Specificity – The First Generation of Solvers

By their nature, FPGAs offer great flexibility. As SAT instances can vary greatly in their size and complexity, it was natural for researchers to initially explore an instance-specific approach when creating SAT solvers whose logic circuit was uniquely tailored after the problem at hand. In this manner, the various variable and clause relationships were imbibed into a specialized circuit that was built each time to solve one instance.

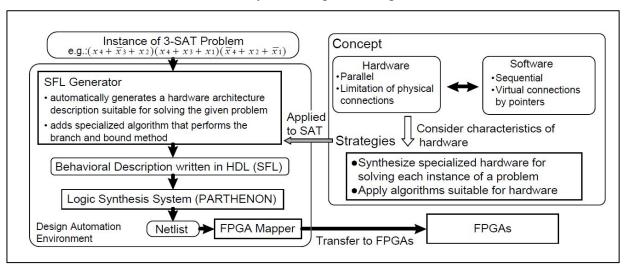

Amid successful early efforts exploring the applicability of FPGAs to SAT solving, Suyama et al. suggested an instance specific approach [19], [9], [17], [18] that is capable of finding all or a fixed number of solutions to a SAT instance. The method is complete as the solver is capable of determining if at least one solution exists. The authors' design flow (Figure 8) entails initially having a C program examining a file containing the description of a SAT instance and generating a high-level HDL behavioral description of the problem at hand. The logic circuit thus described is subsequently analyzed, synthesized and mapped by a CAD tool. In order to increase the efficiency of their parallel algorithm, the authors make use of a

Figure 8: Suyama et al. flow of logic circuit synthesis [9]

static variable ordering technique in [19] and two dynamic variable ordering techniques in [9], [17] and [18]. The first of these ordering techniques is termed experimental unit propagation (EUP) and entails assigning both possible values to a variable and verifying these assignments concurrently. The second technique, named maximal occurrences in minimum length clauses (MOM), deals with selecting variables occurring in a maximal number of binary clauses [9]. In addition, the approach is characterized by the avoidance of using memory for backtracking purposes as each variable is assigned a register that records the depth of the search tree where its value was decided. The reason offered for this design choice is that the memory required for a stack can become quite large and sequential memory accesses can introduce undesired latencies and bottlenecks. The authors report an implementation status [18] of the mapping of a SAT instance featuring 200 variables and 320 clauses on 21 FLEX10K250 FPGA chips. However, even though the total logic utilization is about 13%, the resulting circuit requires a large amount of wiring resources and therefore necessitates all 21 FPGAs. The authors also report an FPGA implementation of a 128-variable, 256-clause circuit that was synthesized at 10 MHz.

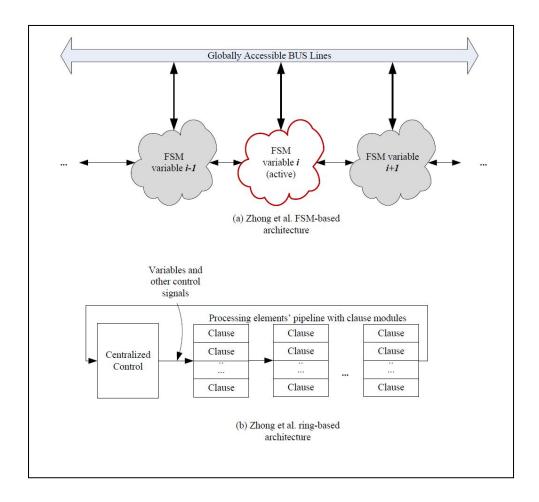

Similarly, Zhong et al. were able to develop a series of instance-specific SAT solver architectures [20], [15], [21] (Figure 9) all based on the DP algorithm [39]. The authors identify implication and conflict checking [15] as the most computation intensive tasks (from a software solution's standpoint) and try to focus their efforts to generating hardware able to accelerate these areas of the basic DP algorithm. The architecture presented in [15] is based on having one finite-state machine (FSM) (Figure 9 top) for each variable keeping track of its state (assigned logical '0', '1' or free). All FSMs are connected in a serial chain and, at any one time, only one FSM is active. If the right-most FSM attempts to pass control to its right, a solution has been found. On the other hand, if the left-most FSM wishes to pass control to its left, the SAT instance has been found to be unsatisfiable. Like Suyama et al., the authors use a C program to generate a VHDL model from the problem's specification. The implication circuit is formula-specific whereas the FSM circuit, since it is identical for all problems, is designed from components that are reused in all circuits. The order of the FSMs on the serial chain is determined statically before execution and variables are sorted depending on the number of their occurrences in the SAT formula. This architecture implies that only one

Figure 9: Zhong et al. hardware SAT solver architectures [15], [21]

variable can receive an assignment at any one time, either due to backtracking, implication or decision. It should be noted that even though the design obviates the need for a backtracking stack, it introduces an unnecessary delay when backtracking as the solver backtracks not to the most recently decided variable but to the variable immediately to the left of the currently active FSM. The key drawbacks of the work presented in [15] are a low clock frequency of 0.7 – 2.0 MHz as well as very long compilation times of up to several hours on their Sun 5 machine featuring 110 MHz and 64 MB of RAM. In [20], non-chronological backtracking is used to further enhance the acceleration that is obtained over the software solution (GRASP solver). In order to resolve the low clock frequencies and high compilation times, Zhong et al. altered the architecture of their solver to a regular ring-based interconnect [21] with centralized control (Figure 9, bottom). This new architecture uses repeated clause modules on

a pipelined bus which allows for higher clock speeds of about 30 MHz. However, at any one time, only a subset of the problem's clauses care evaluated in parallel. In addition, compilation times decreased drastically due to incremental synthesis and place-and-route (using Xilinx tools). To this effect, a reusable template for general components is first created. A Java program examines a SAT formula as well as a bitstream file describing this generic template of reusable modules. This is followed by a customization step to generate the appropriate logic function programs and routing connections. The result of this customization can then be downloaded onto the FPGA. The whole process is said to require only a few seconds.

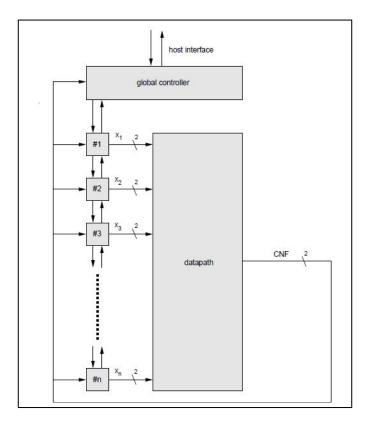

In an approach similar to that proposed by Zhong et al. in [20], Platzner et al. [24], [8] also make use of an array of finite-state machines, each associated with one variable, that are connected in such a manner that an FSM can activate its top or bottom neighbors (Figure 10). A combinational datapath circuit takes variables states as input and computes information that is resupplied to the FSMs. There is a global controller that initiates computations and ensures proper I/O communication. The datapath portion of the circuit and the number of FSMs are

Figure 10: Platzner et al. FSM-based architecture [8]

instance-specific whereas the global controller and FSM structures do not change. At the outset, all variables are unassigned, which leads the datapath to compute its result (CNF line in Figure 10) as unassigned ('X'). In this case, following activation by the global controller, the first FSM (#1) assigns '0' to its variable and verifies the CNF line. If '1' is observed, the partial assignment satisfies the Boolean formula and a solution has been found. On the other hand, if '0' is observed, the variable assignment does not satisfy the Boolean formula and the FSM complements its value and reuses the datapath once again. If 'X' is observed, the partial assignment is neutral and neither satisfies nor unsatisifies the Boolean formula and the FSM activates the FSM below it. If both '0' and '1' assigned to a variable yield a CNF value of '0', control is passed (backtracking) to the FSM above. If the first FSM activates the global controller, the Boolean formula is found to be unsatisfiable. Once again, as was encountered by Zhong et al., the [24] architecture suffers from long compilation times (between 103 and 597 seconds) which dominate the time required to find a solution (e.g. it takes 0.005 seconds to find a solution to problem hole6 of the DIMACS set but 103 seconds to compile the circuit). It should be mentioned that the maximal circuit frequencies for [24] found were found to be between 27 and 65 MHz and therefore somewhat higher than those found by Zhong et al. (for all their architectures reviewed here). As there is no implication computation in [24] the authors use a C simulator program to evaluate enhancing the architecture with this and other features (such as the identification of unassigned variables in satisfied clauses, termed don't care variables) [8]. Simulation results for the architecture performing implication computation show several orders of magnitude speedup over the GRASP software solver although many of the problems tested would not fit onto the FPGA used (XC4020). Finally, physical synthesis results that take into account compilation times showed speedups between 0.03 and 6.54 on the problems from the hole benchmark class against the same GRASP software solver.

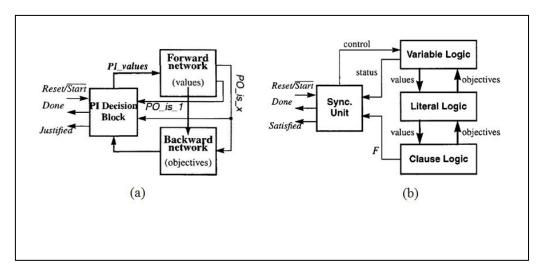

A radically different approach proposed by Abramovici et al. [2], [22] makes use of the PODEM algorithm [43] that is employed in the solving of test generation problems. The central concept of the approach is the objective which is the desired assignment of a value to a signal that is currently unknown. The main goal of the procedure is to assign the value '1' to the primary output of the combinational SAT circuit by finding the appropriate values for primary inputs (variables). For this purpose, a backtracing procedure is used to propagate an

objective along a single path [2] to a primary input so that the objective may be achieved. An important feature of the approach is that primary inputs can be assigned in any desired order and pure literals are identified dynamically. For backtracking purposes, a hardware stack is used and a central control unit is in charge of performing the search process. The method allows for fine grain parallelism as all operations between successive division steps are done in one clock cycle [2]. Figure 11 (a) shows a high-level block diagram of the architecture proposed in [2]. However, the PODEM algorithm requires the propagation of objectives backward in the circuit whereas a hardware circuit always propagates values forward. To solve this issue, the authors use two distinct element models: every gate of the original circuit is mapped into a forward element and a backward element, each belonging to the forward and backward networks respectively. The authors conclude that the approach is hardware intensive as just the forward network alone is almost twice the size of the initial SAT circuit and the complete circuit is about ten times larger. In [22], a revised architecture is proposed (shown Figure 11 (b)). The Variable Logic block transforms (either implications or decisions) objectives into and maintains current variable assignments. These assignments are sent to the Literal Logic block whose job it is to distribute them to the Clause Logic block. The latter block determines clause values, the output of the overall formula and determines all literal objectives which are sent backwards to the Literal Logic block where they are merged with all other objectives (that are arriving for the same variable) into a single objective for a single

Figure 11: High-level view the architectures proposed by Abramovici et al. [2], [22]

variable. As an enhancement over the previous work where only one objective was propagated along a single path, backtracing of all objectives over all possible paths is now done in parallel and several variables are assigned concurrently. In addition, in [22] objectives are propagated with different priorities and unate variables (pure literals) are identified dynamically. It should also be mentioned that the authors propose a partitioning scheme as SAT problems are decomposed into independent sub-problems to be processed in parallel or sequentially [22]. Finally, it appears that this approach is also hardware demanding as a 13-variable, 29-clause, 69-literal circuit ran at 3.5 MHz. and occupied the whole area of a XC6264 FPGA.

#### 3.3 Application Specificity – Software/Hardware Hybrid Solvers

As it became evident that instance-specific approaches resulted in resource-hungry solutions, researchers turned their attention to a different programming model, namely the application-specific paradigm which entails creating a circuit that is compiled once and that is able to treat different SAT instances. These solvers rely on memory modules to store a problem's clauses.

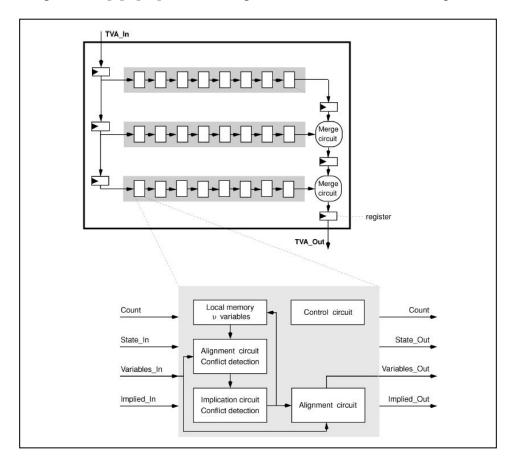

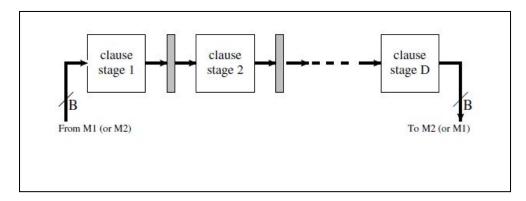

An interesting solver based on dynamic learning and FPGA reconfiguration is presented by Dandalis et al. [23], [14]. This approach is similar to that of Zhong et al. [21] in that it uses chains of pipelined clause modules (Figure 12). A given CNF formula is split into a fixed number of modules (groups of clauses) and thus implications and conflicts are deduced in parallel. Merge units are then used to combine information from the pipelines into a variable set that is consistent. These variables are then fed back to the pipelines until no more implications occur or a conflict has been detected. It is worth noting that only the implication process is executed in hardware with decisions and backtracking done in software. Each clause module has a memory unit that contains each variable's current value (which can be '1', '0', undecided or conflicting). A novel contribution of this work is the fact that the circuit evolves dynamically as it tries to find, by means of previously constructed FPGA template configurations, the minimal time needed to resolve implications or to raise conflicts (UPT). In order to do so, the solver relies on information computed during execution. A greedy heuristic executed by a host computer is used for this purpose. At the beginning, the template having a minimal number of clause modules per group (and thus the highest level of parallelism because more clause pipelines are created) is used to configure the FPGA. The UPT of this

configuration is retained and the host computer decreases the level of parallelism of the next template by increasing the amount of modules per pipeline group. If the newly determined UPT is smaller than the previous minimum, it is retained and reused for the next round of implication and conflict determination. As the host machine reconfigures the FPGA with different templates, the hardware search process does not restart at the root of the search tree but continues from where the previous template had left off. Thus, the optimization process involves finding the level of parallelism that leads to a maximal speedup compared to the baseline solution which uses only one pipeline group for the complete SAT instance. Using a simulator, the authors report, on SAT instances from the DIMACS set, speedups ranging from 1.06 to 5.44 over the baseline solution.

Contrary to the complete nature of the solutions provided by the solvers examined so far, Leong et al. examined not only such a solution in [44] but also turned their attention to incomplete algorithms [4], [16] which can generate solutions but cannot pronounce a SAT

Figure 12: Dandalis et al. SAT deduction engine and clause module details (bottom) [14]

instance unsatisfiable. The work presented in [44] is based on a forward checking tree search method and will not be presented here.

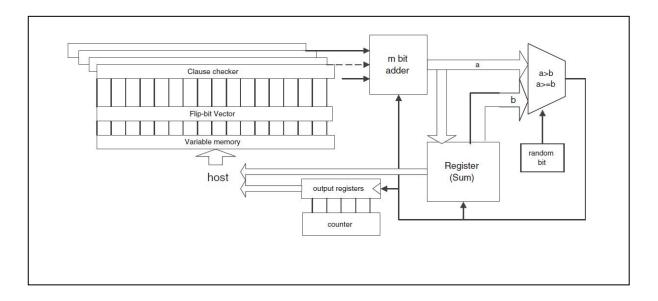

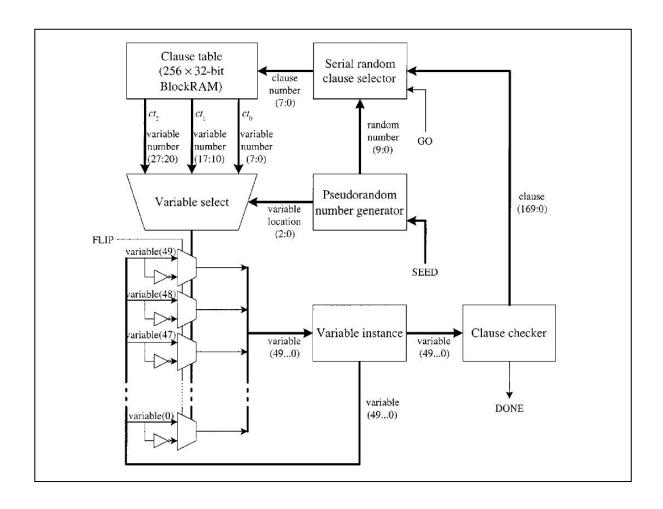

In [4] the incomplete search heuristic GSAT (Figure 5, page 12) was implemented for 3-SAT problem instances (Figure 13). The approach deals with modifying the low-level FPGA configuration bitstream while taking into account the SAT specification. The clause checker in Figure 13 is problem dependent and is customized by a C program according to the SAT instance. Xilinx tools are then used to partially and dynamically reconfigure the FPGA bitstream. The rest of the circuit is generated from a VHDL description and is common to all instances. This eliminates the need for synthesis, mapping, placement and routing of the entire circuit. The inner for-loop of the GSAT algorithm is implemented in hardware whereas the outer for-loop is performed by software. The process starts with a new variable assignment which is downloaded onto the FPGA board. The hardware takes over and, by flipping variables, tries to find the assignment that would create the greatest number of satisfied clauses. If a solution is found, the algorithm terminates. If not, a new random variable assignment is made by software and the process restarts (for a predefined number of times). The solver was tested on a small problem from the aim suite of the DIMACS set but no accelerations were observed when compared to a software implementation of GSAT [4].

Figure 13: Leong et al. GSAT hardware implementation [4]

In [16] Leong et al. addressed the WSAT incomplete algorithm (Figure 6, page 13) and proposed a solver capable of accommodating 3-SAT problems of maximum 50 variables and 170 clauses (Figure 14). As was done for GSAT, the inner loop of WSAT was implemented in hardware and a software host was made to call the GSAT core a predefined number of times with random variable assignments. The clause checker portion of this core also requires configuration at runtime. This method directly manipulates bitstreams to generate FPGA configurations and the usual FPGA synthesis, place-and-route and mapping operations are avoided once again. The results obtained for this solver show accelerations (versus a software implementation of WSAT [16]) on problems from the DIMACS set of 0.1 to 3.3. The core was built to run at 33 MHz.

Figure 14: Datapath of Leong et al. WSAT core [16]

## 3.4 Application Specificity – Modern Solvers

With the work of de Sousa et al. [5], [25] it is possible to see that while hardware SAT solvers still present a hybrid hardware/software approach based on an application-specific programming model, partitioning of the SAT instance into sub-problems starts to become apparent.

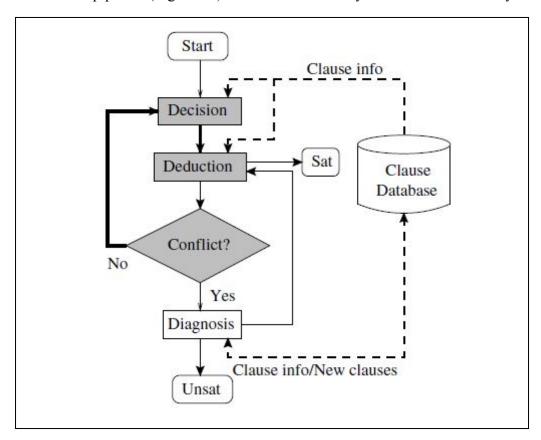

Indeed, de Sousa et al. propose a configurware/software approach (Figure 15). Their SAT solver features dynamic conflict diagnosis and conflict clause identification which are done in software whereas implication computation and identification of decision variables (using heuristics) are done in hardware. When problem instances do not fit completely in hardware, the authors use context switching. They divide the original circuit in pages that are successively loaded with intermediate results from RAM modules. A high-level view of the SAT core is shown in Figure 15. The shaded portions are implemented in hardware. Of note is the use of a clause pipeline (Figure 16) that is architecturally similar to that used by Zhong et

Figure 15: Configuware/Software SAT solver proposed by Sousa et al. [5]

Figure 16: Sousa et al. clause pipeline [5]

al. in [21]. There are several engines that compose the SAT core. The first is the decision engine that, based on a predetermined heuristic, selects one variable for decision. The deduction engine's task is to determine all implications that arise due to a decision by using the unit clause rule and also signals conflicts. If conflicts have been generated, the diagnosis engine analyzes them and constructs a set of offending variables. The variable (belonging to this set) that was assigned most recently is complemented and all implications that arose from it, as well as all subsequent decisions are reset. New implications that were created by the complementation are found and the search continues. In [25], the authors use an XCV2000E FPGA board (97% resource usage) and report that SAT instances of up to 7680 variables and 214304 clauses can be processed. However, the software interface was not yet completed and thus no execution times were reported.

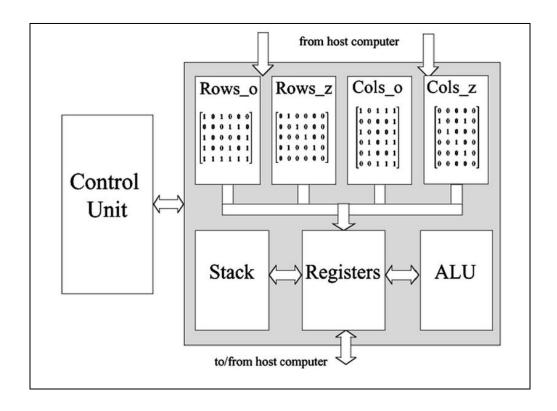

Another prominent example of researchers trying to avoid long hardware compilation times can be seen in the 2004 work of Skliarova and Ferrari [13]. This approach involves using functional units such as registers and arithmetic and logical units (ALUs) to construct a SAT co-processor that avoids being instance-specific (Figure 17). A hardware template circuit based on a ternary matrix that is able to accommodate a SAT sub-problem of a specific size was built. If the sub-problem (appearing at a specific level of the search tree) can fit onto the FPGA, it is downloaded and the aforementioned circuit, implemented on the basis of a DP-like algorithm, is used to solve it. If the sub-problem does not fit, software is used to simplify and reduce it so that it may be downloaded again. Hardware resources are used efficiently in this manner, although the success of instance partitioning between software and hardware is tied to

Figure 17: Skliarova and Ferrari's matrix based solver architecture [13]

the nature of the SAT problem at hand. The authors implemented three different circuit templates, all of different sizes. The largest circuit occupied 54% of the XCV812E FPGA and featured a maximal frequency of 30.516 MHz. Comparisons were made with the GRASP software solver on all instances of the hole suite from the DIMACS benchmark set. Speedups reportedly ranged from 0.289 to 111.245 (considering all three templates). Since it is difficult to correctly ascertain the efficiency of the solver on only one type of problem, other DIMACS instances were used to compare it to GRASP but no significant accelerations were observed. One limiting aspect of the approach is the communication between the software and hardware. As problems become larger and more difficult, more simplifications, reductions, and thus more downloads to the FPGA board are required, which may lead to a decrease in performance.

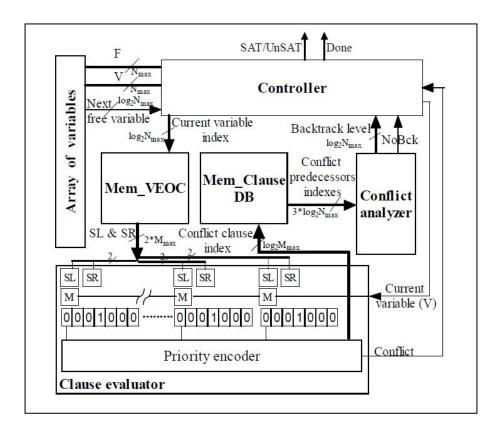

A slightly different SAT solver flavor is presented by Safar et al. [7], [6] as their solution is implemented completely in hardware and avoids instance specificity by storing SAT instance information in RAM modules. In [7], the presented approach is based on

performing a depth first search which is paired up with non-chronological, conflict directed backtracking (Figure 18). In addition, the proposed methodology distinguishes itself by the method employed for clause evaluation as a shift register is used to encode when clauses are satisfied (right shift), unsatisfied (left shift) or there is no impact by the current variable assignment. The authors restrict the range of acceptable problems to 3-SAT and use the "0001000" vector in the shift register-based clause evaluator. A clause thus has two chances to be satisfied and if a '1' is present in the left-most bit, a conflict has been detected. For non-chronological backtracking purposes, a priority encoder is used to determine the return level. Variables are ordered statically and the maximal problem size that can by analyzed by this solver is 100 variables and 200 clauses. The circuit was able to runs at a maximal frequency of 65 MHz and occupies 85% of the XC2VP4 FPGA used.

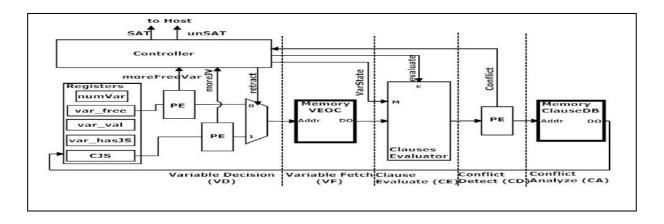

Building on notions from their previously mentioned work, Safar et al. enhance their design [6] with a five stage pipeline (Figure 19). The first, called the variable decision stage (VD), is in charge of the overall control of the solver, performs static variable decision (there

Figure 18: Safar et al. SAT solver architecture [7]

Figure 19: Safar et al. 5-stage pipelined solver [6]

is no implication computation) as well as conflict analysis. The second stage, termed the variable effect fetch stage (VF), uses a memory module to keep track of variable assignment effects on clauses. The principle behind clause evaluation from [7] is reused in the clause evaluate stage (CE) where 7-bit shift registers (one for each clause) are used to evaluate all clauses in parallel. The fourth stage (CD) deals with conflict detection (as before, a '1' in the left-most bit position of a clause evaluator register indicates a conflict) whereas the fifth and final stage (CA) analyzes conflicts. There are several advanced techniques employed in this solver. These include non-chronological backjumping, dynamic backtracking and learning without explicit implication graph traversal. As in their previous work [7], the authors use RAM modules to store SAT problem information thereby avoiding instance specificity. The maximal size of any one problem that can be accommodated by this solver is 511 variables and 511 clauses. This solver circuit operates at 120 MHz and occupies 82% of available LUTs in the XC2VP30-FF896 FPGA used as well as 47% of all available on-chip RAM. The authors report on a comparison made with the SATzilla2009\_C software solver which revealed speedups and decelerations between 0.31 and 8.81.

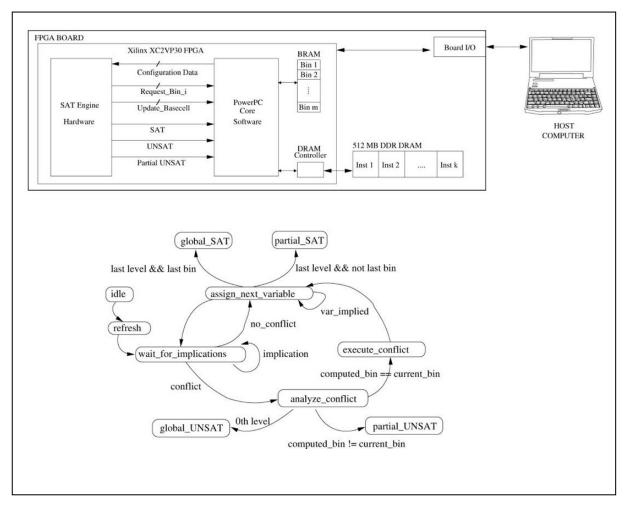

Another example of partitioning SAT problems into smaller instances is provided by Gulati et al. in their work [11] based on their previous custom application-specific integrated circuit (ASIC) implementation [45]. The general architecture and the FSM of the decision unit are presented in Figure 20. The solver proposed here traverses the implication graph as well as generates conflict clauses in hardware in parallel. The BCP methods and non-chronological

backtracking of the GRASP software SAT solver are implemented in hardware. The selection of decision variables is done statically and the number of variables and clauses (as well as clause width) is fixed.

Before solving a SAT problem, a preprocessing step is needed to heuristically partition it into instances that can fit onto the FPGA. For this purpose a 2-dimensional graph bandwidth minimization algorithm with greedy bin-packing is used. In order to find a solution to a problem, all sub-instance bins must be satisfied. Initially, all problem sub-instances are stored in off-chip RAM and are subsequently loaded into on-chip memory by a PowerPC core using the on-chip peripheral bus (OPB) and processor local bus (PLB) protocols from Xilinx. The authors use a XC2VP30 FPGA to implement their solution, which occupies about 70% of logic resources, and the maximal problem size is 8K variables and 14K clauses. Of note is the

Figure 20: Gulati et al. solver architecture (top) and decision engine FSM (bottom) [11]

mathematical model developed by the authors to project their results to the larger XC4VFX140 FPGA. On this platform, the authors extrapolate their solver to accommodate 10K variables and 280K clauses. Moreover, comparisons of XC4VFX140 projected runtimes on various SAT instances with MiniSAT, a successful software solver, yielded a speedup of about 90.

Similar to the above-mentioned Leong et al. approach, Kanazawa and Maruyama's solver (Figure 21 shows a high level view) [10] explores the use of an incomplete SAT algorithm in solving very large 3-SAT problem instances on FPGA using a variant of the WSAT stochastic local search algorithm. The authors justify their selection of this incomplete SAT method with the fact that the resulting circuit does not need complex control structures as

Figure 21: Kanazawa and Maruyama WSAT based solver [10]

well as with the idea that WSAT has very good inherent parallelism that can be used. In order to reduce circuit size, Kanazawa and Maruyama's solver evaluates, in parallel, only clauses that have the possibility of being unsatisfied by the flipping of a variable. Furthermore, this approach makes use of multi-threaded execution as a way to increase performance as many independent tries are executed in parallel. On-chip memory is heavily used for different tables and buffers as well as for storing variables which can be flipped in 1 clock cycle. An important aspect of this use of memories is the fact that the size of both on and off-chip memories as well as off-chip memory bandwidth affect performance. The authors present two implementations. The first does not use off-chip memory as the problem is completely handled by the FPGA and its memory resources. This circuit has a maximal frequency of 85.2 MHz, claims 51% of the XCV6000 FPGA slices and 90% of on-chip RAM. The maximal problem size is 2048 variables with the number of variables depending on the instance analyzed (the authors have verified up to 8500 clauses). A comparison was made with the Walksat<sup>5</sup> software solver which revealed speedups between 3.4 and 50.8 on problems from the SATLIB benchmark suites<sup>6</sup>. The second implementation makes use of 8 off-chip memory banks, runs at 67.2 MHz, and requires 88% of the same FPGA's slices and 97% of its on-chip memory blocks. The largest problem accommodated by this circuit has 32K variables and 128K clauses. A second comparison made with the same Walksat solver revealed accelerations between 13.8 and 37.0 on problems from the SAT Live<sup>7</sup> benchmark suite.

## 3.5 Summary and Analysis of Hardware SAT Solvers

To provide a compact view of all works presented heretofore, Table 1 lists characteristics and attributes of the hardware solvers presented in this chapter. A large hurdle that a hardwarebased SAT solver has to face is the potentially enormous instance representation as some problems have thousands to millions of clauses and variables. Even though FPGA capacities can, up to a certain extent, accommodate these problems, there is still a barrier that hinders the use of these powerful devices to solving SAT. Indeed, as can be seen in Table 1, the approaches presented in this chapter have mostly focused on trying to fit problems on their

<sup>&</sup>lt;sup>5</sup> Solver site: http://www.cs.rochester.edu/u/kautz/walksat/ <sup>6</sup> Site: http://www.satlib.org/

<sup>&</sup>lt;sup>7</sup> Site: http://www.satlive.org/

FPGA platform in a timely and efficient manner rather than on enhancing solvers with sophisticated heuristics and techniques, as is done for their software counterparts [34]. In addition, with larger problem sizes come immense, complicated circuits that require long times to generate. Since the principal goal of hardware SAT solvers is to provide accelerations over software solutions, long circuit build times significantly decrease or even nullify the raw speedup generated by the hardware. Thus, from instance specificity, a seemingly natural way to map SAT to hardware harvesting great amounts of FPGA parallelism, SAT solvers started evolving towards pipelined, sometimes software aided, problem-partitioning natures that rely on memory modules to store instance clauses. By doing so, solver authors have avoided having to bulk up hardware with clause-variable relationships. A tradeoff was thence made between the parallelism obtained from instance-specific circuits requiring long times for compilation and the more coarse parallelism provided by pipelined application-specific circuits with no compilation overhead. On the other hand, it is our intuition that instance specificity is a necessary avenue for providing fine grained FPGA parallelism that is required to tackle the NP-hardness of SAT. Application-specific solvers use memory modules where problem clauses are stored. Nevertheless, different problems arise from the use for memory such as latencies and other limitations (e.g. can only access a fixed width word at a time). Solvers built in this manner have, in our opinion, generally mitigated these barriers by using heuristics such as dynamic variable ordering and non-chronological backtracking. However, for real-world applications with immense problem sizes, memory transactions are unacceptable. Consequently, the rest of this work will focus on assessing the influence of memory on hardware SAT solving and on highlighting the fact that instance specificity parallelism is required to solve the Boolean satisfiability problem. To this effect, a testing platform was implemented that simulates an on-chip memory with as many read ports as there are clauses in the problem instance. The fundamental unit that was used in building this memory is the 1-bit register (grouped in arrays) residing in each logic element of the Altera DE2-70 FPGA board. As such, a focus of this investigation was to develop 2 versions of a SAT solver model based on the complete DP method that has access to all problem clauses at once. One version is a software simulator that is able to provide accurate clock cycle counts and the second is a VHDL description of the hardware necessary to implement the model on an FPGA board.

Table 1: Summary of hardware SAT solvers

| Solver                | Year          | Specificity | Algorithm                                                                                   | HW/SW                 | Maximal                          | Comments                                                                                                                                                |

|-----------------------|---------------|-------------|---------------------------------------------------------------------------------------------|-----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |               |             |                                                                                             | Execution             | Problem                          |                                                                                                                                                         |

|                       |               |             |                                                                                             |                       | Size                             |                                                                                                                                                         |