#### Université de Montréal

## Application du concept des transactions pour la modélisation et la simulation multicœur des systèmes sur puce

#### par Amine Anane

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

Thèse présentée à la Faculté des arts et des sciences en vue de l'obtention du grade de Philosophiæ Doctor (Ph.D.) en informatique

Janvier, 2012

© Amine Anane, 2012.

#### Université de Montréal Faculté des arts et des sciences

#### Cette thèse intitulée:

## Application du concept des transactions pour la modélisation et la simulation multicœur des systèmes sur puce

présentée par:

Amine Anane

a été évaluée par un jury composé des personnes suivantes:

Stefan Monnier, président-rapporteur El Mostapha Aboulhamid, directeur de recherche Yvon Savaria, codirecteur Abdelhakim Hafid, membre du jury

Samy Meftali, examinateur externe

Clément Arsenault, représentant du doyen de la FAS

Thèse acceptée le: .....

## Résumé

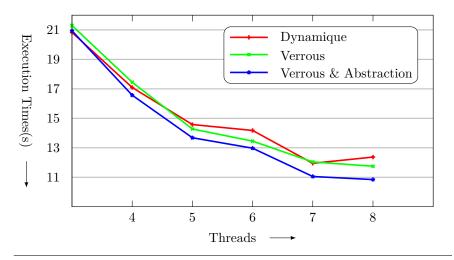

Avec la complexité croissante des systèmes sur puce, de nouveaux défis ne cessent d'émerger dans la conception de ces systèmes en matière de vérification formelle et de synthèse de haut niveau. Plusieurs travaux autour de SystemC, considéré comme la norme pour la conception au niveau système, sont en cours afin de relever ces nouveaux défis. Cependant, à cause du modèle de concurrence complexe de SystemC, relever ces défis reste toujours une tâche difficile. Ainsi, nous pensons qu'il est primordial de partir sur de meilleures bases en utilisant un modèle de concurrence plus efficace. Par conséquent, dans cette thèse, nous étudions une méthodologie de conception qui offre une meilleure abstraction pour modéliser des composants parallèles en se basant sur le concept de transaction. Nous montrons comment, grâce au raisonnement simple que procure le concept de transaction, il devient plus facile d'appliquer la vérification formelle, le raffinement incrémental et la synthèse de haut niveau. Dans le but d'évaluer l'efficacité de cette méthodologie, nous avons fixé l'objectif d'optimiser la vitesse de simulation d'un modèle transactionnel en profitant d'une machine multicœur. Nous présentons ainsi l'environnement de modélisation et de simulation parallèle que nous avons développé. Nous étudions différentes stratégies d'ordonnancement en matière de parallélisme et de surcoût de synchronisation. Une expérimentation faite sur un modèle du transmetteur Wi-Fi 802.11a a permis d'atteindre une accélération d'environ 1.8 en utilisant deux threads. Avec 8 threads, bien que la charge de travail des différentes transactions n'était pas importante, nous avons pu atteindre une accélération d'environ 4.6, ce qui est un résultat très prometteur.

Mots-clés : Modélisation, Simulation parallèle, Transactions, Multicœurs

## Abstract

With the increasing complexity of SoCs, new challenges continue to emerge in the design of these systems in terms of formal verification and high-level synthesis. Several research efforts around SystemC, considered the de facto standard for system-level design, are underway to meet these new challenges. However, because of the complex concurrency model of SystemC, these challenges remain difficult tasks. Thus, we believe it is important to continue on a better footing by using a more effective concurrency model. Therefore, in this thesis, we study a design methodology that provides a better abstraction for modeling parallel components based on the concept of transaction. We show how, through simple reasoning about transactions, it becomes easier to apply formal verification, incremental refinement and high-level synthesis. In order to evaluate the effectiveness of this methodology, we set the goal to optimize the simulation speed of a transactional model by taking advantage of a multicore machine. We present a modeling and parallel simulation environment that we developed. We study different scheduling strategies in terms of parallelism and synchronization overhead. An experiment made on a Wi-Fi 802.11a transmitter model achieved a speed up of about 1.8 using two threads. With 8 threads, although the workload of individual transactions was not significant, we could reach a speed up equal to 4.6 which is a very promising result.

Keywords: SOC Design, Parallel Simulation, Transactions, Multi-core

# Table des matières

| Résum            | né                                              | iii |

|------------------|-------------------------------------------------|-----|

| ${f Abstra}$     | act                                             | iv  |

| Table (          | des matières                                    | v   |

| Liste d          | les figures                                     | iii |

| Liste d          | les codes source                                | xi  |

| Liste d          | les Sigles                                      | xii |

| $\mathbf{Remer}$ | rciements                                       | iii |

| Chapit           | tre 1: Introduction                             | 1   |

| 1.1              | Motivations                                     | 1   |

| 1.2              | Méthodologie                                    | 5   |

| 1.3              | Objectifs                                       | 8   |

| 1.4              | Contributions                                   | 9   |

| 1.5              | Plan                                            | 12  |

| Chapit           | tre 2 : Conception des SOC                      | 14  |

| 2.1              | Flot de conception classique et ses limitations | 15  |

| 2.2              | Modélisation au niveau transaction (TLM)        | 18  |

| 2.3              | SystemC et ses limitations                      | 24  |

|                  | 2.3.1 Vue d'ensemble                            | 25  |

|                  | 2.3.2 Limitations de SystemC                    | 28  |

| Chapit | re 3: 1                           | Les transactions                            | 34  |

|--------|-----------------------------------|---------------------------------------------|-----|

| 3.1    | 3.1 Mémoire transactionnelle (TM) |                                             |     |

|        | 3.1.1                             | Avantages de TM                             | 34  |

|        | 3.1.2                             | Implémentation de TM $\dots$                | 38  |

| 3.2    | Synthè                            | ese de matériel                             | 41  |

|        | 3.2.1                             | Implémentation de référence                 | 42  |

|        | 3.2.2                             | Optimisations                               | 46  |

|        | 3.2.3                             | Bluespec                                    | 49  |

| 3.3    | Raison                            | nement formel                               | 51  |

|        | 3.3.1                             | Aperçu de TLA                               | 51  |

|        | 3.3.2                             | Raffinement                                 | 55  |

| Chapit | re 4 : '                          | Validité d'une exécution concurrente        | 57  |

| 4.1    | Enviro                            | nnement d'exécution                         | 57  |

| 4.2    | Sérialis                          | sabilité                                    | 61  |

| 4.3    | Syntax                            | te d'un ordonnancement                      | 64  |

| 4.4    | Séman                             | tique d'un ordonnancement                   | 66  |

| 4.5    | Sérialis                          | sabilité "Final State"                      | 70  |

| 4.6    | Sérialis                          | sabilité "View"                             | 72  |

| 4.7    | Sérialis                          | sabilité conflictuelle                      | 75  |

| 4.8    | Stratég                           | gies d'ordonnancement                       | 79  |

| Chapit | re 5 : 1                          | Environnement de modélisation et simulation | 84  |

| 5.1    | Modèle                            | e transactionnel                            | 86  |

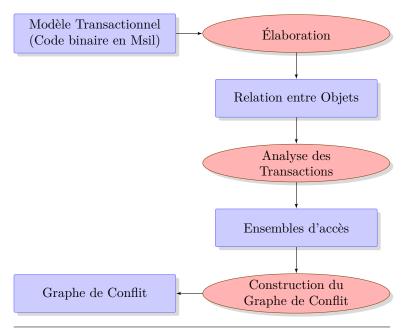

| 5.2    | Analys                            | se statique                                 | 89  |

|        | 5.2.1                             | Élaboration                                 | 89  |

|        | 5.2.2                             | Analyse des transactions                    | 91  |

|        | 5.2.3                             | Construction du graphe de conflit           | 93  |

| 5.3    | Ordoni                            | nancement                                   | 95  |

|        | 5.3.1                             | Ordonnancement dynamique                    | 99  |

|        | 532                               | Limiter le nombre de transactions           | 101 |

|         | 5.3.3                      | Ordonnancement statique          | .03 |  |  |

|---------|----------------------------|----------------------------------|-----|--|--|

| 5.4     | Mise e                     | en œuvre en utilisant .NET 1     | .05 |  |  |

|         | _                          |                                  | 12  |  |  |

| Chapit  | apitre 6 : Expérimentation |                                  |     |  |  |

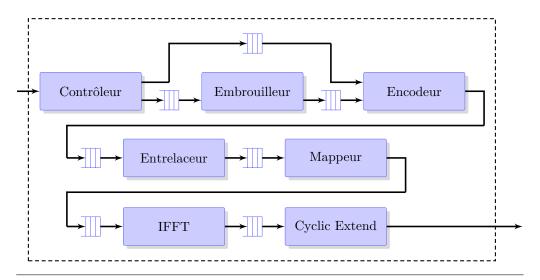

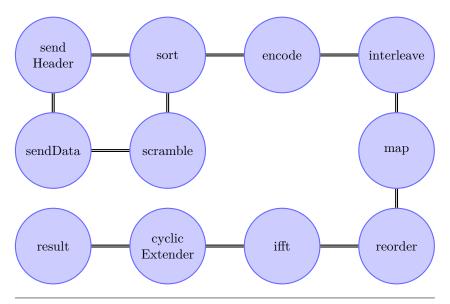

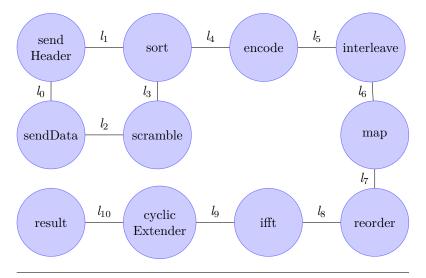

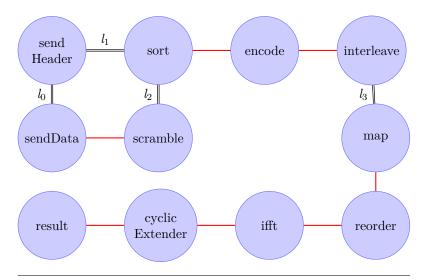

| 6.1     | Modèl                      | le du transmetteur 802.11a       | .12 |  |  |

|         | 6.1.1                      | Contrôleur                       | 13  |  |  |

|         | 6.1.2                      | Embrouilleur                     | .13 |  |  |

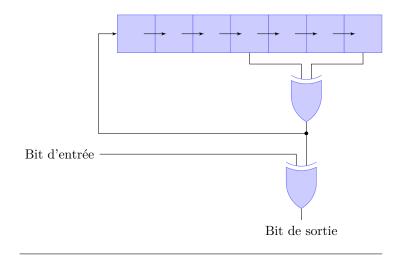

|         | 6.1.3                      | Encodeur convolutionnel          | 13  |  |  |

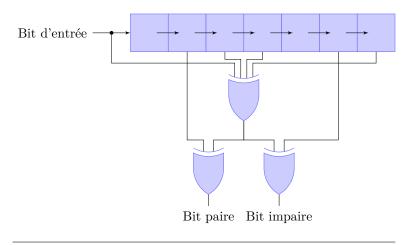

|         | 6.1.4                      | Entrelaceur                      | 14  |  |  |

|         | 6.1.5                      | Mappeur                          | .15 |  |  |

|         | 6.1.6                      | IFFT                             | 16  |  |  |

|         | 6.1.7                      | Extenseur de cycle               | 16  |  |  |

| 6.2     | Résult                     | tats expérimentaux               | 16  |  |  |

|         | 6.2.1                      | Cadre expérimental               | 16  |  |  |

|         | 6.2.2                      | Résultats expérimentaux          | 18  |  |  |

|         | 6.2.3                      | Implémentations et tests         | 26  |  |  |

|         | 6.2.4                      | Optimisation de l'ordonnancement | .35 |  |  |

| Chanit  | mo 7 .                     | Conclusion                       | 48  |  |  |

|         |                            |                                  |     |  |  |

| 7.1     |                            |                                  | .48 |  |  |

| 7.2     | Perspe                     | ectives                          | .52 |  |  |

| Bibliog | graphie                    | e                                | 56  |  |  |

| Annex   | e I :                      | Raffinement d'une FIFO x         | κiν |  |  |

| I.1     | Interfa                    | ace                              | XV  |  |  |

| I.2     | Raffin                     | nement des données               | vii |  |  |

| I.3     | Raffin                     | nement de l'atomicité            | vii |  |  |

| I.4     | Implé                      | mentation finale                 | XX  |  |  |

## Liste des figures

| 1.1 | Environnement de Conception                                                | 10 |

|-----|----------------------------------------------------------------------------|----|

| 2.1 | Flot de conception classique                                               | 15 |

| 2.2 | Modèles TLM                                                                | 21 |

| 2.3 | Architecture du langage SystemC                                            | 26 |

| 2.4 | Modèle d'exécution de SystemC                                              | 27 |

| 3.1 | Difficulté d'étendre le logiciel avec des verrous[24]                      | 37 |

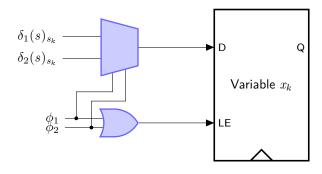

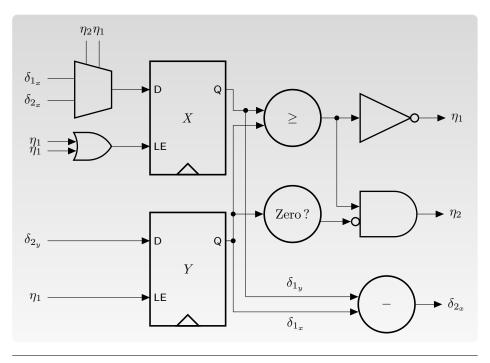

| 3.2 | Circuit RTL d'un registre correspond à une variable accédée par            |    |

|     | deux transactions                                                          | 43 |

| 3.3 | Circuit RTL généré à partir d'un modèle transactionnel                     | 44 |

| 3.4 | Circuit généré à partir du modèle transactionnel $gcd(p,q)$                | 45 |

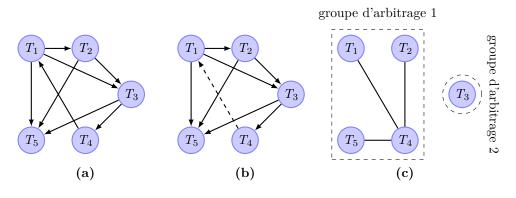

| 3.5 | Analyse des transactions. (a) graphe $<_{SC}$ orienté, (b) graphe $<_{SC}$ |    |

|     | acyclique, (c) groupe d'arbitrages                                         | 49 |

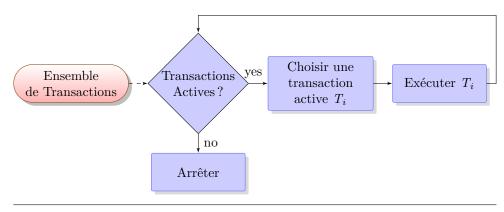

| 4.1 | Sémantique d'Exécution d'un Modèle Transactionnel                          | 58 |

| 4.2 | Environnement d'exécution d'un modèle de transactions                      | 59 |

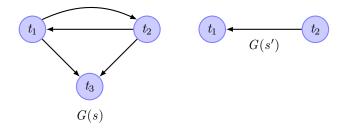

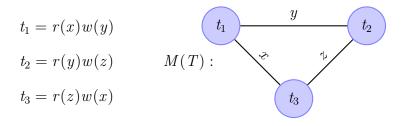

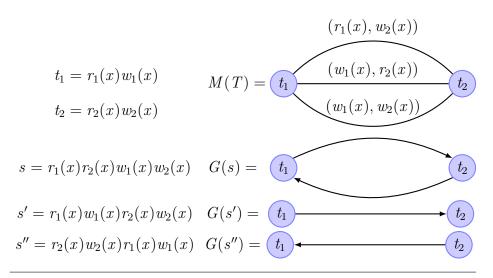

| 4.4 | Exemple de Multigraphe de conflit                                          | 80 |

| 4.5 | Correspondance entre multigraphe de conflit et graphe de sériali-          |    |

|     | sabilité                                                                   | 81 |

| 4.6 | Exécution Concurrente                                                      | 82 |

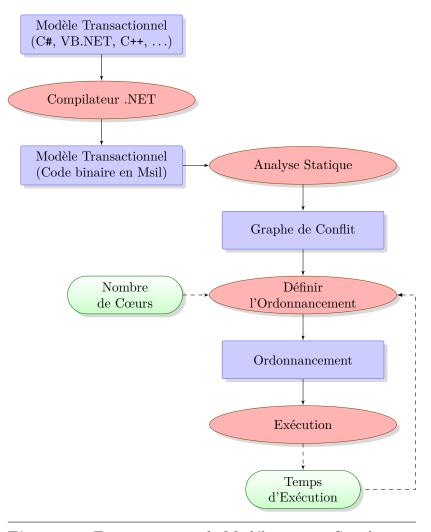

| 5.1 | Environnement de Modélisation et Simulation                                | 85 |

| 5.3 | Phase de l'Analyse Statique                                                | 90 |

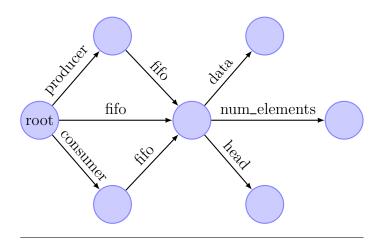

| 5.4 | Graphe de Relation de l'Exemple 5.2                                        | 92 |

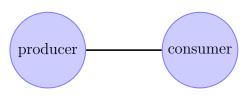

| 5.5 | Graphe de Conflit de l'Exemple 5.2                                         | 94 |

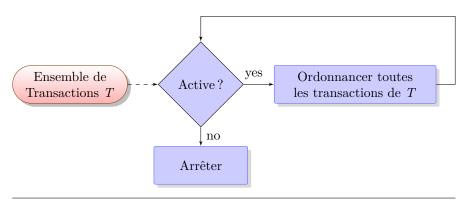

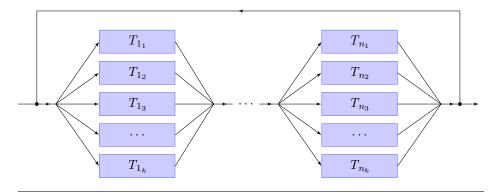

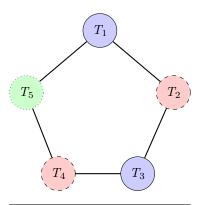

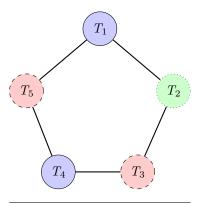

| 5.6  | Ordonnancement des transactions                                      | 96  |

|------|----------------------------------------------------------------------|-----|

| 5.7  | Exemple de coloration de graphe                                      | 96  |

| 5.8  | Nouvelle coloration du graphe de la Figure 5.7                       | 97  |

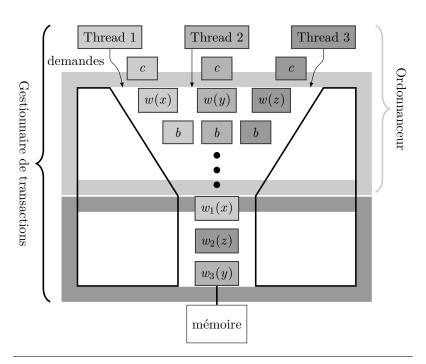

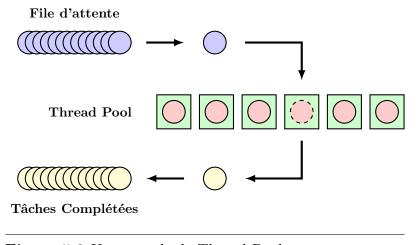

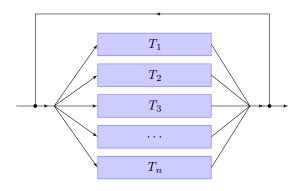

| 5.9  | Un exemple de Thread Pool                                            | 100 |

| 5.10 | Thread Pool avec nombre de tâches ne dépassant pas le nombre de      |     |

|      | threads                                                              | 104 |

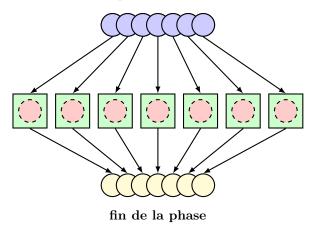

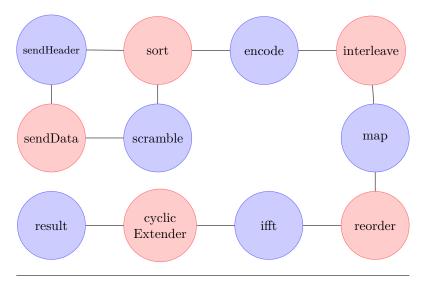

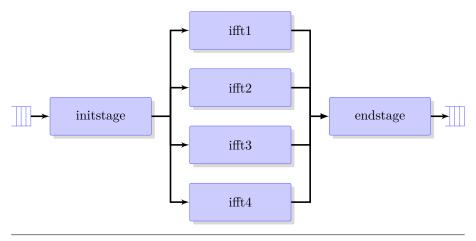

| 6.1  | Modèle du transmetteur 802.11a                                       | 112 |

| 6.2  | Fonction d'embrouillage                                              | 114 |

| 6.3  | Fonction d'encodage                                                  | 114 |

| 6.4  | Coloration du Graphe de Conflit                                      | 119 |

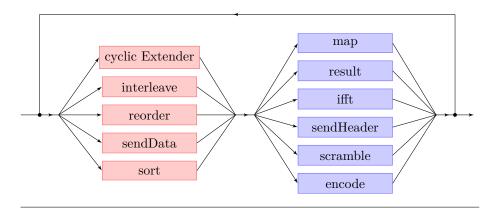

| 6.5  | Exécution Parallèle                                                  | 119 |

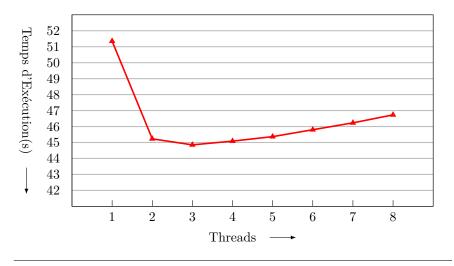

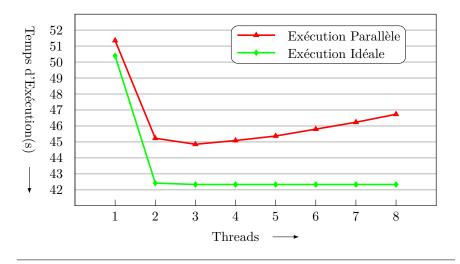

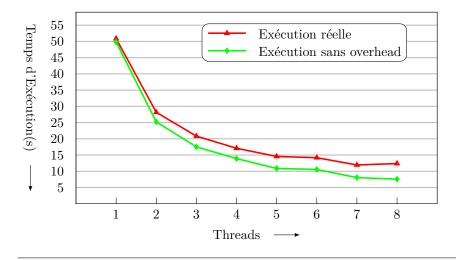

| 6.6  | Temps d'exécution suite à l'ordonnancement de la Figure $6.5$        | 120 |

| 6.7  | Comparaison des Temps d'exécution obtenus par rapport aux meilleu    | rs  |

|      | temps que nous pouvons obtenir                                       | 124 |

| 6.8  | Un étage parmi les trois étages de la nouvelle IFFT Pipelinée        | 125 |

| 6.9  | Temps d'exécution en utilisant l'architecture pipelinée de la Figure |     |

|      | 6.8                                                                  | 126 |

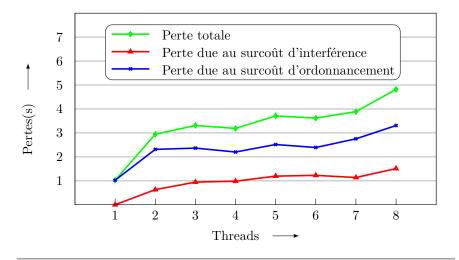

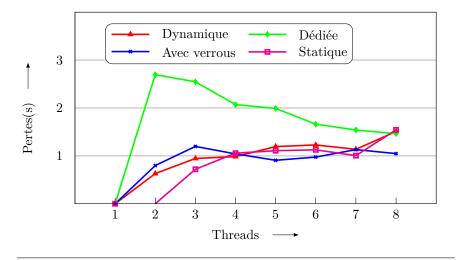

| 6.10 | Pertes dues aux surcoûts                                             | 129 |

| 6.11 | Surcoût d'ordonnancement                                             | 130 |

| 6.12 | Surcoût d'interférence                                               | 132 |

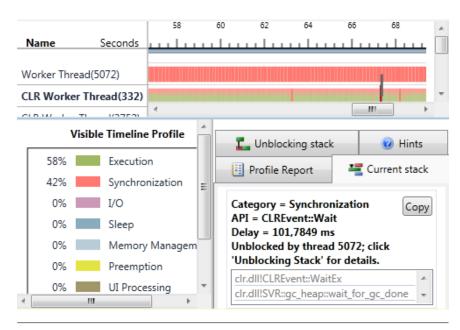

| 6.13 | Attente du Garbage Collector pour finir le ramassage                 | 133 |

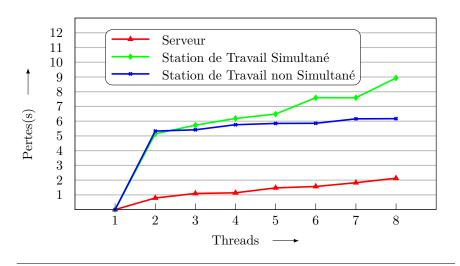

| 6.14 | Comparaison des surcoûts d'interférence selon le type du Garbage     |     |

|      | Collector                                                            | 134 |

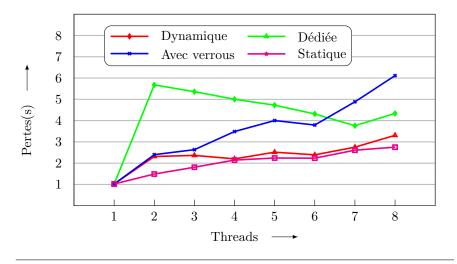

| 6.15 | Ordonnancement des transactions en présence de verrous               | 137 |

| 6.16 | Associer un seul verrou pour les trois transactions du graphe de     |     |

|      | verrous au lieu d'un verrou pour chaque paire                        | 137 |

| 6.17 | Multigraphe de Conflit                                               | 141 |

| 6.18 | Graphe de Concurrence et Attribution des Verrous                     | 142 |

| 6.19 | Relations de conflits lors de l'accès à la FIFO                      | 143 |

| 6.20 | Exemple de FIFO Concurrente                                          | 144 |

| 6.21 | Nouveau multigraphe de conflit ayant moins de cycles et de verrous      | 145 |

|------|-------------------------------------------------------------------------|-----|

| 6.22 | Temps d'exécution par abstraction de la FIFO                            | 146 |

| 7.1  | Environnement de modélisation et simulation                             | 150 |

| 7.2  | Flot de conception utilisant la méthodologie basée sur les transaction. | 152 |

| I.1  | Interaction de la FIFO avec son environnement                           | xvi |

## Liste des codes source

| 5.1 | Code de l'ordonnanceur                                           | 105 |

|-----|------------------------------------------------------------------|-----|

| 5.2 | Encapsulation de la méthode avec l'attribut Transaction dans une |     |

|     | méthode transaction                                              | 106 |

| 5.3 | Création d'un delegate genericTransaction                        | 108 |

| 6.1 | Déterminer une estimation du temps d'exécution                   | 123 |

## Liste des Sigles

CSR Classe des ordonnancements "sérialisables conflictuels"

FSR Classe des ordonnancements sérialisables "Final State"

IP Intellectual Property

ITRS International Technology Roadmap for Semiconductors

MPSOC MultiProcessor System-on-Chip

OSCI Open SystemC Initiative

RTL Register Transfer Level

STM Software Transactional Memory

SOC System On a Chip

TLM Transaction Level Modeling

TM Transactional Memory

VSR Classe des ordonnancements sérialisables "View"

## Remerciements

Je tiens à remercier en tout premier lieu mon directeur de recherche, le professeur El Mostapha Aboulhamid, de m'avoir soutenu, conseillé et dirigé tout au long de cette thèse.

Je voudrais ensuite remercier toutes les personnes qui ont contribué, de près ou de loin, à ce travail, spécialement Julie Vachon et mon codirecteur le professeur Yvon Savaria.

Je tiens à saluer ma mère, mon père et ma sœur pour m'avoir encouragé à aller au bout de cette thèse.

Finalement, je voudrais remercier ma femme, pour son soutien et sa patience et d'avoir supporté mes sautes d'humeur durant toutes ces années. Sans oublier bien sûr mon cher fils qui était toujours compréhensif quand des fois je le prive de sa tournée au parc pour finir mon travail.

1

## Introduction

En raison de l'avancée fulgurante dans la technologie de fabrication des circuits intégrés qui permet d'intégrer de plus en plus de transistors dans un même circuit, plusieurs composants électroniques, connus sous le nom d'IP, peuvent maintenant être programmés et regroupés dans une même puce afin de former un système électronique complet, appelé système sur puce (SOC).

Cette complexité croissante des systèmes sur puce rend leur conception de plus en plus difficile. Cette difficulté se manifeste par ce qui est nommé, "écart de productivité" («design productivité gap»). Cet écart découle du fait que le nombre de transistors disponibles augmente plus rapidement que notre capacité à les concevoir efficacement.

Nous allons commencer par montrer les défis que la conception des systèmes sur puce devrait relever afin de minimiser cet écart de productivité. Ensuite nous présentons l'approche de conception que nous avons proposée dans le but de pouvoir relever ces défis. En troisième partie, nous précisons les objectifs que nous envisageons d'atteindre au cours de ce projet, puis nous décrivons les contributions apportées. Finalement, nous donnons le plan de la présente thèse.

#### 1.1 Motivations

Au fil de l'évolution des systèmes microélectroniques industriels, les concepteurs ont été toujours forcés d'améliorer leur productivité afin d'exploiter pleinement la capacité croissante des circuits intégrés et ainsi réduire l'écart de productivité. L'approche utilisée visait toujours l'augmentation du niveau d'abstraction du modèle utilisé pour la description du système à implémenter. Ainsi, la représentation d'un système matériel est passée d'une représentation au niveau transistors

à une représentation composée de portes logiques pour enfin arriver à une représentation basée sur les transferts de registres (RTL). Aujourd'hui, l'utilisation des modèles RTL comme base de départ dans le flot de conception des systèmes sur puce n'offre plus un niveau d'abstraction suffisant pour arriver à réduire l'écart entre la productivité de conception et la capacité d'intégration des puces actuelles. Par conséquent, l'élaboration d'une nouvelle méthodologie de conception initiée à un niveau d'abstraction supérieure à RTL, connue sous le nom de conception au niveau système, est devenue primordiale si l'on souhaite réduire cet écart.

Depuis plus d'une décennie, plusieurs compagnies industrielles ont joint leur effort en formant l'organisme OSCI (Open SystemC Initiative) afin de promouvoir et adopter une nouvelle méthodologie de conception au niveau système connue sous le nom de modélisation au niveau transaction[14] (TLM: Transaction-Level Modeling). Cet effort a abouti à la création du langage de spécification SystemC, qui est devenu une norme IEEE en 2005[34], et à la spécification d'une norme TLM[35] qui régit la communication entre les modèles TLM. Les avantages clefs derrière la méthodologie TLM et le langage SystemC sont les suivants:

- Promouvoir une méthodologie de conception de système sur puce, qui soit adoptée par l'industrie des systèmes microélectroniques afin de rendre possibles l'interopérabilité des modèles et la réutilisation de propriétés intellectuelles (IP).

- Permettre de spécifier une plateforme virtuelle pour commencer à développer et vérifier le logiciel au tout début de cycle de développement.

- Permettre la séparation ente la communication et la fonctionnalité afin de promulguer la réutilisabilité et l'exploration architecturale.

Malgré que la conception au niveau système et l'adoption de la méthodologie SystemC-TLM ont pu faciliter la conception des systèmes sur puce, il existe encore des défis à relever à court et moyen termes puisque la complexité de ces systèmes ne cesse d'augmenter. Voici les différents défis majeurs afin de faire face à cette complexité croissante.

• Verification Formelle : L'ITRS («International Technology Roadmap for Semiconductors»), un organisme regroupant les principales régions de fabrication des circuits intégrés dans le monde, a été créé afin d'étudier et estimer les besoins technologiques futurs de l'industrie des semiconducteurs sur une période de 15 années. Concernant la conception niveau système, l'ITRS considère que l'écart de productivité est dû en grande partie aux méthodes de vérification actuelles, basées essentiellement sur la simulation, qui nécessitent un temps et un nombre d'ingénieurs considérable afin de pouvoir produire un système de qualité acceptable. Ceci a mené l'ITRS à identifier certains défis à relever concernant les méthodes de vérification. Voici le texte intégral de [36] montrant les besoins à court et à long terme afin de résoudre les problèmes liés aux techniques de vérification des systèmes sur puce :

« Many of the key challenges for verification are relevant to most or all system drivers. In the near term, the primary issues are centered on making formal and semi-formal verification techniques more reliable and controllable. In particular, major advances in the capacity and robustness of formal verification tools are needed, as well as meaningful metrics for the quality of verification. In the longer term, issues focus mainly on raising the level of abstraction and broadening the scope of formal verification. These longer-term issues are actually relevant now, although they have not reached the same level of crisis as other near-term challenges. In general, all of the verification challenges apply to SoC. »

Comme la conception se déplace à un niveau d'abstraction au-dessus de RTL, la vérification devra suivre aussi. En effet, les défis consisteront à :

- adapter et développer des méthodes de vérification formelle à des niveaux d'abstraction supérieurs, pour faire face à la complexité accrue des systèmes rendue possible grâce à la conception au niveau système

- développer des moyens pour vérifier l'équivalence entre les modèles à des niveaux d'abstraction supérieurs et les modèles à des niveaux inférieurs. Ces défis seront beaucoup plus difficiles si les décisions concer-

nant l'augmentation du niveau d'abstraction sont prises sans égard pour la vérification

Par exemple, l'utilisation de langage de description à haut niveau d'abstraction avec des sémantiques mal définies ou inutilement complexes, ou l'adoption d'une méthodologie s'appuyant sur des modèles de simulation à des niveaux d'abstraction supérieurs sans avoir une relation claire avec les niveaux d'abstraction de plus bas niveaux.

Malheureusement SystemC fait partie des langages de description qui ne possèdent pas une sémantique formelle complète et précise afin de pouvoir développer des techniques de vérification formelle efficaces pour celui-ci[60]. Cette difficulté à définir une sémantique formelle pour SystemC provient à la fois de sa nature orientée objet et à la sémantique complexe de son simulateur événementiel[60].

- Vitesse de simulation : Comparée à un modèle RTL, la simulation d'un modèle TLM est largement améliorée permettant ainsi l'exploration architecturale et le développement de plateformes virtuels pour la simulation du logiciel. Cependant, avec la complexité croissante des systèmes sur puce et l'augmentation de la quantité de logiciels embarqués, le besoin d'augmenter la vitesse de simulation est de plus en plus ressenti. La disponibilité croissante des machines multicœurs est un atout considérable afin d'améliorer la vitesse de simulation. Toutefois, il faut que la simulation soit conçue pour qu'elle s'exécute en parallèle et ainsi profiter de plusieurs cœurs. Malheureusement le modèle de concurrence basé sur des threads synchronisés par des événements rend la parallélisation du simulateur de SystemC une tâche aussi difficile que de lui définir une sémantique formelle.

- Synthèse de haut niveau (synthèse comportementale) :Pouvoir synthétiser un système matériel à partir d'un modèle défini à un niveau d'abstraction plus haut que RTL est indispensable pour la conception au niveau système. Malheureusement, malgré que la synthèse comportementale ait été

un sujet de recherche depuis plusieurs décennies, et malgré les progrès récents dus à SystemC et à la modélisation au niveau TLM, des techniques de synthèse comportementale efficaces ne sont pas encore disponibles[36]. En effet, une fois qu'un modèle TLM basé sur SystemC a été spécifié et validé, il doit être raffiné vers un modèle RTL pour la synthèse matérielle. Ce processus est loin d'être automatisé et le raffinement TLM à RTL reste en général une tâche manuelle. En plus, les deux modèles sont parfois préparés par deux ingénieurs différents, qui rend la tâche de raffinement un processus encore plus compliqué[23]. Cette complexité est due principalement à l'écart entre les modèles TLM et RTL où le premier se base sur des appels de fonction alors que l'autre doit gérer et synchroniser la communication entre les différents composants à l'aide de signaux.

### 1.2 Méthodologie

Afin de faire face à la complexité croissante des systèmes sur puce et relever les différents défis présentés plus haut, nous avons choisi d'utiliser une nouvelle méthodologie qui tient compte des avantages de SystemC tout en évitant ses limitations. Cette méthodologie se base sur le concept des transactions permettant de décrire un système comme étant un ensemble d'actions atomiques . Cette notion fut introduite dans le langage des commandes gardées de Dijkstra[21]. Cependant, avec la complexité croissante des systèmes matériels et logiciels et la disponibilité croissante des machines multicœurs, les recherches actuelles autour des transactions ont pris de l'importance en raison de la nécessité d'avoir une meilleure abstraction afin de décrire des processus parallèles[42]. En conséquence, nous allons étendre ce concept au domaine de la conception des systèmes sur puce.

Dans ce qui suit, nous allons présenter les différents avantages que nous pouvons tirer de cette méthodologie tout en montrant comment elle pourrait éliminer les limitations de SystemC mentionnées précédemment.

• Raisonnement simple : Une transaction permet d'abstraire un ensemble d'opérations en une seule action indivisible qui se comporte d'une manière

atomique. Ceci permet au concepteur de raisonner sur la validité de la fonctionnalité d'une transaction comme si elle s'exécute dans un environnement monothread. Ainsi il n'a pas à se préoccuper des interactions complexes avec les autres transactions du programme qui s'exécutent en parallèle.

- Modélisation à plusieurs niveaux d'abstraction : Le fait que le modèle de concurrence basé sur les transactions ait un raisonnement simple n'empêche pas qu'il soit assez expressif afin de modéliser des systèmes à plusieurs niveaux d'abstraction. Par exemple, à haut niveau d'abstraction, un processeur peut être spécifié par une simple transaction qui décode et exécute les différentes instructions. En descendant plus bas dans le flot de conception, l'architecture pipelinée du processeur peut être représentée par plusieurs transactions où chaque transaction décrit un étage du pipeline. Par conséquent le fait d'utiliser le même modèle transactionnel tout le long du flot de conception fournit plusieurs avantages tels que :

- Adopter une méthodologie basée sur le raffinement incrémental où le détail est ajouté progressivement afin de contrôler la complexité du modèle. Ainsi, dans un même modèle transactionnel, nous aurons la possibilité de spécifier différents composants ayant des niveaux d'abstractions différents. Cependant, lors de la simulation, vérification ou synthèse, le raisonnement est toujours le même puisque le même modèle de concurrence est utilisé partout.

- Le modèle transactionnel s'adapte bien avec la méthodologie basée sur TLM, puisque par nature il est transactionnel. En plus, il donne au terme transaction une sémantique précise comparée à SystemC qui traite une transaction simplement comme un appel de fonction sans tenir compte de l'aspect atomique de la transaction.

- Contrairement à SystemC où la synthèse matérielle doit passer par un modèle RTL qui est en général spécifié manuellement, la méthodologie basée sur les transactions a pu faire un pas en avant en permettant de

générer automatiquement un modèle RTL à partir d'un modèle transactionnel[32, 31]. Aujourd'hui nous retrouvons Bluespec qui se base des modèles transactionnels pour la synthèse matérielle[12].

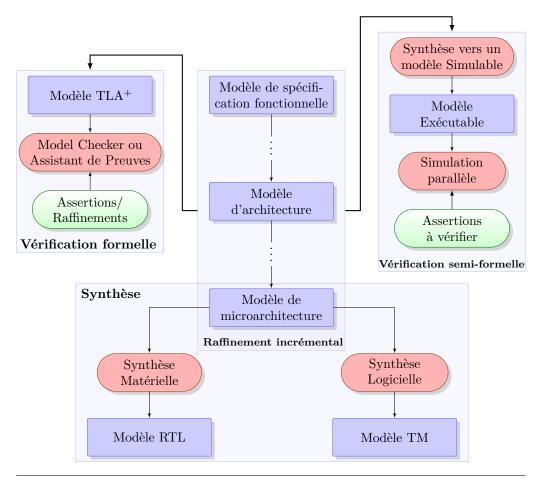

- Vérification Formelle : Vu la simplicité de la sémantique d'une transaction qui se repose sur sa propriété d'atomicité, plusieurs formalismes ont été proposés afin de pouvoir raisonner formellement sur les transactions. Nous mentionnons à tire d'exemple la logique temporelle des actions (TLA<sup>+</sup>)[40], le langage formel UNITY[50] ou les commandes gardées de Dijkstra[21]. Comme mentionné plus haut, un des défis à relever est de rendre les méthodes de vérification formelle plus fiables et contrôlables. Par conséquent une méthodologie qui se base sur des modèles de calcul ayant une sémantique formelle est une condition nécessaire afin d'atteindre ces objectifs. Grâce à cette sémantique formelle, nous pouvons envisager des techniques de raffinement qui garantissent la génération d'un modèle correct par construction. Ces techniques permettront, soit de raffiner automatiquement un design décrit à un haut niveau d'abstraction vers une implémentation plus concrète, soit de prouver formellement qu'un raffinement fait manuellement préserve les fonctionnalités du modèle initial. Grâce à cette sémantique formelle, il devient possible de développer des algorithmes de transformation de modèles transactionnels ciblant des plateformes de simulation multicœur dans le but d'accélérer le temps de simulation. Ceci constituait l'objectif majeur de ce projet de recherche (voir prochaine section 1.3).

- Amélioration de la productivité du logiciel embarqué : La complexité des systèmes augmente considérablement avec l'augmentation de la quantité de logiciels dans les systèmes sur puce et de l'adoption rapide des architectures SOC multicœur (MPSOC). Ainsi une meilleure abstraction pour décrire des systèmes concurrents est nécessaire afin d'améliorer la productivité dans le développement du logiciel embarqué. Comme solution à ce problème, l'ITRS[36] a proposé d'approfondir les recherches sur l'approche de mémoire transactionnelle (TM[42]) afin qu'elle soit adoptée comme méca-

nisme de contrôle de concurrence. Par conséquent l'utilisation d'un modèle transactionnel pour spécifier le logiciel embarqué d'un système sur puce et qui restera le même mécanisme de concurrence dans l'implémentation finale est un atout majeur pour améliorer la productivité des logiciels embarqués.

### 1.3 Objectifs

Au cours de ce projet de recherche, nous nous sommes fixé l'objectif d'accélérer la vitesse de simulation d'un système transactionnel. Pour aboutir à cet objectif, il faut traiter deux aspects dans le cycle de développement des systèmes sur puce. L'aspect modélisation et l'aspect simulation :

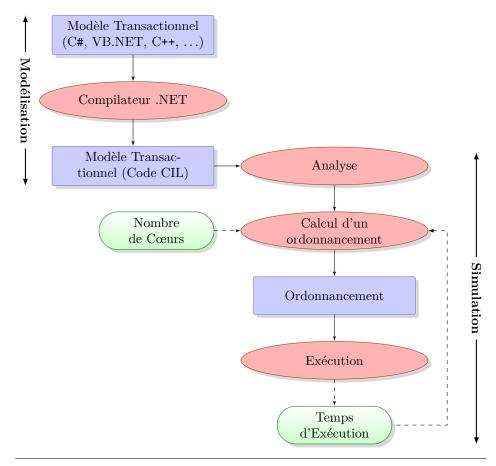

- Modéliation: Le premier objectif consiste à développer un environnement de conception basé sur les transactions. Il est important de noter, en comparaison avec SystemC, que la structure du modèle doit être complètement dissociée du simulateur. Ceci est primordial pour que nous puissions adapter le simulateur au modèle afin d'optimiser la vitesse de simulation. Il s'agit d'ailleurs de l'objectif principal de cette thèse décrit plus bas. La première question qui se pose est : quel langage faut-il utiliser afin de décrire des modèles transactionnels? Nous avons décidé d'utiliser la plateforme de développement «.Net Framework» à cause des avantages multiples de cette plateforme tels que la programmation par attribut, l'introspection et la production dynamique de code. Une fois que l'environnement de programmation est choisi, la principale tâche à réaliser est de définir 1) la structure à donner à la description d'un système sur puce, 2) les éléments de cette structure, et 3) la manière de rassembler ces éléments pour former un modèle transactionnel complet.

- Simulation: Une des raisons d'élever le niveau d'abstraction à un niveau TLM dans le flot de conception des systèmes sur puce est de permettre le développement du logiciel très tôt dans le cycle de développement. En effet, un modèle TLM va fournir au concepteur de logiciel un prototype virtuel décrivant l'architecture de la plateforme cible. Ce prototype virtuel constitue le

modèle de référence pour développer, simuler et valider le logiciel. Cependant avec l'adoption rapide des architectures SOC multicœur et l'augmentation de la quantité du logiciel embarqué, accélérer la vitesse de simulation devient crucial afin de pouvoir valider le logiciel et avoir une meilleure couverture. Puisque les SOC ont opté pour des architectures multicœurs et vu que le nombre de coeurs dans les stations de travail ne cesse d'augmenter, il est clair que pour minimiser l'écart de productivité il faut suivre la tendance et développer des environnements de conception qui doivent tenir compte des ces nouvelles technologies. En conséquence, l'autre objectif principal de cette thèse est de concevoir des ordonnanceurs de simulation de modèles transactionnels qui prennent avantage d'une machine multicœur afin d'accélérer la vitesse de simulation.

#### 1.4 Contributions

Suite à ce projet, nous pensons avoir contribué au domaine de la conception des systèmes sur puce sur différents points cités ci-dessous.

- L'identification des limitations de SystemC sur différents aspects tels que modélisation, simulation et vérification (voir sous-section 2.3.2) et la proposition d'une nouvelle méthodologique de conception basée sur les transactions[3] dans le but de contourner les obstacles de SystemC et relever les défis identifiés par l'ITRS (voir section 1.1).

- Avoir associé plusieurs recherches dans des domaines différents (chapitre 3) qui de loin semblent toucher des concepts différents alors qu'elles traitent la même notion de transaction. Par exemple nous retrouvons les transactions[62] dans le domaine des bases de données, la logique temporelle des actions[40] dans le domaine de la vérification formelle, la mémoire transactionnelle[42] dans le domaine de la programmation concurrente, et les règles de réécriture de termes[32] dans le domaine de la synthèse matérielle. À la fin de cette thèse (chapitre 7), nous avons montré comment nous pouvons

intégrer plusieurs de ces travaux dans un cycle de développement complet d'un système sur puce.

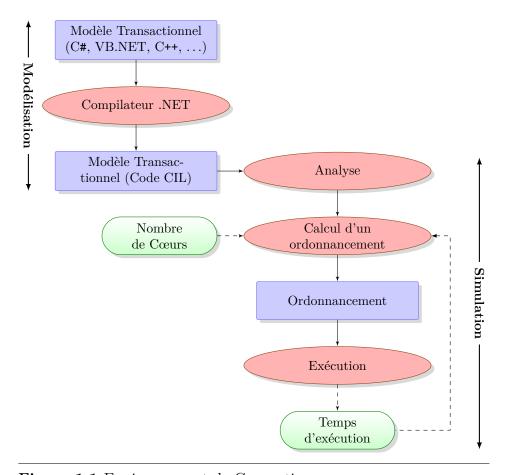

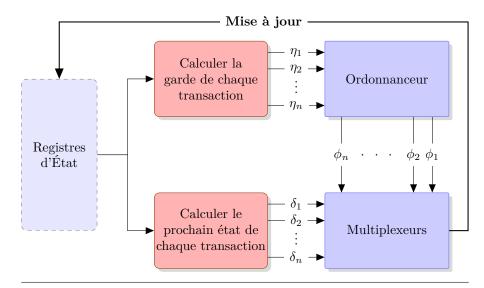

• Le développement d'un environnement de modélisation et de simulation de systèmes sur puce basés sur le concept de transactions (voir Figure 1.1).

Figure 1.1 Environnement de Conception

Les contributions clés suite à ce travail sont :

• Séparation entre le modèle et le simulateur : Contrairement à SystemC, notre environnement assure une orthogonalité complète entre la modélisation et la simulation. En effet, un modèle SystemC compilé est un modèle exécutable qui contient l'implémentation du simulateur alors qu' un modèle transactionnel une fois compilé garde ses métadonnées, sa structure et son comportement, sans aucun détail sur comment il

- va être simulé. Un des avantages de cette approche est de nous avoir permis d'utiliser le modèle avec différents simulateurs afin d'analyser plusieurs alternatives (chapitre 5). Vous pouvez consulter les travaux de [41] pour plus de détails sur les avantages que nous pouvons tirer grâce à cette séparation des aspects.

- Analyseur intégré : L'environnement de conception contient un analyseur intégré qui permet d'extraire du modèle transactionnel l'architecture et le comportement des différents composants ainsi que leurs interactions. Cet analyseur peut être aussi utilisé si nous voulons étendre l'environnement pour inclure d'autres outils pour la vérification formelle ou la synthèse matérielle. Ceci permet par exemple de transformer le modèle vers du code TLA<sup>+</sup> ou Bluespec. La réalisation de cet analyseur est rendue moins compliquée grâce à l'introspection et la programmation par attributs que fournit la plateforme .NET. D'un autre côté, définir un analyseur pour SystemC était l'objet de plusieurs recherches intensives[46] vu la complexité du langage. En effet, les travaux dans [46] ont montré que, malgré le besoin croissant d'analyser des modèles SystemC suite à la complexité croissante des systèmes sur puce, les outils disponibles ne sont pas en mesure d'analyser des modèles SystemC arbitraires.

- o Environnement multi-langage: Un modèle écrit en utilisant un langage de haut niveau tel que C# est compilé vers le langage intermédiaire commun CIL. Le simulateur utilise le langage CIL pour extraire toutes les informations nécessaires pour l'analyse du modèle transactionnel. En conséquence notre environnement de simulation est indépendant du langage et peut supporter plusieurs langages. Ceci constitue un atout majeur au cas où, par exemple, nous voulons décrire un système hétérogène avec des langages de descriptions spécifiques pour chaque sous-système. Une fois compilé, le système va avoir une représentation standard basée sur un modèle transactionnel décrit en langage CIL.

• Accélération de la Simulation : L'environnement de simulation tient compte de la structure du modèle transactionnel et de l'interaction entre les différentes transactions, du nombre de cœurs de la machine de simulation et d'une estimation du temps d'exécution afin de générer un ordonnancement décrivant comment les transactions doivent être ordonnancées et exécutées en parallèle. Nous avons testé cet environnement (chapitre 6) sur une étude de cas constituée d'un modèle de transmetteur selon la norme Wi-Fi 802.11a. Avec deux processeurs, nous avons obtenu une accélération d'environ 1.8, qui se rapproche d'une accélération optimum. Avec 8 processeurs, nous avons pu atteindre une accélération d'environ 4.6, qui est un résultat très prometteur.

#### 1.5 Plan

Le chapitre 2 présente le flot de conception classique d'un système microélectronique et montre comment il ne répond plus aux exigences des systèmes sur puce. Ensuite il décrit la solution qui a été adoptée par l'industrie qui est basée sur la conception au niveau transaction (TLM) et le langage de description SystemC. Enfin, il détaille les limitations de ce langage pour satisfaire les nouveaux besoins dans la conception des SOC à cause de leur complexité qui ne cesse de s'accroitre.

Le chapitre 3 introduit le concept de transaction que nous proposons comme méthodologie de conception des SOC pour remédier aux limitations de SystemC. Il montre le mérite de ce concept en tant que mécanisme de contrôle de concurrence. Il décrit différents travaux qui ont été faits autour des transactions et montre comment ces travaux peuvent être appliqués dans plusieurs aspects de la conception des systèmes sur puce tels que la modélisation, la vérification et la synthèse.

Le chapitre 4 présente une étude théorique sur les modèles transactionnels et leur environnement d'exécution. Il définit une sémantique formelle au modèle transactionnel et introduit plusieurs notions de validité afin de montrer comment une exécution concurrente des transactions doit se dérouler pour respecter la sémantique d'exécution du modèle transactionnel. Cette étude théorique constitue

la base pour le développement de l'environnement de simulation présenté au chapitre 5.

Le chapitre 5 décrit l'environnement de modélisation et de simulation qui a été réalisé en utilisant la plateforme .Net. Il montre comment un modèle transactionnel est représenté dans cette plateforme puis il décrit les étapes développées et les problèmes d'optimisation linéaire utilisés permettant de transformer un modèle transactionnel vers un modèle exécutable pour une simulation concurrente profitant d'une machine multicœur.

Le chapitre 6 détaille les différentes expérimentations qui ont été faites afin d'évaluer les performances d'une simulation parallèle en se basant sur un modèle transactionnel spécifiant un transmetteur selon la norme Wi-Fi 802.11a. Il étudie et compare les différentes alternatives déjà présentées dans le chapitre 5 puis il propose des optimisations afin de minimiser les surcoûts d'ordonnancement et augmenter le parallélisme entre les transactions.

Le chapitre 7 conclut cette thèse en rappelant les principales réalisations effectuées et les contributions apportées en matière de modélisation et simulation des systèmes sur puce. Ensuite il propose des perspectives en matière de vérification, raffinement et synthèse afin de compléter le cycle de conception de systèmes sur puce et pouvoir relever les défis présentés dans la section 1.1. 2

## Conception des SOC<sup>1</sup>

Au fil de l'évolution des systèmes microélectroniques industriels, les concepteurs ont été toujours forcés d'améliorer leur productivité afin d'exploiter pleinement la capacité croissante des circuits intégrés et ainsi réduire l'écart de productivité. L'approche utilisée visait toujours l'augmentation du niveau d'abstraction du modèle utilisé pour la description du système à implémenter. Ainsi, la représentation d'un système matériel est passée d'une représentation au niveau transistors à une représentation composée de portes logiques pour enfin arriver à une représentation basée sur les transferts de registres (RTL). Aujourd'hui, l'utilisation des modèles RTL comme base de départ dans le flot de conception des systèmes sur puce n'offre plus un niveau d'abstraction suffisant pour arriver à réduire l'écart entre la productivité de conception et la capacité des puces actuelles. Par conséquent, l'élaboration d'une nouvelle méthodologie de conception initiée à un niveau d'abstraction supérieur au niveau RTL, connue sous le nom de conception au niveau système, est devenue primordiale si l'on souhaite réduire cet écart.

Dans ce chapitre, nous donnons un aperçu du flot de conception classique et de ses limitations. Ensuite, une solution à ses limitations est présentée en introduisant la modélisation au niveau transaction, communément appelée TLM, et en montrant comment elle est adaptée au nouveau flot de conception. Finalement, nous introduisons SystemC qui est le langage de description adopté par l'industrie et grâce auquel le TLM est supporté. Nous présentons les inconvénients de SystemC qui nous ont poussés à adopter une nouvelle méthodologie qui est basée sur le concept des transactions (chapitre 3).

<sup>1.</sup> L'étude faite dans ce chapitre fait partie de nos publications[3]

## 2.1 Flot de conception classique et ses limitations

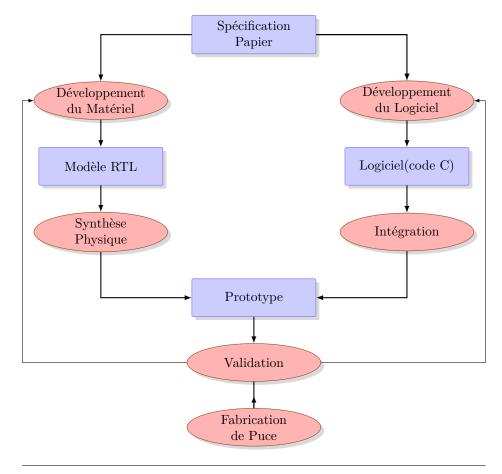

Figure 2.1 Flot de conception classique

Le flot de conception des systèmes sur puce se veut une méthodologie permettant de concevoir, vérifier et délivrer un SOC fonctionnellement correct tout en respectant des contraintes non fonctionnelles, telles que la latence, le débit et la puissance. Traditionnellement, ce flot de conception est divisé en deux activités séparées[23] (voir Figure 2.1) :

- 1. Développement du matériel

- 2. Développement du logiciel

Le développement du matériel débute par la définition de sa description RTL en utilisant un langage de description de matériel (HDL) tel que VHDL ou Verilog. Le modèle RTL développé est soumis à la vérification fonctionnelle par simulation afin de valider son comportement sur des jeux de tests. Ensuite vient la phase de la synthèse physique qui prend comme entrée le modèle RTL, puis génère une description en termes de portes logiques. Cette description est ensuite utilisée par des outils de placement et routage afin de génèrer la topologie du masque sur laquelle va se baser la fabrication d'un prototype physique du système.

L'autre activité dans le flot de conception est le développement du logiciel. Bien que le codage du logiciel puisse se faire en parallèle avec le matériel, la validation du comportement du logiciel ne peut se faire qu'une fois que le prototype physique a été généré. Si une erreur est détectée dans le matériel ou le logiciel, le flot de conception doit alors être répété jusqu'à l'obtention d'un système fonctionnellement correct et exhibant les performances requises. À ce moment le système est prêt à entrer dans le processus de fabrication.

Étant donné la complexité actuelle des systèmes sur puce et la nécessité de réduire le temps de leur mise en marché, le flot de conception classique n'est plus acceptable. Voici deux facteurs principaux expliquant l'obsolescence de ce flot de conception.

1. Validation du logiciel: Le développement du logiciel, spécialement le débogage et la validation, ne peut avoir lieu que si celui-ci s'exécute sur sa plateforme cible. Un prototype physique est utilisé comme point d'entrée pour la validation du logiciel. L'inconvénient majeur de cette approche est que le prototype n'est disponible qu'à la fin du cycle de développement de la plateforme matérielle cible. Ceci, non seulement accroît le temps de mise en marché du produit final, mais nécessite aussi la création d'un nouveau prototype si une erreur est détectée au niveau du matériel suite à l'exécution du logiciel. Ceci est un processus très couteux nécessitant des équipements chers.

La covérification matériel/logiciel[16] peut aussi être utilisée afin de simuler

le logiciel avec le modèle RTL de la plateforme. Cependant, il faut encore attendre assez longtemps avant que le modèle RTL soit prêt. En plus, la covérification est exécutée à la vitesse faible du RTL. Par conséquent, seulement de petites portions du code logiciel peuvent être simulées, par exemple, pour débugger le pilote logiciel d'un périphérique matériel.

Grâce à la capacité croissante des circuits intégrés, un système sur puce complexe peut contenir une plateforme multicœur ayant des processeurs multiples. Ainsi, le logiciel est utilisé pour réaliser une grande partie de la fonction globale d'un SOC, vu que son temps de développement est très inférieur à celui du matériel exécutant la même fonction. En plus, le logiciel fournit une plus grande flexibilité face à l'évolution du système, que ce soit en cours de développement ou après la mise sur le marché. Par exemple, si une nouvelle version d'une norme doit être prise en compte, il est possible de fournir une mise à jour du logiciel que l'utilisateur peut télécharger. Toutefois, afin de pouvoir profiter de ces avantages que le logiciel offre par rapport au matériel, il faut pouvoir commencer à développer et vérifier une forte proportion du logiciel beaucoup plus tôt dans le cycle de développement du système sans devoir attendre la plateforme RTL ou le prototype. En plus, il importe que le logiciel puisse être simulé à une vitesse supérieure que celle obtenue par la méthode de covérification.

2. Exploration architecturale: Les systèmes sur puce contiennent aujourd'hui plusieurs IP, tels qu'un ou plusieurs processeurs, DSP, mémoires, périphériques, etc. Ces IP communiquent à travers un ou plusieurs bus. La configuration de ces bus ainsi que le choix des protocoles influent considérablement sur les performances [3]. Les architectures à bus partagés, tels que OCP, AMBA et CoreConnect, constituent des choix populaires pour les systèmes sur puce. Ils permettent un espace d'exploration large vu qu'ils peuvent être configurés de différentes manières. Ainsi, le concepteur du système peut explorer différents protocoles de communication et plusieurs configurations afin de faire le choix d'une architecture à adopter en vue de répondre aux

exigences de performance. L'utilisation d'un modèle RTL pour explorer plusieurs types d'architectures est impraticable, dû à ses temps de simulation trop longs.

Un autre point auquel le flot de conception classique ne peut pas répondre est l'exploration architecturale que l'on effectue pour décider des fonctionnalités qui seront implémentées en logiciel et celles qui seront implémentées en matériel. Le matériel permet généralement d'avoir de meilleures performances comparées au logiciel. Le processus de développement du matériel est toutefois plus long et plus coûteux que celui du logiciel. Il faut cependant rappeler que les systèmes sur puce sont soumis à des contraintes de temps réel que le logiciel ne pourrait satisfaire à lui seul. Ainsi, les fonctionnalités ciblées par des contraintes de performance sont implémentées en matériel alors que les autres fonctionnalités sont écrites en logiciel. On appelle partitionnement matériel/logiciel[10] le problème délicat qui consiste à trouver la bonne architecture, c'est-à dire celle possédant les performances requises et développée au moindre coût.

## 2.2 Modélisation au niveau transaction (TLM)

Afin de faire face à la complexité croissante des systèmes sur puce et répondre aux exigences présentées plus haut, le point d'entrée du flot de conception doit être élevé à un niveau plus haut que RTL, d'où vient le terme « conception au niveau système » (SLD : System Level Design). Durant ces 10 dernières années, la conception au niveau système a eu un grand intérêt pour une nouvelle méthodologie de conception, connue sous le nom de modélisation au niveau transaction (TLM : Transaction-Level Modeling)[14]. Le principe fondamental de TLM est de pouvoir modéliser seulement le niveau de détail qui est nécessaire pour une tâche particulière en cours du cycle de développement. Ce niveau de détail est caractérisé par son degré de précision par rapport à une implémentation réelle du système. Plusieurs aspects permettent de déterminer le niveau de précision d'un modèle[25]. Voici les deux aspects principaux utilisés dans TLM.

- Aspect structurel : C'est le degré auquel le modèle reflète la structure concrète de l'implémentation. Ceci dépend de plusieurs facteurs. Par exemple :

- o Si le partitionnement matériel et logiciel est déjà défini.

- Si les modules matériels et logiciels de l'implémentation sont représentés.

- Pour les modèles matériels, si les signaux et les broches de l'implémentation sont reflétés dans le modèle.

- Pour les modèles logiciels, si la communication entre tâches a été raffinée au niveau des mécanismes de communication fournis par le système d'exploitation temps réel (RTOS) utilisé dans l'implémentation.

- Pour la communication, si le protocole de communication de l'implémentation est spécifié.

- Aspect temporel : C'est le degré auquel le modèle représente le temps de calcul réel de l'implémentation. Trois niveaux de temps sont généralement distingués sur un modèle particulier :

- Modèle Un-timed: C'est un modèle où la notion de temps n'existe pas.

- Modèle Approximate-timed : C'est un modèle qui possède la notion de temps afin de représenter une estimation du temps d'exécution réel de l'implémentation.

- *Modèle Cycle-timed*: C'est le modèle le plus précis qui détermine exactement le temps d'exécution réel de l'implémentation en nombre de cycles d'horloges.

La méthodologie basée sur TLM n'est pas unique et plusieurs modèles transactionnels ont été définis[23, 14, 25, 51] selon leurs degrés de précision temporelle et structurelle. Dans ce qui suit, nous allons donner un aperçu de TLM en identifiant les concepts communs qui l'entourent.

Le premier concept sur lequel est basé le TLM est le suivant : la communication entre les composants qui constituent un système sur puce et la fonctionnalité de ces composants peuvent être développées et raffinées indépendamment. Ainsi, dans un modèle TLM, les communications telles que FIFO ou bus sont modélisées par des canaux et les composants tels que contrôleurs, processeurs, DSP, sont modélisés par des modules. Les modules communiquent entre eux en faisant appel à des fonctions d'interfaces exposées par les canaux. Ces appels d'interface sont appelés transactions, d'où vient le terme TLM. La modélisation de la fonctionnalité des composants ainsi que la communication entre eux passe par trois niveaux d'abstraction :

- 1. Niveau fonctionnel : C'est le plus haut niveau d'abstraction. Il décrit la fonctionnalité du système sans donner aucun détail d'implémentation temporel ou structurel. Par conséquent, un tel modèle n'a aucune notion de composant matériel ou logiciel et l'architecture du SOC n'est pas encore représentée.

- 2. **Niveau d'architecture :** Une fois que la fonctionnalité du système est définie, la phase suivante consiste à spécifier l'architecture de la plateforme. Ce niveau doit avoir un degré de précision structurelle suffisant afin de pouvoir commencer à développer et valider le logiciel.

- 3. Niveau microarchitecture : Ce niveau capture toute l'information qui permet une simulation niveau Cycle-timed. Le matériel est spécifié par sa description RTL alors que le logiciel est spécifié par le jeu d'instructions du processeur cible. Ce modèle est le point d'entrée des outils de synthèse physique.

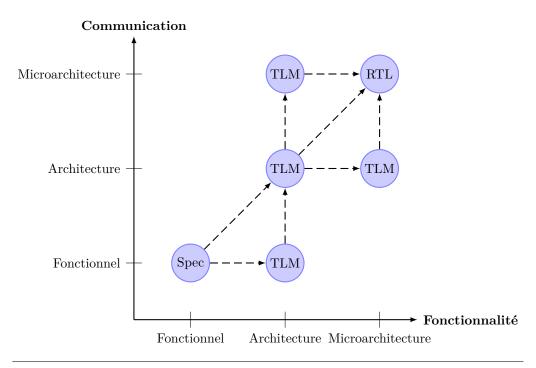

La Figure 2.2 illustre les différents modèles qui peuvent être utilisés durant le cycle de développement en considérant les trois niveaux d'abstraction cités plus haut, ainsi que la séparation entre communication et fonctionnalité.

Les deux modèles extrêmes dans le flot de conception sont le modèle fonctionnel et le modèle RTL.

• Modèle fonctionnel : appelé aussi modèle algorithmique [23] ou modèle de spécification [14]. C'est une spécification exécutable décrivant la fonctionna-

Figure 2.2 Modèles TLM

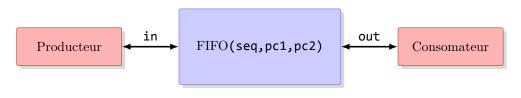

lité du système sans détail de l'architecture. Ce modèle est souvent décrit par un ensemble de processus qui communiquent entre eux à travers des variables partagées ou par des canaux de passage de messages tels que des FIFO. Par exemple, un système orienté traitement numérique de signal, va avoir un modèle de flux de données simulable, où les traitements sont représentés par des processus qui communiquent à travers des FIFO.

• Modèle RTL: Un modèle RTL décrit le comportement d'un circuit synchrone en spécifiant deux sortes d'éléments: registres et logique combinatoire. Les registres sont les composants qui contiennent les données. La logique combinatoire spécifie toutes les fonctions logiques d'un circuit. Ces fonctions prennent en entrée les données stockées dans un ou plusieurs registres et calculent les valeurs de sortie vers ces registres. La mise à jour des registres est synchronisée et n'aura lieu qu'au moment où un signal horloge (ou plusieurs) est activé. Ce modèle décrit toute la microarchitecture au cycle près.

Le flot de conception entre le modèle fonctionnel et le modèle RTL peut passer par plusieurs modèles intermédiaires. Le point commun entre ces modèles intermédiaires est que l'architecture de la plateforme cible est déjà spécifiée avec des degrés de précision structurels différents. Tous ces modèles sont considérés comme étant des modèles TLM[14]. D'un autre côté, ils peuvent refléter certains degrés de précision temporelle qui, par conséquent, vont engendrer d'autres niveaux d'abstraction. Ces modèles TLM ne sont pas nécessairement tous utilisés durant le cycle de développement. Ceci dépend considérablement des techniques utilisées et de la complexité du système à développer[14]. Dans ce qui suit, nous allons donner une vue globale sur l'utilité des modèles TLM, et montrer comment ils répondent aux besoins cités dans la section précédente.

#### Développement du logiciel au tout début

Dès que la spécification du système a été complétée, le développement de la plateforme TLM commence. Ainsi, la plateforme cible sera disponible pour le développement du logiciel très tôt dans le cycle de développement. Ceci permet d'avoir une méthodologique de conception matériel/logiciel concurrente où le développement du logiciel se fait en parallèle avec le matériel. En effet, les développeurs de logiciels regardent la plateforme TLM comme le modèle de référence pour exécuter et valider leurs codes logiciels, alors que les développeurs du matériel la considèrent comme le modèle de départ pour entamer le développement de la plateforme RTL. Vis-à-vis du développement logiciel, la plateforme TLM est utilisée pour les deux objectifs suivants :

• la validation de la fonctionnalité logicielle en utilisant une plateforme TLM non temporelle. Ceci correspond au modèle d'architecture TLM de la Figure 2 où l'architecture est décrite au niveau fonctionnalité et communication. Les détails sur la microarchitecture sont ignorés. Par exemple, les détails sur le protocole de bus et la microarchitecture pipeline, n'influent pas sur la fonctionnalité et ne sont pas précisés à ce niveau d'abstraction. Ceci a pour avantage d'avoir une rapidité de simulation suffisante pour pouvoir dérouler le logiciel et le valider.

• L'optimisation de certaines fonctionnalités logicielles soumises à des contraintes temporelles en utilisant un modèle TLM temporisé. Dans ce cas, le modèle d'architecture va être annoté par des délais approximatifs afin de pouvoir estimer le temps d'exécution de la plateforme cible. Il est parfois nécessaire d'avoir un temps d'exécution précis. Ainsi, certaines fonctionnalités au niveau des composants ou de la communication vont être raffinées au niveau microarchitecture afin d'obtenir un modèle cycle-timed. Ces modèles temporels sont aussi utilisés afin d'estimer les performances et faire de l'exploration architecturale.

#### Exploration architecturale

Durant les premières phases du cycle de développement, il est nécessaire de définir l'architecture qui convient au mieux aux besoins et qui satisfait les contraintes de performance exigées. En raison de sa rapidité de simulation, TLM donne la possibilité d'analyser plusieurs architectures du système, une fois la spécification fonctionnelle du système est complétée. Ainsi, le concepteur a les moyens de décider sur le bon partitionnement matériel/logiciel, la topologie de la communication, les types des bus et des processeurs à utiliser, etc. Afin de pouvoir estimer les performances du système, le modèle TLM doit inclure des informations sur le temps d'exécution. Ces informations de temps peuvent être extraites à la suite de conduites de tests de performance ou à partir des modèles RTL de certains IP déjà développés et qui vont être réutilisés dans le système courant [51].

Dans cette section, nous avons présenté les concepts fondamentaux entourant la méthodologie de conception basée sur TLM. Cependant, il est nécessaire d'avoir les outils et les techniques nécessaires afin de mettre en pratique cette méthodologie et ainsi profiter de tous les avantages qu'elle peut apporter. Aujourd'hui, le standard utilisé dans la conception des systèmes sur puce en se basant sur la méthodologie TLM est SystemC. Dans la prochaine section, nous allons donner un aperçu de SystemC et de ses limitations qui constituent un obstacle pour répondre aux nouveaux besoins des systèmes sur puce.

# 2.3 SystemC et ses limitations

Plusieurs systèmes et langages ont émergé afin de résoudre plusieurs aspects de la conception des systèmes sur puce. Par exemple, les langages de description de matériel tels que VHDL et Verilog sont utilisés pour simuler et synthétiser les circuits numériques. C/C++ est le langage principal utilisé pour développer les logiciel embarqués. PSL et SVA sont utilisés pour la vérification fonctionnelle des modèles RTL. SystemVerilog, une extension de Verilog, élève le niveau d'abstraction pour la description du matériel en ajoutant des structures orientées objets en permettant la synthèse comportementale. Bluespec et Esterel permettent la génération d'un modèle RTL à partir d'une description matérielle à un plus haut niveau d'abstraction. Matlab est souvent utilisé pour la spécification des besoins et le développement des algorithmes de traitement de messages.

Chacun de ces langages a un rôle particulier au cours de cycle de développement. Cependant, la complexité croissante des systèmes sur puce nécessite entre autres :

- La disponibilité d'un système de modélisation fiable qui permet d'assister les concepteurs durant tout le cycle de développement en commençant à un niveau d'abstraction système.

- Pouvoir échanger entre compagnies des IP écrits à un niveau d'abstraction système. Pour cela il faut que les compagnies adoptent le même langage de modélisation.

Grâce à l'organisme OSCI (Open SystemC Initiative), composé de plusieurs compagnies industrielles, le langage SystemC a pris naissance en 1999, et en 2005 il est devenu une norme IEEE. SystemC n'est pas la meilleure solution pour tous les aspects de conception, cependant il unit plusieurs caractéristiques qui manquent dans d'autres langages. Voici quelques unes.

• La spécification et la modélisation à plusieurs niveaux d'abstraction, commençant par un modèle purement fonctionnel jusqu'à un modèle RTL.

- Des mécanismes qui séparent la fonctionnalité du système de sa communication, permettant ainsi l'adoption de la méthodologie TLM.

- La notion de temps afin de pouvoir estimer les performances et explorer plusieurs alternatives.

- Avoir un seul langage de conception pour modéliser le matériel et le logiciel afin de faciliter le codesign matériel/logiciel et d'accélérer la simulation.

Nous commençons par introduire la structure d'un modèle SystemC et son modèle d'exécution évènementiel. Ensuite, nous présentons les limitations de SystemC qui sont dues principalement à ce modèle de calcul.

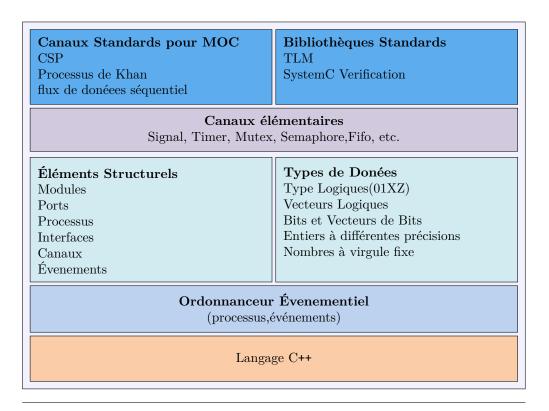

#### 2.3.1 Vue d'ensemble

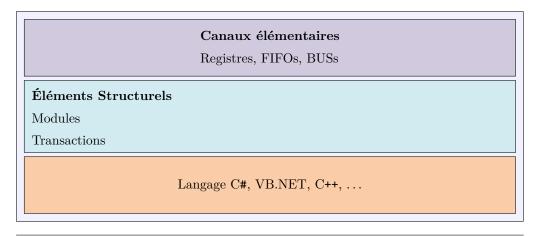

SystemC utilise une approche en couches qui permet une grande flexibilité afin d'introduire de nouvelles structures qui partagent le même noyau de simulation. Ce noyau de simulation est la couche de base de SystemC. Il est basé sur un ordonnanceur événementiel qui travaille avec les processus et les évènements d'une manière abstraite. Il contrôle les événements et l'ordonnancement des processus sans avoir connaissance de ce que les évènements représentent ou de ce que font les processus. Ensuite vient la couche des éléments structurels qui permet de spécifier la structure des modèles. Un modèle SystemC est composé d'un ou plusieurs modules. Ces modules communiquent avec d'autres modules à travers des ports reliés à des canaux de communications. Les ports exposent des interfaces qui sont implémentées par les canaux. De cette manière, il est possible d'analyser plusieurs types de canaux implémentant la même interface sans avoir à modifier les modules communicants. Un module peut avoir un ou plusieurs processus qui décrivent sa fonctionnalité. La synchronisation entre processus se fait par notification et attente d'évènements. Au-dessus de cette couche sont définis des canaux standards ainsi que des canaux spécifiques à des modèles de calcul. On retrouve aussi la bibliothèque TLM et la bibliothèque de vérification. SystemC définit un ensemble de types de données qui sont utiles pour les modèles matériels et certains types

d'applications logicielles. À titre d'exemple, il y a le type fixed-point pour les applications DSP (Data Signal Processing).

La Figure 2.3 représente les différentes couches de SystemC. La couche de fond montre que SystemC n'est pas un langage à lui seul, mais il s'agit d'une bibliothèque fondée entièrement en C++. C'est-à-dire que n'importe quel programme écrit en SystemC peut être compilé avec un compilateur C++ afin de générer un programme exécutable.

Figure 2.3 Architecture du langage SystemC

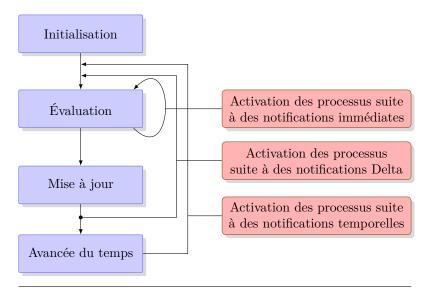

L'algorithme d'ordonnancement de SystemC se base sur un modèle d'exécution événementiel. Il distingue trois types de notification d'évènements : la notification immédiate, la notification delta et la notification temporelle. La coordination et la synchronisation entre les processus suite à ces trois types de notification sont gérées par l'ordonnanceur de SystemC dont les trois phases d'exécution sont représentées dans la Figure 2.4.

Phase d'initialisation: Pendant la phase d'initialisation, chaque processus est

Figure 2.4 Modèle d'exécution de SystemC

exécuté une fois jusqu'à sa suspension. Un processus est suspendu lorsqu'il appelle la fonction wait, indiquant ainsi qu'il passe en mode attente en passant la main à l'ordonnanceur. Il y a trois types d'attentes : attente de la notification d'un événement, attente du prochain cycle delta, ou attente temporelle définie par une durée de temps discret.

Phase d'évaluation: Après la phase d'initialisation, l'ordonnanceur commence la phase d'évaluation en exécutant séquentiellement dans un ordre indéterminé la liste des processus prêts à être exécutés. Durant cette phase, un processus pourrait générer une notification d'évènement immédiate. Ainsi, d'autres processus sensibles à cet évènement sont ajoutés à la liste des processus prêts à être exécutés. Ces nouveaux processus seront exécutés dans la même phase d'évaluation. Une fois que la liste des processus prêts à être exécutés est vide, l'ordonnanceur passe à la phase de mise à jour.

Phase de mise à jour : La phase de mise à jour permet d'implémenter la sémantique de demander-actualiser (request-update) permettant d'ajourner l'actualisation de l'état du système une fois que la phase d'évaluation est terminée. La combinaison de la phase d'évaluation et de la phase de mise

à jour forme un delta-cycle. Ainsi, à la fin du delta-cycle, l'ordonnanceur vérifie s'il existe des notifications delta en instance. Si c'est le cas alors, l'ordonnanceur enregistre tous les processus en attente de l'occurrence de ces évènements dans une liste de processus prêts à être exécutés puis recommence un nouveau delta-cycle en exécutant encore une fois la phase d'évaluation.

Avancée du temps : Quand il n'existe plus de notification delta, l'ordonnanceur avance le temps à la plus proche notification temporelle (dû à une attente temporelle), détermine les processus à être exécutés durant cet instant de temps, puis recommence l'exécution des trois phases d'ordonnancement correspondant à un nouveau temps de simulation.

#### 2.3.2 Limitations de SystemC

Dans ce que suit nous présentons les inconvénients majeurs de SystemC selon plusieurs aspects de conception.

#### 2.3.2.1 Modélisation

SystemC ne rend pas la tâche de modélisation très différente de celle d'un langage de description du matériel (HDL) tel que VHDL ou Verilog. Ceci est dû au fait que la sémantique du langage ne diffère pas de celle d'un langage HDL qui est basé sur un modèle de calcul événementiel. En effet, à part la notification immédiate qui a été ajoutée à la version 2.0 de SystemC, les deux types de langages se basent sur la même notion de delta-cycle et des notifications d'événement pour la synchronisation entre processus. Par conséquent, les mêmes difficultés rencontrées, au niveau des langages HDL, pour gérer les accès concurrents à des ressources partagées sont aussi présentes dans SystemC[52]. D'un autre côté, même au niveau TLM et plus haut, SystemC utilise le même modèle de calcul augmenté des notifications immédiates. Comme nous allons voir dans la section 3.1, avec la complexité croissante des systèmes qui nécessite de plus en plus de processus parallèles, l'utilisation de ces mécanismes de synchronisation devient de plus en plus complexe et le risque d'erreurs est élevé.

Un autre problème qui peut survenir lors de la modélisation d'un système SystemC est l'interblocage dû à l'ordre d'exécution des processus. En effet, lors de la phase d'évaluation, l'ordre des processus est arbitraire. Cependant pour une implémentation particulière de SystemC et pour un même stimulus l'ordre des processus est toujours le même. Par conséquent, la simulation de certains modèles génère des résultats corrects dans une implémentation particulière de SystemC, alors que le modèle exhibe certaines défaillances fonctionnelles. L'exemple 2.1 illustre ce problème dû à l'emploi des notifications immédiates.

Exemple 2.1 Interblocage dû aux notifications immédiates

```

writer = new producer("Writer") // line 1

reader = new reader("Reader") // line 2

void read(){

void write() {

while(true)

while(true)

wait(write_event);

value = ComputeNewValue();

ConsumeValue(value);

write_event.notify();

read_event.notify();

wait(read_event);

}

}

}

}

```

Si l'ordonnanceur exécute le processus writer en premier, alors la notification immédiate de l'événement write\_event est perdue puisqu'aucun processus n'est en attente de cet évènement lors de son occurrence. Ceci mène à un interblocage où le modèle est suspendu indéfiniment. Cependant, si le processus « reader » s'exécute en premier, il sera suspendu en attente de la notification de l'événement write\_event et ainsi, quand le processus writer s'exécute, l'événement write\_event est notifié, permettant au processus reader de continuer son exécution et le cycle write-read continuera indéfiniment. Remarquer qu'il est possible d'influencer l'ordre d'exécution des processus en interchangeant les déclarations des processus writer et reader dans les lignes 1 et 2 du présent exemple. Ce genre d'erreur dû au non-déterminisme dans l'ordre

d'exécution des processus, pourtant fixe pour une implémentation particulière de SystemC, peut mener à une implémentation incorrecte du modèle dont la simulation a donné des résultats corrects.

$\Diamond$

Pour éliminer le comportement indésirable induit par le non-déterminisme qui est dû à l'utilisation des notifications immédiates, la plupart des canaux standards de SystemC, incluant sc\_fifo, se basent sur la sémantique request-update et le concept de delta-cycle expliqués plus haut[34]. En effet, si nous remplaçons les deux notifications immédiates, dans l'exemple 2.1, par des notifications delta, notify(SC\_ZERO\_TIME) (voir Exemple 2.2), nous obtenons un comportement déterministe indépendant de l'ordre d'exécution des processus. Cependant, une telle synchronisation implicite entre processus imposée dans chaque delta-cycle est très restrictive comparée à une synchronisation effective entre processus parallèles dans une application logicielle multitâches ou dans un circuit asynchrone[37].

Exemple 2.2 Interblocage résolu par notifications delta-cycle

```

writer = new producer("Writer") // line 1

reader = new reader("Reader") // line 2

void write() {

void read(){

while(true)

while(true)

wait(write_event);

value = ComputeNewValue();

ConsumeValue(value);

write_event.

read event.

notify(SC ZERO TIME);

notify(SC_ZERO_TIME);

wait(read_event);

}

}

}

}

```

D'un autre côté, un comportement non déterministe n'est pas toujours dû à des

erreurs de synchronisation, mais il peut être spécifié intentionnellement. En effet, la modélisation d'un système à un niveau très haut d'abstraction est par nature non déterministe puisque plusieurs détails d'implémentation sont abstraits. Par exemple, prenons le cas où plusieurs maîtres accèdent à un bus concurremment. Au point de vue de l'implémentation, cet accès concurrent est géré par un arbitre et des priorités d'accès. Cependant, au niveau système, l'ordre de priorité n'est pas encore spécifié. Autrement dit, quel que soit l'ordre d'exécution, il faut que la fonctionnalité du système soit correcte. Permettre un ordre aléatoire en cours de simulation ne résout pas le problème. Les travaux dans [29] et [38] adressent ce problème en générant plusieurs ordonnancements possibles en cours de simulation. Des techniques de réduction d'ordre partiel sont utilisés afin d'éliminer les ordonnancements qui ont les mêmes effets sur le comportement du système. Ces travaux permettent d'avoir une meilleure couverture de test, cependant l'impact sur le temps de simulation est considérable.

#### 2.3.2.2 Vérification par raffinement et sémantique formelle

Bien que SystemC permette la modélisation à plusieurs niveaux d'abstraction système, le flot pour passer d'un niveau d'abstraction à un autre est géré dans la plupart des cas manuellement. Par conséquent, à chaque niveau d'abstraction, il faut revérifier la fonctionnalité du système afin d'assurer qu'elle est conforme aux spécifications initiales. D'un autre côté, les techniques utilisées pour la vérification fonctionnelle sont essentiellement basées sur la simulation. Cependant, l'inconvénient majeur de la simulation est qu'elle permet seulement une faible couverture même avec un temps de simulation extrêmement long. Comme il a été indiqué par ITRS, les défis actuels sont centrés autour de comment rendre les techniques de vérification formelle plus fiables et plus contrôlables. En dépit, des activités intensives dans le développement des techniques de vérification pour le logiciel et le matériel, étendre ces techniques à SystemC est un considérable défi[60]. En effet, plusieurs travaux ont essayé de donner une sémantique formelle à SystemC en le transformant à un langage formel tel que ASM[26], Promela[59], SMV[56] afin d'appliquer les techniques de «Model Checking». Toutefois, ces travaux traitent

seulement un sous-ensemble de SystemC. Cette difficulté est due essentiellement à la nature orientée objet de SystemC et à son modèle de calcul complexe.

#### 2.3.2.3 Vitesse de simulation

Grâce à la méthodologie basée sur TLM, la vitesse de simulation est considérablement améliorée, permettant ainsi d'explorer plusieurs architectures et de pouvoir valider le logiciel[23]. Cependant, cette vitesse doit être maintenue au même taux de complexité que les systèmes sur puce. La disponibilité croissante des machines multicœurs est la tendance actuelle afin d'accélérer le temps de simulation. Toutefois, la complexité du langage SystemC rend la parallélisation de la simulation assez difficile.

En effet, le modèle de concurrence de l'ordonnanceur de SystemC repose sur la sémantique de coroutine. Voici la description de cette sémantique comme décrite dans [34] :

"Since process instances execute without interruption, only a single process instance can be running at any one time, and no other process instance can execute until the currently executing process instance has yielded control to the kernel. A process shall not pre-empt or interrupt the execution of another process. This is known as co-routine semantics or co-operative multitasking".

Ainsi, chaque processus s'exécute sans interruption jusqu'à ce qu'il cède la main à un autre processus, à la suite de l'appel à la fonction wait, à partir de ce moment il reste suspendu jusqu'à sa prochaine exécution. Par conséquent, une manière directe de respecter cette sémantique est d'exécuter les processus séquentiellement. En fait, c'est cette exécution séquentielle qui est implémentée dans le simulateur de référence de SystemC. Il est toujours possible de concevoir une implémentation du simulateur qui profite d'une machine multicœur en exécutant les processus d'une manière concurrente à condition que le comportement apparaisse identique à la sémantique de coroutine. En d'autres termes, une analyse complexe des processus et de leurs dépendances est nécessaire pour une simulation multicœur d'un modèle SystemC. Plusieurs travaux[20, 22, 55, 47] ont essayé de paralléliser le simulateur de SystemC. Cependant vu la complexité du langage, seulement un