#### Direction des bibliothèques

#### **AVIS**

Ce document a été numérisé par la Division de la gestion des documents et des archives de l'Université de Montréal.

L'auteur a autorisé l'Université de Montréal à reproduire et diffuser, en totalité ou en partie, par quelque moyen que ce soit et sur quelque support que ce soit, et exclusivement à des fins non lucratives d'enseignement et de recherche, des copies de ce mémoire ou de cette thèse.

L'auteur et les coauteurs le cas échéant conservent la propriété du droit d'auteur et des droits moraux qui protègent ce document. Ni la thèse ou le mémoire, ni des extraits substantiels de ce document, ne doivent être imprimés ou autrement reproduits sans l'autorisation de l'auteur.

Afin de se conformer à la Loi canadienne sur la protection des renseignements personnels, quelques formulaires secondaires, coordonnées ou signatures intégrées au texte ont pu être enlevés de ce document. Bien que cela ait pu affecter la pagination, il n'y a aucun contenu manquant.

#### NOTICE

This document was digitized by the Records Management & Archives Division of Université de Montréal.

The author of this thesis or dissertation has granted a nonexclusive license allowing Université de Montréal to reproduce and publish the document, in part or in whole, and in any format, solely for noncommercial educational and research purposes.

The author and co-authors if applicable retain copyright ownership and moral rights in this document. Neither the whole thesis or dissertation, nor substantial extracts from it, may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms, contact information or signatures may have been removed from the document. While this may affect the document page count, it does not represent any loss of content from the document.

#### Université de Montréal

Nouvelles approches pour la conception d'outils CAO pour le domaine des systèmes embarqués

Par

#### James Lapalme

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences - Secteur des sciences

Thèse présentée à la Faculté des études supérieures en vue de l'obtention du grade de Doctorat en Informatique

Février, 2009

© James Lapalme, 2009

DA 76 USY 2009 VO13

# Université de Montréal Faculté des études supérieures

#### Cette thèse intitulée:

Nouvelles approches pour la conception d'outils CAO pour le domaine des systèmes embarqués

présenté par :

James Lapalme

a été évaluée par un jury composé des personnes suivantes :

Dr. Houari Sahraoui président-rapporteur

Dr. El Mostapha Aboulhamid directeur de recherche

Dre. Gabriela Nicolescu codirectrice de recherche

Dr. Claude Frasson membre du jury

Dr. Ahmed Jerraya examinateur externe

Dr. Thierry Bardini représentant du doyen de la FES

# Résumé

Notre société de consommation exerce des pressions énormes sur l'industrie des systèmes embarqués. Ces pressions sont causées en grande partie par des attentes souvent contradictoires et difficilement conciliables. Afin de répondre à la situation, l'industrie fait évoluer de manière fulgurante les techniques et les processus de fabrication des systèmes électroniques. Malgré cette évolution, un gouffre important sépare notre capacité d'intégrer des transistors et notre habileté pour la conception de systèmes les utilisant de façon efficace. Ce gouffre ne fait qu'exacerber les difficultés de l'industrie à répondre aux exigences du marché. Les outils CAO sont un moyen prometteur pour combler ce gouffre. L'efficacité de ces outils est un critère important pour leur réussite et peut être grandement influencée par les technologies et les approches de conception utilisées pour leur réalisation. La communauté du logiciel a développé plusieurs technologies et approches pouvant servir à l'élaboration des outils CAO.

Ce travail présente des idées innovatrices pour la conception et la réalisation d'outils CAO. Ces idées s'appuient sur l'utilisation de technologies modernes provenant de la communauté du logiciel. Les technologies principales qui seront abordées dans le cadre de ce travail sont la plateforme .Net, le Web Sémantique, la conception dirigée par les modèles et les patrons de conception. Ce travail présente aussi plusieurs réalisations afin d'appuyer les idées proposées.

Mots clés : système embarqué, .Net, Web Sémantique, CAO, conception dirigée par les modèles, Y-Chart

# **Summary**

Our society of consumption exerts enormous pressures on the embedded systems industry. These pressures are mainly due to expectations which are often contradictory and not easily reconcilable. In order to cope with the situation, the industry has rapidly developed and evolved techniques and manufacturing processes for electronic systems. In spite of this evolution, an important gap exists between our capacity to integrate transistors and our systems design capabilities to use these transistors effectively. This gap does nothing but exacerbate the difficulties of industries to fulfill the expectations of the market. CAD tools are a promising means to cross this gap. The effectiveness of these tools is an important criterion for their success. Their effectiveness is largely influenced by the technologies and the design approaches used for their implementation. The software community has developed several technologies and approaches which can be greatly beneficial to CAD tools development. This thesis presents innovative ideas for the design and the realization of CAD tools. These ideas are based on the use of modern software technologies. Several accomplishments will also be presented which support these ideas. The main technologies that will be discussed within this work are the Net platform, the Semantic Web, model-driven design\development and design patterns.

Key words: embedded systems. Net, Semantic Web, CAD, model-driven design, Y-Chart

# Table des matières

| Résumé             |                                                                        | i    |

|--------------------|------------------------------------------------------------------------|------|

| RésuméSummary      |                                                                        |      |

| Table des matières |                                                                        | v    |

| Liste des figures  |                                                                        | _vii |

| Liste des          | abréviations                                                           | _ ix |

| Remerci            | ements                                                                 | _ xi |

| Introduc           | ction                                                                  | 1    |

| 1.1                | La conception assistée par ordinateur                                  | 4    |

| 1.2                | Les technologies modernes du logiciel                                  | 5    |

| 1.3                | Motivations                                                            | 6    |

| 1.4                | Contribution et l'organisation                                         | 7    |

| Revue de           | e la littérature                                                       | 9    |

| 1.5                | Les SDL                                                                | _10  |

| 1.5.1              | Les HDL/SDL indépendants                                               | 10   |

| 1.5.2              | 2 HDL/SDL orientés bibliothèques                                       | _12  |

| 1.6                | Les méthodologies                                                      | _14  |

| 1.6.1              | L'élaboration par raffinements successifs                              | _ 14 |

| 1.6.2              | La conception à base d'IP                                              | _17  |

| 1.6.3              | B Le paradigme « Y-Chart »                                             | 18   |

| 1.7                | Les nouveaux défis                                                     | _19  |

| Le parad           | ligme « Y-Chart » : une discussion sur le développement dirigé par les |      |

| modèles            |                                                                        | 21   |

| Une nouvelle méthodologie pour la conce   | ption d'outils CAO             | 57            |

|-------------------------------------------|--------------------------------|---------------|

| La séparation des aspects de modélisation | et de simulation dans les lan  | gages         |

| orientés-« framework » de modélisation m  | atériel/logiciel               | 85            |

| L'impact du Web sémantique sur la conce   | ption des systèmes assistée po | ar ordinateur |

|                                           |                                | 109           |

| Conclusion et Travaux Futurs              |                                | 151           |

| 1.8 Développements possibles              |                                | 154           |

| Sources documentaires                     |                                | 157           |

| Liste des contributions                   |                                | xvii          |

# Liste des figures

| Figure 1 Système de guidage Autonetics D-17 du missile Minuteman I $\_$ |    |

|-------------------------------------------------------------------------|----|

| Figure 2 Systèmes embarqués modernes                                    |    |

| Figure 3 Gouffre de productivité                                        | 4  |

| Figure 4 Raffinements Successifs                                        |    |

| Figure 5 Y-Chart                                                        | 18 |

# Liste des abréviations

| CAD         | Computer Assisted Design                                          |

|-------------|-------------------------------------------------------------------|

| CAO         | Conception assistée par ordinateur                                |

| CIL         | Common Intermediate Language                                      |

| CLI         | Common Language Infrastructure                                    |

| CLS         | Common Language Specification                                     |

| CTS         | Common Type System                                                |

| <b>ECMA</b> | European Computer Manufacturers Association                       |

| EDA         | Electronic Design Automation                                      |

| <b>EDIF</b> | Electronic Design Interchange Format                              |

| <b>FIFO</b> | First In, First Out                                               |

| <b>FPGA</b> | Field-Programmable Gate Arrays                                    |

| HDL         | Hardware Description Language                                     |

| IC          | Integrated Circuit                                                |

| IEEE        | Institute of Electrical and Electronics Engineers                 |

| IP          | Intellectual Property                                             |

| ISO         | International Organization for Standardization                    |

| JVM         | Java Virtual Machine                                              |

| NOC         | Network On Chip                                                   |

| OOP         | Object-Oriented Programming                                       |

| OSCI        | Open SystemC Initiative                                           |

| PCB         | Printed Circuit Board                                             |

| RTL         | Register Transfer Level                                           |

| SCV         | SystemC Verification Library                                      |

| SDL         | System Description Language                                       |

| STOC        | SpecC Technology Open Consortium                                  |

| UCI         | University of California Irvin                                    |

| VES         | Virtual Execution system                                          |

| VHDL        | Very High Speed Integration circuit Hardware Description Language |

| <b>XML</b>  | Extensible Markup Language                                        |

## Remerciements

Je voudrais remercier Dr. El Mostapha Aboulhamid et Dre. Gabriela Nicolescu pour l'aide et l'encadrement dont ils m'ont fourni durant mes études de doctorat. Je voudrais tout particulièrement remercier Mostapha pour sa grande générosité et son appui quasi paternel qui m'ont aidé lors des moments plus difficile de ce parcours.

Je voudrais remercier profondément les personnes proches de moi qui n'ont jamais arrêté de croire en moi; dont leur encouragement et leur support ont été cruciaux à la réussite de ce travail (thx Mom, Dad and MJ).

En terminant, je voudrais remercier sincèrement Steven, Christian et Marie-Josée pour avoir participé à la correction de cette thèse et/ou pour avoir écouté mon « blabla » interminable sur le contenu de celle-ci... :0)

I would like to dedicate this to my mother and father who have always pushed me to better myself, and to Zachary, Jacob and Marie-Josée, the three loves of my life, without whom this would have no meaning

I would also like to dedicate this to my maternal grand-parents for their love

" I began this journey to understand the world around me.

I have learnt very little about it but have learnt a great deal about myself" – Anonymous

## Introduction

L'vie contemporain. Malgré leur omniprésence, la majorité de la population est ignorante du rôle important que joue ces petits systèmes cachés qui font fonctionner comme par magie, les nombreuses choses qui nous entourent. Juste en prenant une petite pause de la rédaction de ce texte, en regardant autour de moi, dans mon bureau, je peux percevoir rapidement une multitude d'items à l'apparence anodine contenant un système embarqué:

- imprimante

- routeur

- téléphone multifonctionnel

- thermostat électronique

- montre électronique

- téléphone cellulaire

Puisque le terme *système embarqué* est omniprésent dans ce texte et pour en faciliter la compréhension, voici une définition informelle permettant de mieux comprendre la portée et le sens du terme :

« Un système embarqué peut être défini comme un système électronique et informatique autonome, qui est dédié à une tâche bien précise. Ses ressources disponibles sont généralement limitées. Cette limitation est généralement d'ordre spatial (taille limitée) et énergétique (consommation restreinte). » (Wikipedia.)

Les systèmes embarqués ont évolué grandement depuis leur apparition initiale. La figure 1 présente un des premiers systèmes embarqués à être produit en série durant les années 60: le système de guidage pour le missile Minuteman 1.

Figure 1 Système de guidage Autonetics D-17 du missile Minuteman I

De nos jours, les systèmes embarqués sont plusieurs ordres de grandeur plus petits et supportent un très grand nombre de fonctionnalités. La figure 2 (à gauche) présente le ©iPod touch de Apple, un produit de consommation de masse très populaire, qui possède plusieurs fonctionnalités telles que le décodage vidéo, le décodage de musique, la communication réseautique sans-fils, etc. La figure 2 (à droite) illustre bien la taille de certains des plus petits systèmes embarqués pouvant être produits de nos jours : les Smartdusts motes. Les Smartdusts motes sont des systèmes micro-électro-mécaniques capables de communiquer via un réseau sans-fil. De plus, généralement, ils sont sensibles aux divers aspects de leur environnement : son, lumière, température, etc.

Figure 2 Systèmes embarqués modernes

Malgré l'évolution fulgurante des techniques et des processus de fabrication des systèmes électroniques (dont les systèmes embarqués), l'industrie de la microélectronique fait face à de grands enjeux afin de répondre aux attentes du marché. Notre société de consommation exerce des pressions énormes sur cette

industrie. Ces pressions sont causées en grande partie par des attentes souvent contradictoires ou difficilement conciliables. Le marché demande à la fois des produits avec de plus en plus de fonctionnalités, mais dont le coût d'achat est moindre et le temps de mise en marché plus court.

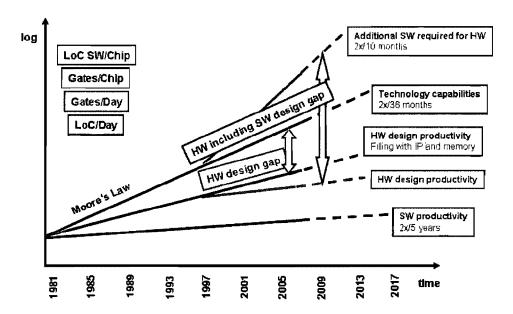

La loi de Moore [2], une loi fondée sur des extrapolations empiriques faites par Gordon Moore chez Intel, énonce « la quantité de transistors pouvant être intégrés par superficie sur une puce double approximative aux 2 ans ». Cette capacité d'intégration des transistors est due à l'amélioration continue des processus de fabrication. Cette capacité d'intégration croissante est un élément essentiel afin de pouvoir répondre aux besoins du marché. Néanmoins, elle n'est pas un critère suffisant.

Depuis plusieurs décennies maintenant, un fossé énorme se crée entre notre capacité d'intégrer des transistors et notre habileté pour la conception de systèmes les utilisant de façon efficace. La figure 3 illustre graphiquement ce fossé. La ligne noire représente la loi de Moore avec un niveau d'intégration doublant aux 36 mois. La ligne grise du bas représente l'évolution de la productivité de l'industrie en conception de système matériel. On peut percevoir un écart qui croit à un rythme exponentiel entre ces deux lignes. La figure 3 illustre aussi la croissance des besoins additionnels pour du logiciels spécifiques nécessaires au support des systèmes matériels. Cette croissance double aux 10 mois. Donc le vrai gouffre de productivité incluant les besoins de logiciel est énorme (la flèche rouge verticale).

Figure 3 Gouffre de productivité<sup>1</sup>

Les causes freinant la productivité sont grandement attribuables à la complexité du processus de conception des systèmes modernes, et de leur validation. Les grands aspects devant être maîtrisés pour vaincre ce gouffre sont [40]:

- la réutilisation;

- la vérification et le test;

- l'optimisation de la conception de système guidée par les coûts;

- la conception de logiciel embarqué;

- la robustesse des plateformes matérielles d'implémentation;

- la gestion du processus de conception.

La maîtrise du processus de conception des systèmes modernes requiert un grand éventail de techniques, d'outils et de méthodologies qui permettent d'établir de manière prévisible une transformation des exigences en un produit fini.

## 1.1 La conception assistée par ordinateur

Le domaine de la conception assistée par ordinateur (CAO) a comme cheval de bataille les grands enjeux entourant la conception des systèmes modernes dont les

-

<sup>&</sup>lt;sup>1</sup> Source ITRS 2007

systèmes embarqués. La CAO facilite la transformation d'exigences fonctionnelles en produits finis par l'utilisation d'outils informatisés supportant des techniques et des méthodologies de conception. Typiquement, cette assistance augmente de façon significative la productivité des concepteurs en offrant plusieurs fonctionnalités clés :

- la capture et la validation de besoins fonctionnelles;

- le raffinement des spécifications fonctionnelles en implémentation;

- l'exploration et l'analyse des implémentations alternatives;

- la vérification des implémentations.

Dans le passé, le domaine de la CAO a mis beaucoup l'accent sur la dimension outillage et a négligé celui de la méthodologie. Les outils CAO inflexibles au soutien de nouvelles méthodologies rendant ceux-ci mal adaptés et inefficaces sont une conséquence de cette négligence. Il est clair que la tendance des systèmes embarqués est de se complexifier en raison de leur capacité multifonctionnelle de plus en plus ciblée à un domaine précis, ainsi que leur conception incluant un nombre croissant de composantes hétérogènes (micromécanique, micro-optique, etc.). Afin de maintenir cette tendance, il est nécessaire d'avoir des méthodologies de conception éprouvées, efficaces et adaptées pour guider les concepteurs durant le cycle complet de mise en marché – du concept au produit fini testé. Les prochaines générations d'outils CAO se doivent d'être plus flexibles afin de répondre aux besoins méthodologiques.

#### 1.2 Les technologies modernes du logiciel

Parallèlement et indépendamment de l'industrie des systèmes embarqués, les domaines du logiciel et du génie logiciel ont évolué énormément au cours des 20 dernières années. Cette évolution est due aux mêmes facteurs de pression que subit l'industrie des systèmes embarqués : plus de fonctionnalités livrées à moindre coûts et en moins de temps. Afin de faciliter la création de logiciels de meilleure qualité et d'augmenter la productivité des développeurs, la communauté du logiciel a mis au point plusieurs technologies innovatrices. Quatre de ces grandes technologies sont :

- les langages et les plateformes de programmation modernes tel que C# et .Net [1][28];

- le développement à base de patron de conception [31];

- le développement dirigé par les modèles [45][11];

les technologies du Web sémantiques [10].

En plus de permettre le développement de logiciels de manière plus efficace, ces technologies permettent de produire de meilleurs logiciels étant souvent plus flexibles et adaptables. Puisque le domaine de la CAO est à la base un domaine axé sur le logiciel, ce domaine peut bénéficier grandement de l'utilisation des technologies mentionnées plus haut afin d'améliorer leur conception et leur degré de flexibilité. Donc l'utilisation du savoir faire du domaine du logiciel peut amener des solutions intéressantes aux problématiques de productivité du domaine des systèmes embarqués.

#### 1.3 Motivations

Les méthodologies de conceptions, les langages de description systèmes ainsi que les environnements de conception implémentant ces deux éléments sont des outils importants pour la conception des systèmes embarqués (ces éléments seront présentés davantage dans le prochain chapitre). Malgré les efforts investis pour l'avancement de ceux-ci, il n'existe pas encore de solutions parfaites. Plusieurs difficultés persistent :

- les environnements de conception ne supportent pas adéquatement les méthodologies; plusieurs discontinuités sont présentes.

- les environnements de conception permettent difficilement l'intégration d'outils tierce-partie afin de supporter des flux de conception personnalisés.

- les langages hôtes utilisés pour les langages de description systèmes indépendants (voir chapitre 2) ajoutent souvent inutilement des complexités rendant leur utilisation et leur personnalisation difficiles.

- les langages de description système orientés bibliothèque (voir chapitre 2) supportent difficilement la conception par blocs de propriété intellectuelle (IP) (voir chapitre 2) en raison d'un manque de séparation entre les aspects de modélisation et de simulation.

- les environnements de conception ne facilitent pas adéquatement la conception par IP; la consommation, le partage et l'analyse des informations décrivant les systèmes et les IP sont souvent difficiles.

Ce travail cible ces enjeux et propose des solutions utilisant les technologies modernes du logiciel. Plus précisément, ce travail s'attarde particulièrement à :

- la conception des langages de description orientés bibliothèque afin de faciliter leur utilisation, leur personnalisation et l'intégration d'outils tiercepartie

- la séparation des aspects de modélisation et simulation chez les langages de description orientés bibliothèque afin de faciliter la conception par IP et l'exploration de partitionnement.

- la gestion des informations décrivant les systèmes et les IP basée sur les technologies sémantiques afin de faciliter la consommation, le partage et l'analyse de celles-ci.

De plus, ce travail porte une attention particulière à l'implémentation du paradigme « Y-Chart » (voir chapitre 2) comme méthodologie pour la conception des systèmes puisque celui-ci propose un flux de conception complet qui ressemble beaucoup à la conception dirigée par les modèles utilisés par la communauté du logiciel.

## 1.4 Contribution et l'organisation

Les principales contributions de cette thèse sont les suivantes :

- la présentation du lien entre le développement orienté modèle et le paradigme du « Y-Chart ». Une discussion sur ce paradigme est faite, ainsi qu'une comparaison de plusieurs implémentations de celui-ci (chapitre 3).

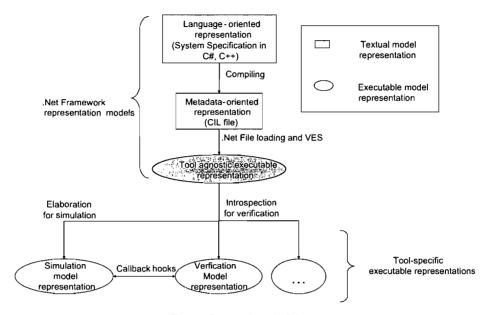

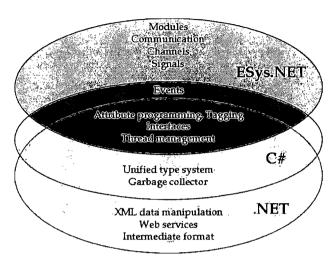

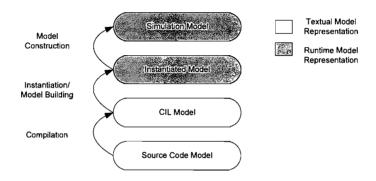

- la définition d'une nouvelle méthodologie pour la conception des outils CAO basée sur les technologies .Net et une vision orientée modèle (chapitre 4);

- l'élaboration d'une plateforme nommée Esys.Net pour la modélisation et la simulation de systèmes qui utilise cette nouvelle méthodologie (chapitre 4);

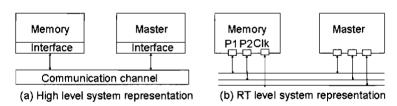

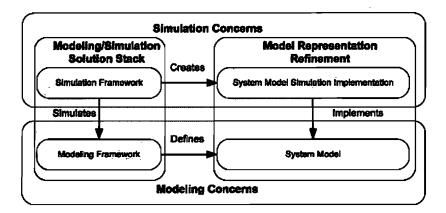

- la définition d'une nouvelle architecture cible pour les plateformes de type « Framework » pour la modélisation et la simulation de systèmes matériel/logiciel (chapitre 5);

- l'élaboration d'une plateforme nommée SoCML implémentant cette architecture cible (chapitre 5);

- la définition d'une approche innovatrice utilisant les technologies du « Semantic Web » pour palier au problème de l'utilisation des technologies XML dans le demain de la CAO (chapitre 6);

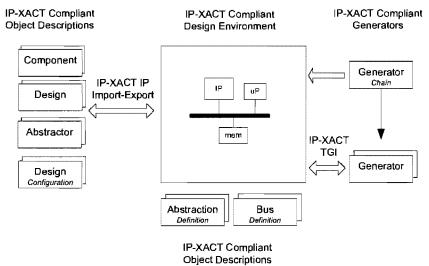

• la présentation d'une étude de cas basée sur le standard IP-XACT pour l'application des technologies sémantiques (chapitre 6);

Un ensemble précis de technologies logicielles a été crucial pour la réalisation de ces contributions. Ces technologies seront présentées, discutées et appliquées dans le contexte de la CAO et des systèmes embarqués, elles sont :

- le langage C# et la plateforme .Net;

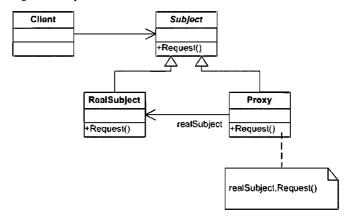

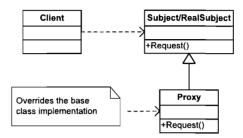

- les patrons de conception avancés tel que le « Proxy » et le « Dependency Injection »;

- le développement dirigé par les modèles;

- les technologies du Web sémantiques.

La forme de cette thèse est « par articles ». Le noyau de son contenu est constitué de quatre articles. Le chapitre 2 présente une revue de la littérature sur les outils de modélisation et de simulation des systèmes embarqués. Ce chapitre présente aussi trois méthodologies de conception de systèmes couramment utilisées. Le chapitre 2 résume aussi des revues déjà présentes dans les articles. Le contenu des chapitres 3 à 6 est essentiellement celui des articles. Le chapitre 7 est une conclusion plus globale que celles se trouvant dans chacun des articles.

## Revue de la littérature

L'synthèse. Pour faire face à cette insuffisance, nous utilisons les outils d'abstraction et de simplification pour créer des modèles de notre réalité qui sont compréhensibles et manipulables. Les systèmes embarqués sont très complexes. Ils comportent une énorme quantité de détails dont ceux-ci se manifestent sur plusieurs échelles de grandeurs – des effets de leurs fonctions perceptibles à notre niveau jusqu'aux phénomènes atomiques de leur implémentation. Donc, le domaine des systèmes embarqués ne peut être abordé sans faire des abstractions et des simplifications.

La modélisation de systèmes matériels complexes discrets ainsi que des langages pour exprimer ces modèles sont en utilisation depuis près de 40 ans [21][13]. Ces langages portent le nom de « hardware description language » (HDL). Avec la standardisation en 1987 par l'IEEE du langage VHDL, l'industrie a rapidement adopté les HDL comme des outils essentiels. Depuis l'apparition initiale des premiers HDL, les systèmes matériels ont évolué vers des formes plus complexes combinant le matériel et le logiciel : les systèmes embarqués. Afin de permettre aux concepteurs de modéliser ces nouveaux systèmes, les HDLs ont évolué aussi vers des langages appelés « system description languages » (SDL).

De concert avec le développement des HDL/SDL, des méthodologies de conception ont été élaborées. Ces méthodologies définissent des paradigmes de conception et/ou des cadres généraux d'activités pour guider le cycle de vie d'élaboration des systèmes complexes. Les trois méthodologies les plus utilisées aujourd'hui sont le raffinement successif, le paradigme « Y-Chart » et la conception à base de IP.

#### 1.5 Les SDL

Il existe deux grandes familles de HDL/SDL soit les indépendants et les orientées bibliothèque. Les HDL/SDL indépendants sont caractérisés par le fait qu'ils ont des syntaxes, des compilateurs et des analyseurs qui leur sont propres. Contrairement à ceux-ci, les HDL/SDL orientés bibliothèques sont définis au moyen de bibliothèques de code implémenté avec un langage de programmation général déjà existant tel que C++, C et Java. Chaque approche a ses avantages et ses inconvénients.

#### 1.5.1 Les HDL/SDL indépendants

Cette première famille de HDL/SDL est composée de langages conçus uniquement pour la description de systèmes matériels et/ou embarqués. La grande majorité de ces langages ont été conçus par l'industrie pour l'industrie. Certains de ceux-ci s'inspirent de proche ou de loin aux langages programmation déjà existants.

#### 1.5.1.1 VHDL [39]

Le développement de VHDL a été initié en 1981 par le « United States Department of Defence » afin d'adresser la crise du cycle de vie des systèmes matériels. VHDL est fortement inspiré du langage de programmation Ada. Les principaux objectifs de VHDL sont :

- définir une notation unifiée pour la description de systèmes électroniques modélisés à divers niveaux d'abstraction;

- être lisible par l'homme et les systèmes informatisés;

- supporter la communication de métadonnées reliées au processus de conception;

- faciliter la maintenance, la modification et l'acquisition de composantes matérielles;

- supporter le développement, la vérification, la synthèse et validation de description matérielle via un langage agnostique des outils.

VHDL est un langage dédié pour la description des systèmes matériels. Plusieurs des concepts nécessaires pour la description adéquate de composantes logiciels sont absentes. Malgré ce fait, VHDL est un langage très bien adapté pour la description de systèmes matériels aux niveaux d'abstraction des portes logiques et des transferts inter registres (RTL). Présentement, plus d'une quinzaine de standards IEEE sont

reliés au VHDL tel que VHDL-AMS [38] pour la description des systèmes analogiques.

#### 1.5.1.2 Verilog [37]

Verilog était le principal compétiteur à VHDL avant l'arrivée de SystemC en 1999. Malgré son apparition initiale en 1985, le langage est devenu un standard IEEE seulement en 1995. Verilog a l'avantage d'avoir une syntaxe beaucoup moins verbeuse que celle de VHDL au détriment d'une expressivité moindre. De plus, la simulation de modèle Verilog est généralement beaucoup plus rapide. Depuis quelques années, VHDL et Verilog convergent de plus en plus offrant ainsi des capacités similaires [5].

#### 1.5.1.3 SystemVerilog [65]

SystemVerilog est une extension de Verilog. Il a été proposé par le consortium Accellera en 2002 et standardisé par IEEE en 2005. SystemVerilog étend Verilog avec des éléments nécessaires pour la modélisation et la vérification de systèmes embarqués. SystemVerilog offre une expressivité très riche en matière de vérification et de validation. Cette expressivité est grandement due à l'intégration du langage OpenVera dans le standard. [6] fait la comparaison entre VHDL, Verilog et SystemVerilog. Par ce travail, on peut percevoir que SystemVerilog est un quasi surensemble de VHDL et Verilog.

#### 1.5.1.4 Handel-C et OCAPI [14]

Quelques articles discutent des avantages à utiliser des HDLs basés sur des langages de programmation existants [16]. OCAPI est un langage basé sur le C++. Il est très efficace pour effectuer de l'exploration à un niveau d'abstraction système. Handel-C est un langage basé sur le C. Il permet la traduction de ceux-ci vers EDIF et VHDL pour l'exécution sur FPGAs. Ces deux technologies ont la particularité qu'elles s'intègrent facilement ensemble pour offrir un environnent capable de supporter un processus de conception de systèmes ciblé pour les FPGA.

#### 1.5.1.5 SpecC [68]

SpecC a été développé en 1997 à l'University of California Irvine. Le langage SpecC est une extension du langage de programmation ANSI-C. SpecC augmente C avec des concepts essentiels pour la conception de systèmes. Il offre une notation formelle destinée aux spécifications et à la conception des systèmes embarqués. En 1999, le SpecC Technology Open Consortium (STOC) a été fondé pour guider l'évolution de SpecC. En décembre 2002, la deuxième génération du langage, SpecC 2.0, a été approuvé par le STOC. SpecC est l'un des rares langages à supporter la spécification explicite d'éléments comportementaux hiérarchiques. De plus, d'autres langages comme SystemC ont été fortement influencés par les concepts de canal de communication, ainsi que les divers niveaux d'abstraction de ceux-ci développés dans SpecC. SpecC a été conçu pour bien supporter par une méthodologie de conception de système basé sur l'assemblage d'IP.

#### 1.5.2 HDL/SDL orientés bibliothèques

La deuxième famille de HDLS/SDLs est celle dont les langages sont définis par l'entremise d'une bibliothèque de code développé avec un langage de programmation déjà existant tel que C++, C et Java. Via une bibliothèque de code, ces langages ajoutent les concepts nécessaires pour la conception de systèmes embarqués. Les concepts typiquement ajoutés sont :

- comportement concurrent;

- notion du temps;

- élément pour la modélisation d'élément de communication.

Pour l'élaboration de ce type de langage, ce sont souvent les langages orienté objet qui sont utilisés comme langage hôte pour les bibliothèques.

#### 1.5.2.1 JHDL [9]

JHDL est un environnement orienté objet qui exploite exclusivement les capacités du langage de programmation Java. JHDL permet la modélisation, la simulation et l'implémentation efficace sur FPGA de systèmes matériels définis au niveau RTL. Le principal objectif de JHDL est de développer un environnement pour la CAO

exploratoire pour l'identification des dispositifs principaux et les fonctionnalités clés que celui-ci doit offrir pour le développement de systèmes ciblé pour les FPGA.

#### 1.5.2.2 SystemC [64]

SystemC, annoncé en 1999 par The Open SystemC Initiative (OSCI), a été reçu avec beaucoup d'enthousiasme de la part de l'industrie et de la communauté académique. SystemC a été le premier SDL orienté bibliothèque basé sur le langage C++. En 2003, l'OSCI a annoncé le SystemC Verification Library (SCV) [27], une bibliothèque ajoutant des fonctionnalités de vérification et d'introspection. En 2005, SystemC a été standardisé par l'IEEE. À l'heure actuelle, c'est un langage très populaire pour la conception des systèmes embarqués. SystemC offre tous les concepts qu'on retrouve typiquement dans les HDLs traditionnels tel que VHDL et Verilog. Il offre aussi un ensemble de concepts supplémentaires permettant la spécification de systèmes à divers niveau d'abstraction. Toutefois, la version courante de SystemC n'offre pas tous les concepts nécessaires pour la modélisation de composantes logicielles. Il est possible d'utiliser les capacités intrinsèques du langage C++, mais le standard ne définit pas formellement comment ses éléments devraient être pris en considération par la bibliothèque. Une étude fait par Doulos [26] illustre que la majorité des compagnies utilisant SystemC font des études de performance, de l'exploration d'architecture, de la modélisation au niveau transactionnel et de la conception logiciel-matériel. L'étude illustre aussi que ces compagnies utilisent généralement des HDL standards comme VHDL pour la modélisation de systèmes matériels et pour la synthèse.

#### 1.6 Les méthodologies

Les méthodologies de conception sont un élément essentiel pour la réalisation de systèmes. Elles définissent un cadre de travail permettant de guider de manière répétitive et prévisible le processus d'élaboration d'un système. Généralement, ces cadres de travail comportent deux composantes : une liste d'artéfacts de travail et un ensemble de flux d'activités. Les artéfacts sont des intrants ou des extrants aux activités du cadre de travail. Le type d'artéfacts utilisés, le processus de réalisation de ceux-ci, ainsi que leur importance dans le processus global d'élaboration sont des éléments différenciant les diverses méthodologies sur le marché. Les trois méthodologies les plus présentes sont :

- l'élaboration par raffinements successifs;

- le paradigm « Y-Chart »;

- la conception à base d'IP.

La plus ancienne mais encore la plus répandue est l'élaboration par raffinements successifs. Le rôle des flux d'activités est d'organiser les différentes catégories d'activités nécessaires pour la conception d'un système afin d'avoir une recette répétable. Les catégories d'activités les plus typiques sont la modélisation, la vérification, la validation, l'analyse de performance et la synthèse. Chaque méthodologie organise différemment les activités.

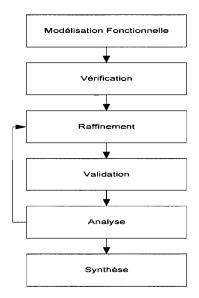

#### 1.6.1 L'élaboration par raffinements successifs

Au plus simple, l'élaboration par raffinements successifs consiste à créer le modèle d'un système à un haut niveau de détails qui est par la suite détaillé par raffinements successifs afin de produire une description du système pouvant être implantée [71]. Cette approche est orientée « top-down » ou de « haut vers le bas ». Typiquement, le premier modèle du système est très orienté fonctionnel. Celui-ci abstrait tous les aspects d'implémentation afin de cibler uniquement les exigences, les fonctions et l'interaction entre celles-ci. Ce modèle est ensuite vérifié pour valider sa complétude et sa cohérence. Il est finalement raffiné pour obtenir de nouveaux modèles comportant des détails d'implémentation de plus en plus précis. L'objectif de chaque raffinement est d'explorer divers choix de conceptions pour évaluer leurs impacts

(performance, puissance, etc.). Généralement, chaque itération de raffinement comporte un ensemble de tâches réalisées plus ou moins en série :

- raffinement du modèle afin de créer un modèle plus détaillé;

- validation de l'alignement entre le nouveau modèle et les exigences afin de ne pas introduire d'erreur;

- analyse des performances (temps d'exécution, puissant, etc.) du système défini. Cette analyse est soit faite avec des méthodes d'analyse statiques (model checking) ou dynamiques (simulation);

- analyse des résultats;

- définition de la stratégie pour la prochaine itération de raffinement.

Figure 4 Raffinements Successifs

La figure 4 illustre le flux d'activités de la méthodologie. Les diverses implémentations de cette méthodologie identifient deux axes de raffinement :

- calcul;

- communication.

Les raffinements sur l'axe du calcul consistent à ajouter des détails tels que le temps nécessaire pour faire les calculs, la répartition des fonctions en logiciel ou matériel, la gestion du partage de ressources de calcul, etc. Les raffinements sur l'axe de la communication consistent à ajouter des détails tels que le temps nécessaire pour faire les communications, la gestion du partage des ressources de communication, les protocoles de communication, la médiation entre les divers protocoles de

communication, etc. Dans [24] un raffinement selon des axes est présenté ainsi qu'une taxonomie de modèles ciblant des niveaux de détails précis sur ces axes. [30] présente une autre taxonomie de modèles ainsi que leur position dans un flux de travail.

Les grandes difficultés de cette approche sont d'explorer rapidement des solutions alternatives de raffinement et de garantir que ces raffinements n'introduisent pas d'erreurs. La première problématique est due au fait que généralement les modèles sont biaisés par une certaine conception générale du système. Ce biais est souvent introduit aussitôt que la modélisation initiale. Chaque raffinement introduit de nouveaux biais. Ces biais sont quasiment inévitables, en raison du caractère « top-down » de la méthodologie. Puisque le dernier raffinement fait doit aboutir une spécification d'implémentation avec une architecture bien définie, il est sans contre dit que chaque raffinement amènera le modèle à posséder des caractéristiques de cette architecture finale. Ce biais rend difficile l'exploration de raffinement pouvant aboutir à des architectures très différentes. Chaque raffinement contraint donc les possibles explorations.

La deuxième problématique est due au fait que chaque raffinement nécessite de retoucher au modèle afin d'introduire des nouveaux détails. Les raffinements peuvent consister à ajouter que de simples annotations liées au temps ou la consommation énergétique jusqu'à des modifications majeures nécessitant la réécriture/substitution de certaines portions du modèle. Ce dernier cas est typique lors du passage d'un niveau d'abstraction à un autre tel que le passage d'une modélisation au niveau d'un protocole de communication à un niveau de détails RTL. Donc, chaque raffinement fait que le modèle peut introduire des erreurs qui sont parfois difficiles à détecter tôt. SystemC et SpeC sont des environnements bien adaptés à cette méthodologie.

#### 1.6.2 La conception à base d'IP

À l'opposée de la méthodologie par raffinements successifs, la conception à base d'IP utilise une approche « bottom-up » [55]. L'idée générale est de concevoir un système par l'assemblage d'un ensemble de composantes existantes offrant des fonctionnalités et des interfaces d'intégration standardisées. On peut facilement faire le parallèle avec le jeu de bloc ©Lego. Chaque bloc ©Lego à une forme précise et une interface standardisée qui permettent de le connecter à d'autres blocs ©Lego. Donc, je peux facilement construire une entité aussi complexe fonctionnellement qu'un château avec un ensemble de composantes très simples. Le développement de cette méthodologie a grandement été poussé par le besoin de concevoir rapidement des systèmes complexes pour répondre à des besoins du marché. Puisque typiquement, chaque bloc a été préalablement testé, analysé et synthétisé, il est généralement facile de concevoir un système valide et synthétisable avec les caractéristiques de performance désirées.

Malgré la simplicité théorique de cette méthodologie, l'implémentation de celle-ci n'est pas triviale en raison de plusieurs difficultés pragmatiques. Le support informatisé d'une méthodologie par des outils pour la CAO est important. Il y a plusieurs outils commerciaux sur le marché supportant l'approche, mais il n'y a pas de standard non-propriétaire très répandu pour la description d'IP afin que ceux-ci soit supportés par les outils. Chaque fabriquant doit en pratique prendre la décision de rendre son IP disponible à un sous-ensemble d'outils sur le marché. De plus, il est souvent difficile d'offrir une représentation suffisante d'un IP pour supporter le processus de conception (simulation, test, synthèse), mais dont le détail de la représentation ne dévoile pas les secrets de conception propriétaire du IP. Une autre grande difficulté est qu'il n'existe pas de standard unique d'interface pour les composantes, donc pour des raisons purement pratiques, les fabricants doivent se limiter à supporter un nombre limité d'interface. Donc l'ensemble de ces difficultés fait en sorte qu'il est difficile d'avoir un ensemble de composantes couvrant l'ensemble de nos besoins pouvant être facilement interconnectés et dont le système total peut être facilement testé et synthétisé.

#### 1.6.3 Le paradigme « Y-Chart »

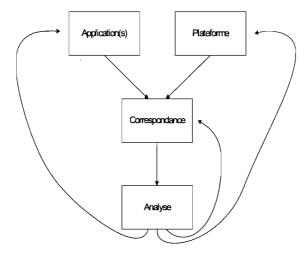

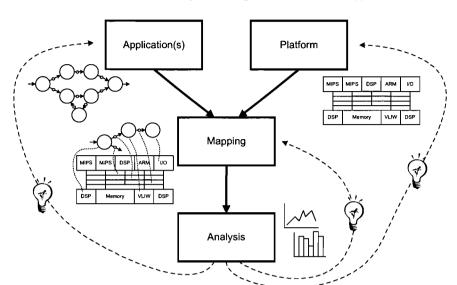

Figure 5 Y-Chart

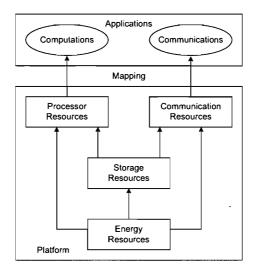

Le paradigme « Y-Chart » est caractérisé par un flux d'activité débutant avec deux branches indépendantes qui se rejoignent pour se terminer avec une série d'activités [43]. Le tout forme un Y comme illustre la figure 5 d'où le nom « Y-Chart ». Cette méthodologie est basée sur l'idée qu'il est important de séparer le problème de conception de systèmes en deux sous problèmes : (i) définir les fonctions d'un système de matière agnostique d'une implémentation (l'application) et (ii) définir une plateforme (matériel et logiciel) offrant un ensemble de ressources de calcul, de communication et de stockage pouvant supporter les besoins fonctionnels. Les exigences de l'application sont typiquement définies au moyen d'éléments de calcul communiquant ensemble via des éléments de communication. Généralement, ce type de définition permet d'expliciter le parallélisme pouvant être exploité dans l'application. Il est difficile d'être plus précis, car chaque implémentation du paradigme utilise son propre formalisme pour la portion application et plateforme, donc nous essayons juste de peindre un portrait général de l'approche.

Une fois ces deux sous problèmes résolus, une correspondance est définie entre les éléments de l'application et les ressources de la plateforme. Cette correspondance établie une configuration entre la ressource de la plateforme utilisée pour implémenter un certain élément applicatif. Une fois la correspondance faite, il est possible d'évaluer les performances (temps d'exécution, puissance, etc.) de

l'implémentation des besoins sur la plateforme selon la configuration établie. Selon les résultats obtenus, le concepteur peut revoir sa correspondance, la conception de la plateforme et la définition des besoins. Il peut boucler dans ce flux aussi longtemps qu'il n'a pas obtenu les résultats voulus.

Les grandes difficultés de cette méthodologie sont la séparation d'un problème en deux modèles agnostiques l'un de l'autre et la mise en correspondance des deux modèles. Ces deux problèmes sont intrinsèquement reliés, car généralement plus l'éloignement des deux modèles est grand plus la mise en correspondance est difficile.

Il n'est pas rare de voir cette méthodologie utilisée avec les deux autres et cela surtout pour la portion plateforme. Originalement, le paradigme « Y-Chart » a été conçu pour adresser la problématique de l'implémentation d'un besoin fonctionnel sur une plateforme existante dont celle-ci pouvait accommoder les besoins de diverses manières. Cette méthodologie permettait donc de faciliter l'exploration de ces diverses implémentations afin de trouver la meilleure. Pour cette raison, les compagnies ciblant une stratégie de réutilisation de plateformes flexibles et puissantes pour implémenter plusieurs produits utilisent souvent cette approche. On appelle cette approche de la conception orienté plateforme ou « plateform-based design» [18]. La définition de cette plateforme peut être le produit d'une conception à base d'IP ou par raffinements successifs. Métropolis [8] est un exemple d'environnement utilisant cette méthodologie.

#### 1.7 Les nouveaux défis

Une autre révolution importante dans le domaine des circuits intégrés est l'intégration d'éléments non-microélectroniques sur silicium tel que les composants micro-optiques et micromécaniques. La conception de systèmes complexes et hétérogènes incluant ces composantes est caractérisée par un ensemble de nouveaux problèmes devant être résolus au niveau de la modélisation et de la vérification.

# Le paradigme « Y-Chart » : une discussion sur le développement dirigé par les modèles

algré sa grande complexité si on s'attarde aux détails, le processus de développement d'un logiciel ou d'un système embarqué peut être résumé par deux grandes étapes :

- comprendre et décrire le besoin (le quoi);

- implanter la solution (le comment).

La communauté du logiciel s'intéresse à ces deux étapes ainsi que le passage de l'un à l'autre depuis plusieurs années. Dans les années 70, des techniques structurées pour aborder ces sujets ont vu le jour afin de pallier aux nombreux problèmes reliés aux approches précédentes généralement très ad hoc [23]. Au fil des années, influencées par l'émergence de nouveaux paradigmes tel que l'orienté objet, les techniques structurées ont donné place aux techniques d'analyse et de conception orienté objet [12]. Malgré les énormes efforts investis pour avancer la science de l'élaboration des logiciels, le passage du « quoi » au « comment » reste toujours très difficile. Une cause principale de cette difficulté est que le passage du « quoi » au « comment » se traduit souvent par une intervention humaine qui fait l'élaboration d'artéfacts pour implémenter le « comment » basé sur sa compréhension du « quoi ». Ce type d'intervention est souvent long et sujet à l'erreur.

Au début des années 80, une nouvelle approche a été proposée pour rapprocher le « quoi » du « comment », la méthode d'analyse orienté objet et de conception récursive Shaler-Mellor [66]. Cette approche consiste à modéliser le « quoi » de manière assez précise qu'il soit possible d'utiliser une approche par traduction automatisée pour générer le « comment » final. Cette approche préconise aussi, basée sur le principal de l'orthogonalité des aspects, une modélisation séparée des aspects

purement logiciel des aspects de contraintes architecturales, ainsi que la spécification des « ponts » afin de faire le lien entre les deux aspects. Cette approche a été raffinée dans les années 90 et 2000 afin de donner lieux à la conception dirigée par les modèles [11] et l'architecture dirigée par les modèles [45]

Le paradigme « Y-Chart » développé en 1997 peut être clairement classifié comme une approche dirigée par les modèles au même titre que la méthode Shaler-Mellor Quoi que le travail original de [43] ne fait mention que de l'approche orienté objet et non le travail de [66], il est difficile de croire que l'approche n'a pas été influencée par ce dernier ou du moins par les principes véhiculés dans le milieu du logiciel grâce à celui-ci au début de années 90.

L'article qui suit présente le paradigme « Y-Chart », un exemple d'une méthodologie pour la conception de systèmes embarqués dirigé par les modèles. Une grande portion de l'article est consacrée à la présentation/discussion de diverses approches pour l'implémentation de cette méthodologie, un sujets qui n'ont pas beaucoup été traités dans la littérature. Cet article peut-être perçu comme une extension de l'état de l'art de cette thèse.

Les contributions principales de cet article sont:

- une présentation à caractère pédagogique de la méthodologie « Y-Chart », des modèles de calcul et des modèles d'architecture;

- une présentation de trois implémentations de la méthodologie « Y-Chart » afin de faire la comparaison de leurs choix de conceptions.

Les pages suivantes contiennent une copie de l'article [50], dans son format original (sauf la numérotation des pages), soumis à ACM Transactions on Embedded Computing Systems.

# Y-Chart Based System Design: A Discussion on Approaches

#### JAMES LAPALME

University of Montréal, Department of Computer Science and Operations Research, Canada

and

#### **BART THEELEN**

Eindhoven University of Technology, Department of Electrical Engineering, Netherlands and

#### NIKOLAY STOIMENOV

ETH Zürich, Computer Engineering and Networks Laboratory, Switzerland and

#### JEROEN VOETEN

Eindhoven University of Technology, Department of Electrical Engineering; Embedded Systems Institute; Netherlands

and

#### LOTHAR THIELE

ETH Zürich, Computer Engineering and Networks Laboratory, Switzerland and

#### EL MOSTAPHA ABOULHAMID

University of Montréal, Department of Computer Science and Operations Research; Canada

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

© 2009 ACM 0000-0000/2009/0000-0001 \$5.00

#### 2 · James Lapalme et al.

Embedded systems are a source of technology that facilitates our modern lifestyle. In order to do so, they tend to increase in complexity as well as integrate in are day-to-day activities. To meet the market's expectations on technological improvement, time-to-market objectives for introducing innovative embedded systems are shorter than ever. Over the last decade, model-based design has been a subject of great interest as a means to accelerate the design of embedded systems. The Y-chart paradigm is a principal approach to model-based embedded system design. Despite the simplicity and conciseness of this paradigm, it has been implemented in several different ways by various methodologies. This variety in implementation designs is due to the particular emphasis a methodology puts on the different steps of the paradigm (application modeling, platform modeling, mapping, analysis and synthesis). This article explores this variety by examining and comparing three Y-chart based design methodologies: Metropolis, the Distributed Operation Layer incorporating Modular Performance Analysis and the Y-chart variant of the Software/Hardware Engineering methodology. These methodologies have been chosen because they: cover a broad domain of applications, have been developed on a relatively long period of time and are representative of typical Y chart approaches. Moreover, these implementations of the paradigm present interesting design approaches which are worth comparing.

This article (i) presents the concepts underlying the Y-chart paradigm as well as models of computation and models of architecture, (ii) discusses the three mentioned implementations, and (iii) compares these implementations to highlight important design differences. The examination and comparison show that the Y-chart paradigm is a very flexible framework that can be implemented in many ways.

Categories and Subject Descriptors: C.0 [Computer Systems Organization]: Modeling of Computer Architecture, System Architectures, Systems Specification Methodology; F.1.1 [Computation by Abstract Devices]: Models of Computation; B.1.2 [Performance and Reliability]: Performance Analysis and Design Aids; I.6.4 [Simulation and Modeling]: Model Validation and Analysis; I.6.5 [Simulation and Modeling]: Model Development—Modeling Methodologies

General Terms: Design, Languages, Measurement, Performance, Verification Additional Key Words and Phrases: Design-Space Exploration, Embedded Systems, Model of Architecture, Model of Computation, Y-Chart

#### 1. INTRODUCTION

The decreasing time-to-market for modern embedded systems encourages the industry to strive for design reuse between multiple products. Moreover, the constantly increasing consumer demands for full featured systems requires the use of high-performance platforms. In order to cope, systems designers often consider platforms such as Multi-Processor Systems-on-Chip (MPSoC) because they allow reuse and offer high-performance. MPSoC include a combination of multiple processors and specialized processing elements to allow the execution of multiple applications in parallel. They also offer the flexibility to optimise aspects such as performance and energy consumption. When elaborating a system, designers face some crucial questions:

- —Which platform is most suitable for realizing the requested functionality?

- —How to exploit the parallelism provided by the chosen platform efficiently?

- —Is the application software parallelized in a suitable way?

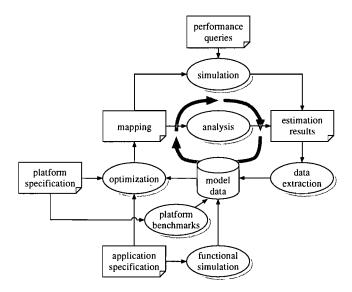

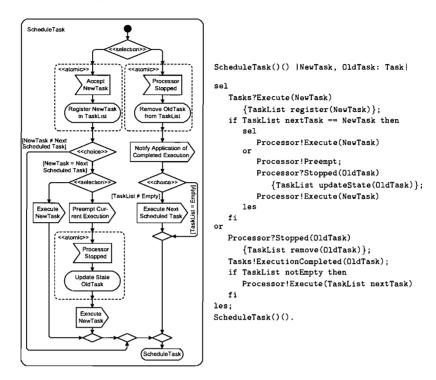

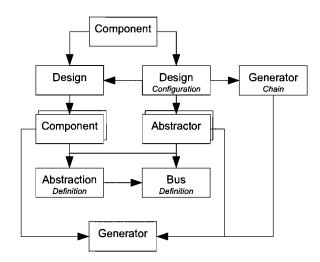

Figure 1 illustrates how the Y-chart paradigm introduced in [Kienhuis et al. 1997] provides a framework for answering these questions. This work should must not ACM Journal Name, Vol. V, No. N, M 2009.

3

Fig. 1. Design-space exploration with the Y-chart paradigm

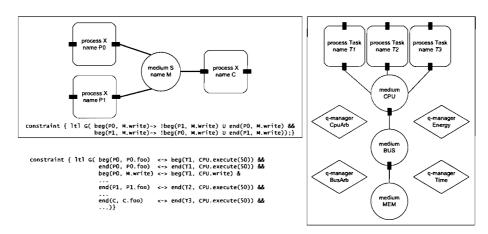

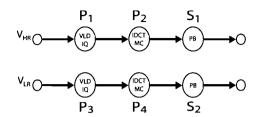

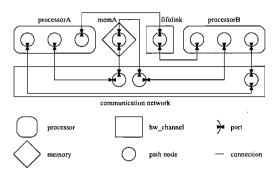

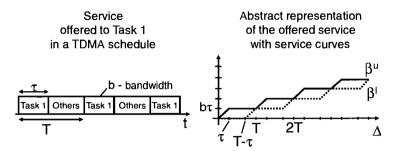

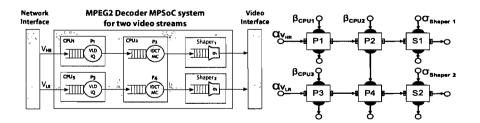

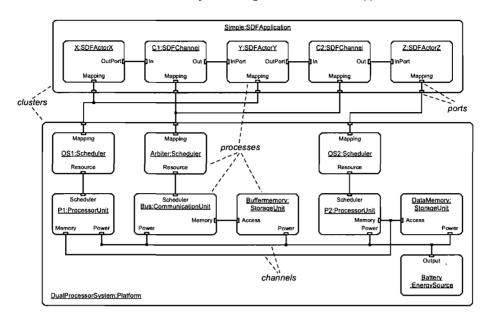

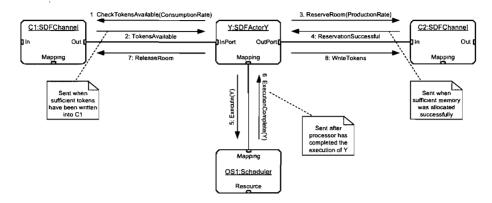

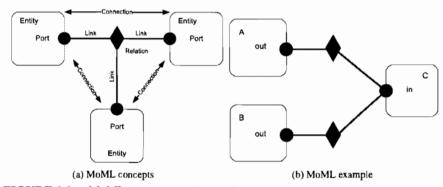

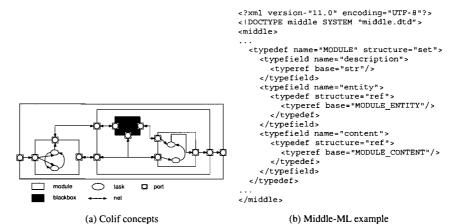

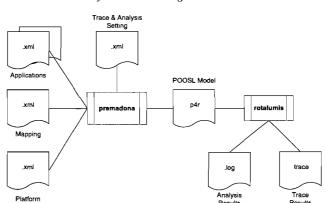

be confused with the Gajski and Kuhn Y-chart [Gajski and Kuhn 1983] which is a taxonomy for visualizing design views as well as design hierarchies. Modern embedded systems such as mobile phones support multiple applications such as MP3 players and Internet browsers. These applications are targeted to execute on a collection of processors (and specialized processing elements) that make up a platform [Martin 1998; H. Chang and Todd 1999; Sangiovanni-Vincentelli and Martin 2001]. By defining a mapping to specify which processor (or specialized processing elements) executes what functions of each application (allocation and binding) and at which moments in time (scheduling), one can predict the resulting performance of the overall solution design. The analysis of these results may give hints for improving the application software, the platform design and/or the mapping. The Y-chart paradigm envisions to iteratively apply such improvements until finding a solution that satisfies the end requirements. The final solution is then implemented to produce the desired product. The Y-chart paradigm was initially introduced by Kienhuis et al. [Kienhuis et al. 1997] in the context of dataflow-oriented systems. It was also independently applied in the POLIS project [Balarin 1997] for control dominated systems (e.g. automotive). Recently, it has also been used in others control-oriented domains [Baleani et al. 2000; Sgroi et al. 2001; Zeng et al. 2006]. The work introduced by Kienhuis consisted of Stream-Based Functions for describing applications, a C++ inspired Pamela library for specifying platforms, and a simulator called ORAS to perform the analysis part [Kienhuis 1999].

Although the key concept underlying the Y-chart paradigm of explicitly separating application descriptions from a platform specification is relatively simple, methodologies like POLIS, Metropolis [Balarin et al. 2003], SPADE [Lieverse et al. 2001], and Cadence's Virtual Component Co-Design Environment [Krolikoski et al. 1999] use very different implementations of the paradigm. This article discusses the

#### 4 · James Lapalme et al.

Y-chart paradigm for design-space exploration of distributed embedded systems by investigating alternative approaches to implement it. To this end, we focus on alternative formalisms for specifying applications and platforms as well as different views on how a mapping can be described. In addition, we elaborate on the possible analysis and design-space exploration capabilities that various Y-chart based design methodologies support and how they assist a designer in finding a suitable solution for a design problem. We have chosen to write this paper because there are few papers which compare various design approaches for the implementation of the Y-Chart paradigm.

The objective of this paper is not to offer the reader an in-deep comparison of various implementations in order to determine ranking. The objective is rather to present and discuss some interesting design approaches the authors have observed for implementing the different steps of the Y-Chart paradigm. These approaches will be compared in order to highlight capabilities, limitations and trade-offs. The authors would also like to stress that great emphasis will be put on design and not implementation of these approaches, hence issues such as performance and scalability will not be greatly discussed. The three specific implementations of the Y-Chart paradigm used in this paper are Metropolis, the Distributed Operation Layer incorporating Modular Performance Analysis and the Y-chart variant of the Software/Hardware Engineering methodology. The paper also presents the history and key underpinning concepts of the Y-Chart paradigm in order to offer an in-deep presentation of the paradigm. The secondary objectives of this paper are to offer a good introduction to the Y-Chart paradigm as well as contribute to the design debates surrounding its implementation.

This article is organized as follows. After presenting the background of the Y-chart paradigm in more detail, we summarize related work on various design methodologies that implement it. Subsequently, we elaborate on formalisms for describing applications and for specifying hardware platforms. After a detailed overview of three particular methodologies, we give a concise comparison that highlights alternative approaches for implementing the Y-chart paradigm. The examination and comparison of the methodologies show that the implementation of the Y-chart paradigm maybe done in various ways.

#### 2. BACKGROUND

# 2.1 Y-Chart Based Design-Space Exploration

The Y-chart paradigm is an example of a model-driven engineering framework [Bezivin 2005]. The crux of explicitly separating applications (functionality) from the platform (architecture) as shown in Figure 1 leads to the following five-step approach to minimize overall design time:

- (1) Create a model of the functionality performed by each application in a fashion that is independent of any specific platform and which expresses opportunities for parallel execution;

- (2) Create a model of the platform that captures key characteristics of the services it can provide to applications using resources like processors, busses, memories and power; as well as the cost of these services in terms of area, performance, energy, etc;

- (3) Define a mapping of how the platform is deployed to execute the applications;

- (4) Evaluate the quality of the parallelized applications mapped onto the platform in terms of area, performance, energy, etc and decide on improvements for the application software, platform design or mapping in case the results are unsatisfactory. If so, repeat step 1, 2 or 3 respectively according to the new insights until a solution is found that satisfies all design requirements;

- (5) Realize the solution in terms of synthesising hardware and compiling software.

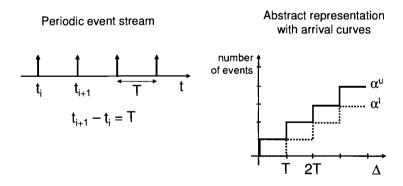

Y-chart based design methodologies assist designers by providing: (i) a coherent set of formalisms, (ii) techniques for analyzing design solutions and (iii) techniques for searching the design space. They often offer computer aided design tools. Formalisms refer to languages for writing down models. To efficiently exploit platforms with multiple processing elements, it is necessary to make potential parallelism in applications explicit. Models of Computation (MoC) are formalisms that describe systems in terms of computation and communication entities. Computation entities (or tasks) capture functional behaviour, whereas communication entities represent data and control dependencies between concurrently executed tasks. Most MoCs will help designers to make explicit potential parallelism. An application model created in step 1 expresses the services required for executing functional behaviour. These service requests are often characterized by the number of instructions to execute or the amount and size of data to be communicated. The term Model of Architecture (MoA) is sometimes used to denote a MoC that is specifically intended for describing platforms. A platform model for step 2 specifies the services that the resources of a platform can provide as well as the cost of using them (cycles, energie, etc.). Notice that although we use MoC and MoA to emphasize the purpose of formalisms, Y-chart based design methodologies may actually use the same formalism for describing both applications and platforms. A mapping in step 3 basically represents a possibly interesting match between the service requesting computation and communication entities in applications and the service providing resources in a platform. When a specific combination of application models, a platform model and a mapping yields satisfactory results with respect to the design requirements, then step 5 realises this particular design solution using appropriate software and hardware synthesis tools.

The Y-chart paradigm is very suitable for design problems where platforms offer multiple resources in order to execute a particular computation. The suitability is a consequence of the ease of defining various mappings between an application and a platform which are defined separately. For design problems where mapping alternatives are fairly absent, such as in telecommunication networks or traditional control systems, applying the Y-chart paradigm can be counterproductive. The reason for this is that such systems actually benefit from a higher degree of coupling between the functionalities they offer and implementation of latter. Methodologies supporting the development of such integrated models include SystemC based approaches [Grotker et al. 2002], System-on-Chip Environment [Gajski et al. 2000] and Software/Hardware Engineering [Theelen et al. 2007]. These methodologies often rely on successive refinement of the integrated model towards a synthesisable design where a distinction between applications and the platform on which they run is less prominent than in the Y-chart paradigm.

# 2.2 Models of Computation

An interesting view on MoCs is given in [Burch et al. 2001]:

"A model of computation is a distinctive paradigm for computation, communication, etc. For example, the Mealy machine model of computation is a paradigm where data is communicated via signals and all agents operate in lockstep (we use "agent" as a generic term that includes both hardware circuits and software processes). The Kahn Process Network model is a paradigm where data carrying tokens provide communication and agents operate asynchronously with each other (but coordinate their computation by passing and receiving tokens). Different paradigms can give quite different views on the nature of computation and communication. In a large system, different subsystems can often be more naturally designed and understood using different models of computation."

Having different views on the nature of computation and communication implies that modeling an application with various MoCs may result in models that differ significantly in the amount of details that is expressed about computation and computation. In the context of the Y-chart paradigm, MoCs that explicitly express (potential) concurrency between computations are of special interest. We categorize MoCs as control-oriented, dataflow-oriented and process-oriented:

- —Control-oriented MoCs consider systems as automata, which consist of states and transitions between these states. A state captures a certain status reachable by executing a (collection of) computation(s), while transitions describe possible changes in this status (i.e., the execution steps). Although automata are mostly suited for describing pure sequential systems, some control-oriented MoCs such as Communicating Finite State Machines (CFSM) [Brand and Zafiropulo 1983] and Co-design Finite State Machine (CDFSM) [Balarin 1997] allow describing a system as a collection of concurrent state machines that can communicate with each other.

- —Dataflow-oriented MoCs describe systems in terms of tasks (actors or processes), channels and tokens. A task is a computation entity that can potentially be executed in parallel with other tasks. Tasks communicate with each other by exchanging tokens through channels. Such a token denotes an indivisible unit of information. The channels often include FIFO buffers to enable the sending and receiving tasks to run at a different rate, while successively communicated tokens are processed in-order.

- —Process-oriented MoCs use processes and events as major modeling entities. A process represents a computation entity that may be executed in parallel with other processes. Processes can synchronise based on communication events, which can for example be in terms of signals or passing messages.

It is sometimes possible to express a MoC of one type by using a MoC of another, however such alternative representations are not always very intuitive. Such an example is the process-oriented MoC of SystemC [Grotker et al. 2002] that can express various control-oriented, dataflow-oriented and other process-oriented MoCs. Another such example is use of certain types of automata (i.e., control-oriented MoCs) to formally express the semantics of dataflow- and process-oriented MoCs such as Synchronous Dataflow [Lee and Messerschmitt 1987; Ghamarian 2008] and the Par-

|                   | MoC'                                                     | Reference                         | Concurrency                  | Communication                                                                    | Time                                                                | Explicit Non-<br>Determinism | Stochasticity                                                                                | Analytic<br>Tractability |

|-------------------|----------------------------------------------------------|-----------------------------------|------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------|--------------------------|

| Control-Oriented  | Finite State Ma-<br>chines                               | [Hoperoft and<br>Ullman 1979]     | -                            | ÷                                                                                | Integer-valued*                                                     |                              | -                                                                                            | ++                       |

|                   | Discrete-Time<br>Markov Chains                           | [Chung 1967]                      | -                            | -                                                                                | Discrete real-<br>valued distribu-<br>tions                         | -                            | Discrete distributions on time                                                               | ++                       |

|                   | Timed Probabilistic<br>Systems                           | [Alur 1991]                       | -                            | -                                                                                | Discrete real-<br>valued distribu-<br>tions                         | +                            | Discrete distributions on behavior and time                                                  | +                        |

|                   | Synchronous<br>Dataflow                                  | [Lee and Messer-<br>schmitt 1987] | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven                                      | Integer-valued*,<br>discrete integer-<br>valued distribu-<br>tions* | -                            | Discrete distributions<br>on time*                                                           | ++                       |

|                   | Cyclo-Static<br>Dataflow                                 | [Bilsen et al<br>1995]            | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven                                      | Integer-valued*                                                     | -                            | -                                                                                            | ++                       |

| Dataflow-Oriented | Scenario-Aware<br>Dataflow                               | [Theelen et al<br>2006]           | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven                                      | Discrete real-<br>valued distribu-<br>tions                         | +*                           | Discrete distributions<br>on behavior and time                                               | ++                       |

| Ģ                 | Boolean Dataflow                                         | [Buck 1993]                       | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven                                      | -                                                                   | -                            | -                                                                                            | o                        |

| aflow             | Kahn Process<br>Networks                                 | [Kahn 1974]                       | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven                                      | -                                                                   |                              | -                                                                                            |                          |

| Dat               | Dynamic Dataflow                                         | [Buck 1993]                       | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven                                      | -                                                                   | +                            | -                                                                                            | -                        |

|                   | Reactive Process<br>Networks                             | [Gerlen and<br>Basten 2004]       | Asynchronous                 | Asynchronous FIFO<br>buffered, token-driven<br>and synchronous control<br>events |                                                                     | +                            | -                                                                                            |                          |

| 1                 | Real-Time Calculus                                       | [Thiele et al<br>2000]            | Asynchronous                 | Asynchronous (FIFO)<br>huffered, data-driven                                     | Continuous                                                          | +                            | +*                                                                                           | ++                       |

| 2                 | Esterel                                                  | [Boussinot and<br>Simone 1991]    | Synchronous                  | Unhuffered asynchronous<br>signals                                               | Discrete integer<br>valued                                          | -                            | •                                                                                            | +                        |

| -                 | Communicating<br>Sequential Proc-<br>csses               | [Hoare 1978]                      | Asynchronous                 | Synchronous message passing                                                      | -                                                                   | -                            | -                                                                                            | ++                       |

| iente             | Communicating<br>Concurrent Systems                      | [Milner 1989]                     | Asynchronous                 | Synchronous message<br>passing                                                   | -                                                                   |                              | -                                                                                            | ++                       |

| s-Or              | Metropolis Meta<br>Model                                 | Baların et al<br>2003]            | Asynchronous                 | Unbutfered asynchronous events                                                   | Discrete real-<br>valued                                            | +                            | •                                                                                            | o                        |

| Process-Oriented  | Timed Automata                                           | [Alur and Dill<br>1994]           | Asynchronous                 | Synchronous message passing                                                      | Discrete real-<br>valued or<br>continuous                           | +                            | Discrete distributions<br>on behavior and dis-<br>crete or continuous<br>distributions time* | +                        |

|                   | Parallel Object-<br>Oriented Specifica-<br>tion Language | [Bokhoven 2002]                   | Asynchronous<br>(two levels) | Synchronous message passing                                                      | Discrete real-<br>valued                                            | +                            | Discrete distributions on behavior and time                                                  | +                        |

Table I. Comparing some example models of computation

allel Object-Oriented Specification Language [Bokhoven 2002]. Some research has been done on unifying various MoCs. Such unification is important when defining subsystems with different MoCs. Examples of unifying MoCs are the Tagged Signal Model Framework (TSM) [Lee and Sangiovanni-Vincentelli 1998] and the Ptolemy Project [Brooks et al. 2005].

Table I gives an overview of a number of widely used MoCs. It summarize their approach to concurrency, communication and time. These aspects are essential for modeling distributed embedded system. A \* indicates that the aspect is supported by some variant of the MoC. The table also indicates whether the abstraction mechanisms of explicit non-determinism (i.e., not implied by concurrency but by some other language construct) and stochasticity are supported. The last column gives some impression to what extend the basic form of a MoC is analytically tractable. Comparing MoCs on this last aspect is very difficult and the results in Table I should therefore be taken with precaution. A -- indicates that (nearly) all properties are undecidable at design time. In case some design-time analysis is possible, such as structural consistency checks, a - is used. Conversely, ++

#### 8 • James Lapalme et al.

indicates that (nearly) all models expressed in the considered MoC are fully design-time analyzable, both for correctness and performance. A + expresses that not all but many models are fully analyzable. A problem could for example be the implication of an infinite state space by certain models. A o denotes analytical tractability between - and +.

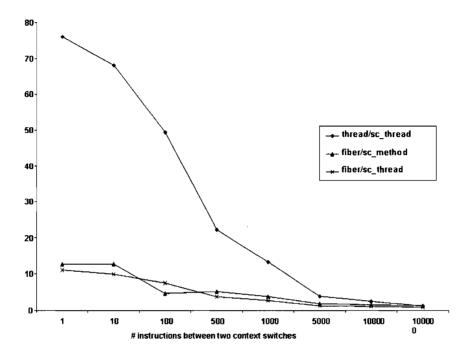

#### 2.3 Models of Architecture