#### Université de Montréal

# Synthèse de EFSM observatrices à partir de spécifications HAAD

par

Etienne Ogoubi

Département d'informatique et de recherche opérationnelle

Faculté des arts et des sciences

Mémoire présenté à la Faculté des Études Supérieures en vue de l'obtention du grade de maîtrise (M.Sc) en informatique

Avril, 2002

© Etienne Ogoubi, 2002

QA 176 U34 2007 V.038

J

#### Université de Montréal Faculté des Études Supérieures

#### Ce mémoire intitulé

Synthèse de EFSM observatrices à partir de spécifications HAAD

présenté par

Etienne Ogoubi

a été évalué par un jury composé des personnes suivantes:

Michel Boyer

président-rapporteur

**Eduard Cerny**

directeur de recherche

**Guy Bois**

membre du jury

Mémoire accepté le 23 août 2002

# **Sommaire**

En informatique, le processus de vérification de systèmes numériques constitue un grand défi pour les chercheurs. Plusieurs études proposent un nombre très varié de solutions et de méthodes de vérification. Nos travaux portent sur une méthode qui permet de vérifier la conception et l'implementation des protocoles des bus synchones (exemple le PCI). Pour ce faire, nous convertissons les chronogrammes de spécifications des protocoles de bus en Diagrammes à Actions Annotés et Hiérarchiques (HAAD), puis en machines à états observatrices, qui sont utilisées pour observer les activités sur le bus en simulation, en émulation et en méthodes formelles. La machine observatrice signale une erreur si le protocole du bus est violé. Les machines observatrices sont codées en RTL synthétisable dans les languages de description Verilog ou VHDL. Pour illustrer notre méthode, nous utilisons un sous-ensemble du protocole du bus PCI.

Mots Clés: Diagrammes à Actions Annotés et Hiérarchique, Diagramme à Action Feuille, Diagramme à Action Hiérarchique, Machine à États Finis, Machine à États Observatrice, Machine à États Finis Synchrone et Temporisée (STFSM), Peripheral Component Interconnect (PCI), Protocole du Bus PCI.

# **Abstract**

Efficient design verification is a major preoccupation in hardware systems design. We report on a method that assists the verification of the implementations of synchronous bus protocols (e.g., PCI). To this end we convert a Timing Diagram specification of the protocol in the form of Hierarchical Annotated Action Diagrams (HAAD) into synchronous state machines - checkers that can be used to observe the activity on the bus during simulation, emulation or formal verification and signal an error signal if a protocol violation is detected. The checkers are coded in synthesizable RT-level Verilog or VHDL. We illustrate the method on a subset of the PCI bus protocol.

Key Words: Hierarchical Annotated Action Diagram (HAAD), Leaf Action Diagram (LAD), Hierarchical Action Diagram (HAD), Finite State Machines (FSM), Checker State Machine, Synchronous Timed Finite State Machines (STFSM), Peripheral Component Interconnect (PCI), PCI-Bus Protocol.

# Table Des Matières

|                                                                     | Pages |

|---------------------------------------------------------------------|-------|

| Sommaire                                                            | iii   |

| Abstract                                                            | iv    |

| Table des matières                                                  | v     |

| Liste des figures                                                   | ix    |

| Liste des signes et des abbréviations                               | xiii  |

| Chapitre 1 : Introduction                                           | 1     |

| 1.1. La vérification des systèmes numériques                        | 2     |

| 1.1.1. La simulation                                                | 2     |

| 1.1.2. Les méthodes formelles                                       | 3     |

| 1.1.3. Les méthodes symboliques                                     | 3     |

| 1.1.4. L'émulation                                                  | 4     |

| 1.2. Proposition de nouvelles solutions pour la vérification de bus | 5     |

| 1.3. Plan du mémoire                                                | 12    |

| Chapitre 2 : Spécification d'un système par le HAAD                 | 14    |

| 2.1. Introduction                                                   |       |

| 2.2. Diagrammes à actions annotés et hiérarchique (HAAD)            | 16    |

| 2.2.1. Diagrammes à actions feuille                                 | 16    |

| 2.2.2. Annotation des diagrammes feuilles                           | 22    |

| 2.2.3. Diagrammes à actions hiérarchiques                           | 23    |

| 2.2.4 Annotation des diagrammes hiérarchiques                       | 25    |

|   | 2.2.5. Description d'un diagramme à actions                        |            |

|---|--------------------------------------------------------------------|------------|

|   | feuille en langage HAAD                                            | 26         |

|   | 2.2.6. Diagrammes synchrones                                       | 28         |

|   | 2.3. Conclusion                                                    | 29         |

| _ |                                                                    |            |

| ( | hapitre 3 : Construction des machines observatrices à partir des   |            |

|   | spécifications HAAD                                                |            |

|   | 3.1. Introduction                                                  |            |

|   | 3.2. Décomposition des diagrammes feuilles                         | 32         |

|   | 3.2.1. La décomposition en parallèle d'un diagramme feuille        | 33         |

|   | 3.2.2. La décomposition en cascade d'un diagramme feuille          | 35         |

|   | 3.3. Machine à états finis synchrone et temporisée (STFSM)         | 40         |

|   | 3.4. La machine STFSM générique                                    | 46         |

|   | 3.5. Composition des STFSM en fonction des HAD                     | 50         |

|   | 3.5.1. Les équations de coordination des STFSM                     | 50         |

|   | 3.6. Conclusion                                                    | 55         |

|   |                                                                    |            |

| C | hapitre 4 : Validité de la méthode pour la synthèse des EFSM       | 56         |

|   | 4.1. Introduction                                                  |            |

|   | 4.2. Démonstration de modèle                                       |            |

|   | 4.2.1. Démonstration de modèle                                     |            |

|   | 4.2.2. Computation Tree Logic (CTL)                                |            |

|   | 4.3. Validité des STFSM génériques                                 |            |

|   | 4.3.1. Vérification du modèle STFSM générique                      |            |

|   | 4.3.2. Prototype de test pour le modèle générique du               |            |

|   | STFSM en verilog                                                   | 62         |

|   | 4.3.3. Spécification et vérification des propriétés pour le modèle | 02         |

|   | générique du STFSM                                                 | <i>(</i> ) |

|   | 4.3.4. Vérification des compositions des STFSM                     |            |

|   | 4.4. Conclusion                                                    |            |

|   | · · · Conclusion                                                   | 66         |

| Chapitre 5 : Étude du bus PCI: synthèse de EFSM observatrice et les    |         |

|------------------------------------------------------------------------|---------|

| résultats expérimentaux                                                | 67      |

| 5.1. Introduction                                                      | 67      |

| 5.2. Opérations sur le bus PCI                                         | 68      |

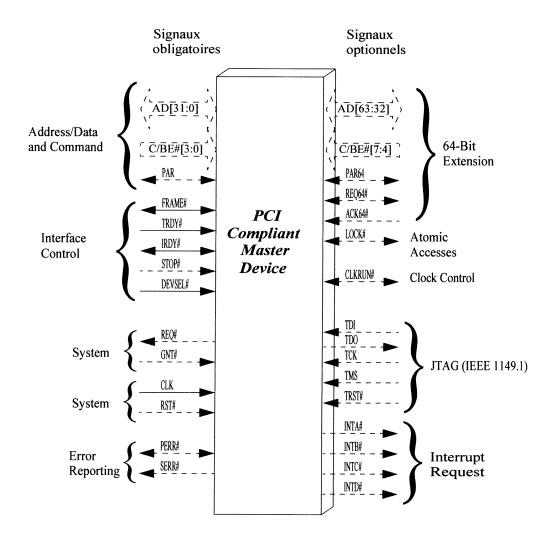

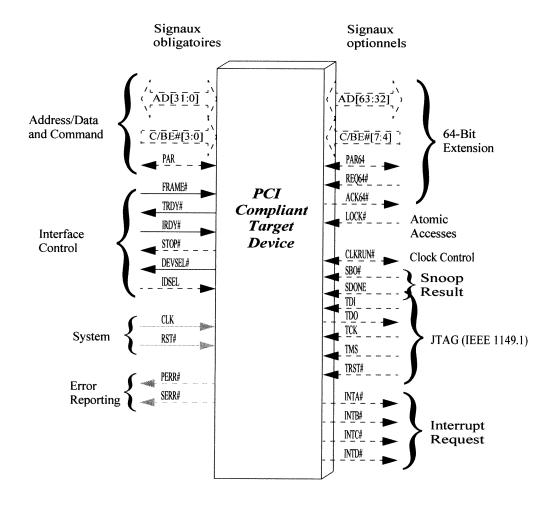

| 5.3. Les groupes des signaux fonctionnels du bus PCI                   | 69      |

| 5.3.1. Le signal d'horloge (CLK)                                       |         |

| 5.3.2. Les signaux de contrôle                                         |         |

| 5.4. Comportement des signaux de contrôle sur le PCI lors de la        |         |

| transaction de lecture                                                 | 73      |

| 5.5. Comportement des signaux de contrôle sur le PCI lors de la        |         |

| transaction d'écriture                                                 | 76      |

| 5.6. Interruptions prématurées des transactions sur le bus PCI         |         |

| 5.6.1. Les raisons pour lesquelles la source peut interrompre u        |         |

| transaction                                                            | 78      |

| 5.6.2. Les raisons pour lesquelles la destination peut interromp       | ore une |

| transaction                                                            | 80      |

| 5.7. Les contraintes temporelles lors d'une transaction sur le bus PCI | 82      |

| 5.7.1. Prévenir la monopolisation du bus par la source                 | 83      |

| 5.7.2. Prévenir la monopolisation du bus par la destination            | 83      |

| 5.8. Modèle HAAD synchrone des transactions de lecture et d'écritur    | e84     |

| 5.8.1. Traduction de la transaction de lecture en diagrammes           |         |

| feuilles transformables en STFSM                                       | 86      |

| 5.8.2. Traduction de la transaction d'écriture en diagrammes           |         |

| feuilles transformables en STFSM                                       | 95      |

| 5.9 Conclusion                                                         | 101     |

| Chapitre 6 : Conclusion - synthèse des EFSM observatrices à partir des HAAD | 102 |

|-----------------------------------------------------------------------------|-----|

| 6.1. Travaux accomplis                                                      | 103 |

| 6.2. Travaux à venir                                                        | 104 |

| Références                                                                  | 106 |

| Annexe                                                                      | xiv |

# Liste des Figures

|                          |                                                           | Page |

|--------------------------|-----------------------------------------------------------|------|

| FIGURE 1. M              | fachine Observatrice sur un bus lors de la vérification   |      |

| d'un                     | e transaction                                             | 7    |

| FIGURE 2. R              | ésumé de l'approche utilisée pour la synthèse de la       |      |

| macl                     | hine observatrice                                         | 9    |

| FIGURE 3. D              | iagramme à actions feuille représentant un fragment de    |      |

| la sp                    | écification de la fonction de lecture sur le PCI          | 17   |

| FIGURE 4. D              | iagramme à actions feuille avec des opérations            | 19   |

| FIGURE 5. R              | eprésentation graphique d'un diagramme à action feuille   |      |

|                          | ant en évidence les différents types de contraintes       | 22   |

| FIGURE 6. S <sub>I</sub> | pécification en langage HAAD du diagramme à actions       |      |

| feuill                   | le de la Figure 5                                         | 27   |

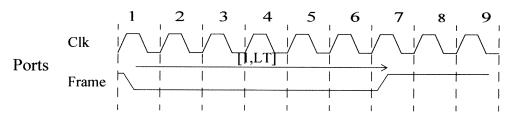

| FIGURE 7. Ex             | xemple de diagramme synchrone: Transaction réduite        |      |

| de le                    | cture sur le bus PCI                                      | 29   |

| FIGURE 8. Tr             | ransaction réduite de lecture sur le bus PCI représentant |      |

|                          | iagramme feuille f                                        | 33   |

| FIGURE 9. Ex             | remple de diagramme feuille résultant de l'application    |      |

| de la                    | règle 1 de la décomposition parallèle sur le diagramme f  | 34   |

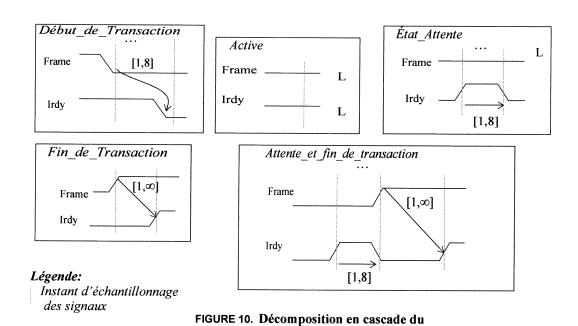

| FIGURE 10. De            | écomposition en cascade du diagramme feuille représenté   |      |

|                          | figure 9                                                  | 35   |

| FIGURE 11. Ex            | emple de diagramme feuille résultant de l'application     |      |

|                          | règle 3. i) de la décomposition cascade sur le diagramme  |      |

|                          | e de la 9                                                 | 26   |

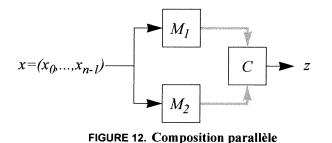

| FIGURE 12. | Composition parallèle37                                          |

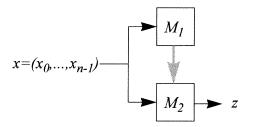

|------------|------------------------------------------------------------------|

| FIGURE 13. | Composition en cascade                                           |

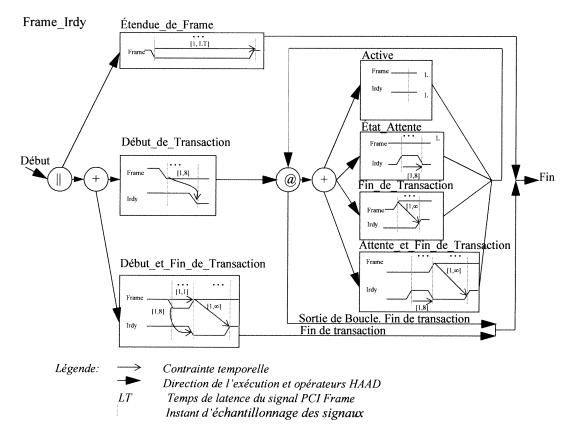

| FIGURE 14. | Modèle HAAD du fragment Frame_Irdy de la transaction             |

| d          | e lecture du bus PCI. Recomposition des fragments pour           |

| d          | onner fonctionnellement Frame_Irdy39                             |

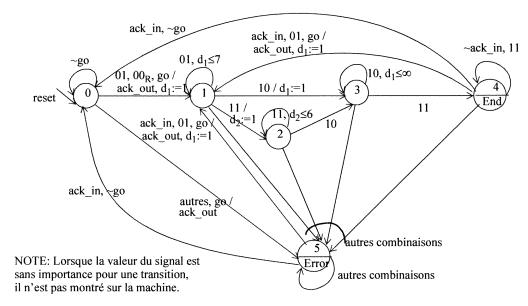

| FIGURE 15. | Exemple de STFSM: boîte Attente_et_Fin_de_Transaction            |

| d          | e la Figure 1046                                                 |

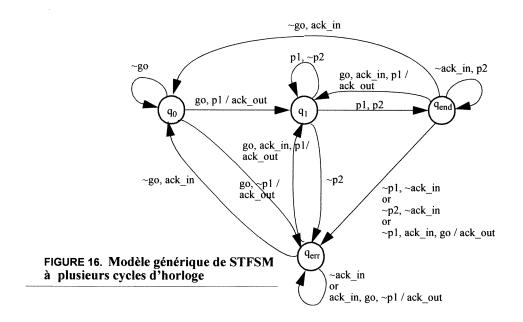

| FIGURE 16. | Modèle générique de STFSM à plusieurs cycles d'horloge48         |

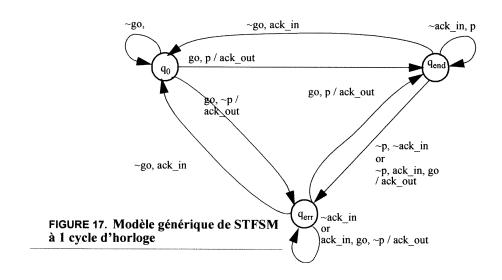

| FIGURE 17. | Modèle générique de STFSM à 1 cycle d'horloge48                  |

| FIGURE 18. | Description schématique de la composition en cascade de          |

| 2          | machines51                                                       |

| FIGURE 19. | Opération de boucle sur un STFSM à 1 cycle d'horloge54           |

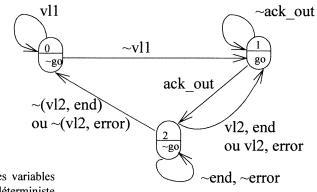

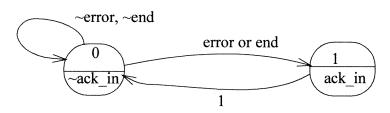

| FIGURE 20. | Machine à états pour générer le signal go60                      |

| FIGURE 21. | Machine à états réflecteur du signal ack_in60                    |

| FIGURE 22. | Schéma de prototype de test pour le modèle générique du STFSM63  |

| FIGURE 23. | Représentation schématique d'un agent source du bus PCI70        |

| FIGURE 24. | Représentation schématique d'un agent destination du bus PCI71   |

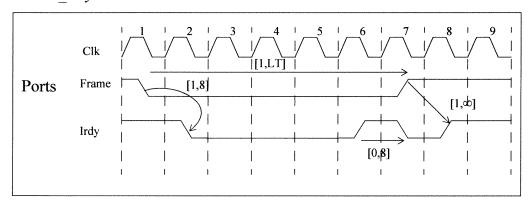

| FIGURE 25. | Chronogramme de la transaction de lecture sur le bus PCI         |

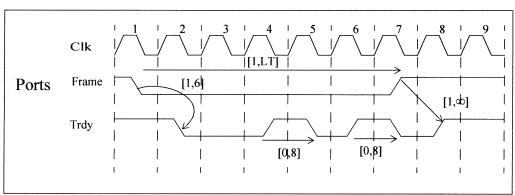

| FIGURE 26. | Chronogramme de la transaction d'écriture sur le bus PCI         |

| FIGURE 27. | Modèle HAAD des transactions de lecture et d'écriture sur        |

| le         | bus PCI84                                                        |

| FIGURE 28. | Diagramme à action de la transaction de lecture sur le bus PCI85 |

| FIGURE 29. | Diagramme à action de la transaction d'écriture sur le bus PCI85 |

|            | Diagramme feuille Frame_Irdy issu de la décomposition            |

|            | rallèle de la figure 2886                                        |

|            | Diagramme feuille Frame_Trdy issu de la décomposition            |

|            | rallèle de la figure 2887                                        |

| FIGURE 32. | Diagramme feuille Frame_Devsel issu de la décomposition          |    |

|------------|------------------------------------------------------------------|----|

| pa         | arallèle de la figure 28                                         | 87 |

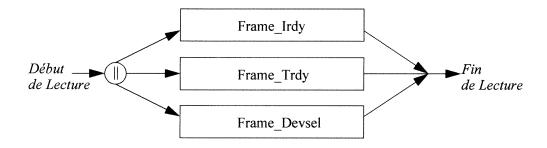

| FIGURE 33. | Composition parallèle de diagrammes feuilles réduits issus de la |    |

| d          | écomposition de la figure 28                                     | 88 |

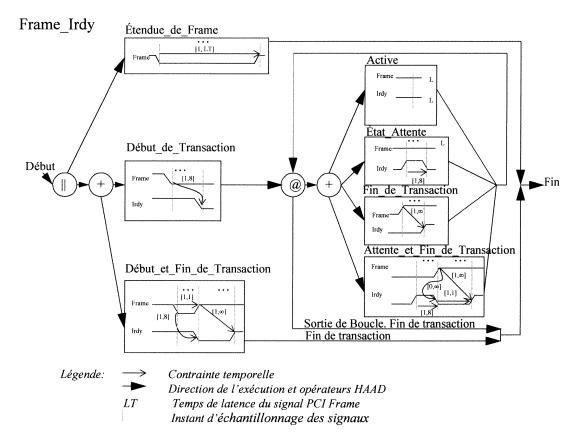

| FIGURE 34. | Modèle HAAD du fragment Frame_Irdy de la transaction de          |    |

| le         | cture du bus PCI                                                 | 89 |

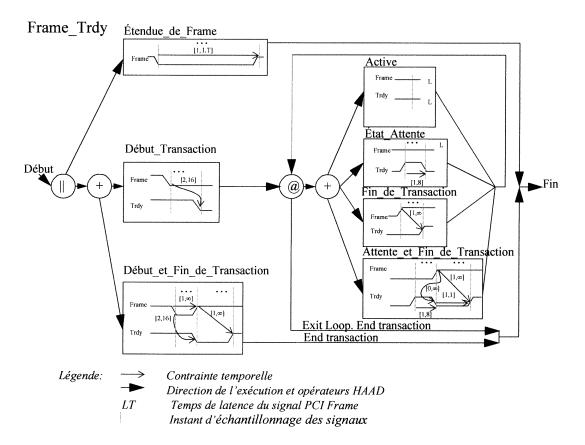

| FIGURE 35. | Modèle HAAD du fragment Frame_Trdy de la transaction de          |    |

| le         | cture du bus PCI                                                 | 90 |

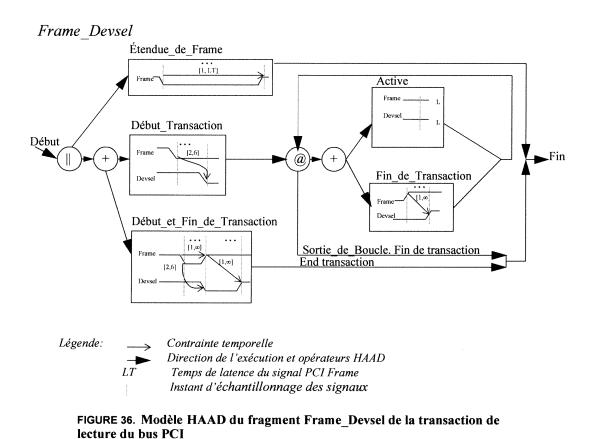

| FIGURE 36. | Modèle HAAD du fragment Frame_Devsel de la transaction de        |    |

| le         | cture du bus PCI                                                 | 91 |

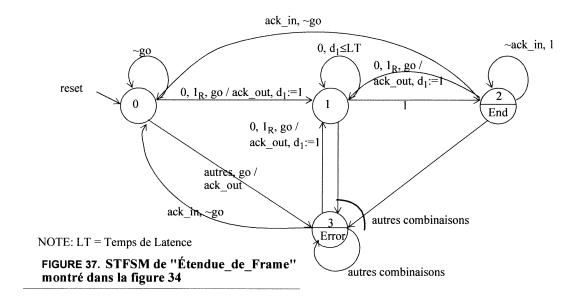

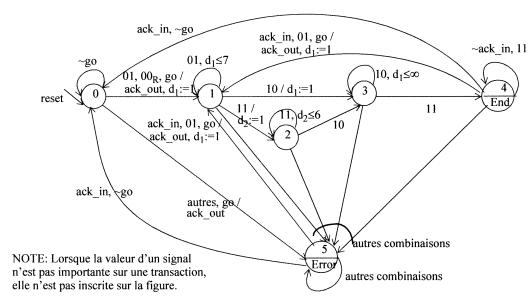

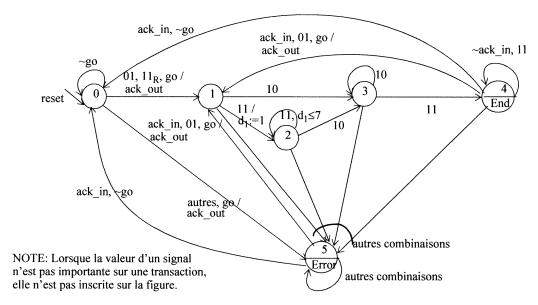

| FIGURE 37. | STFSM de "Étendue_de_Frame" montré dans la figure 34             | 92 |

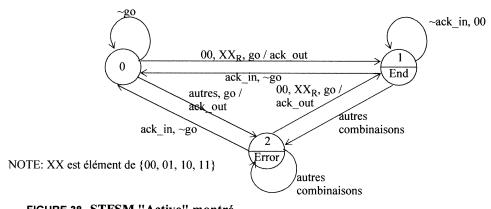

| FIGURE 38. | STFSM "Active" montré dans la figure 34                          | 92 |

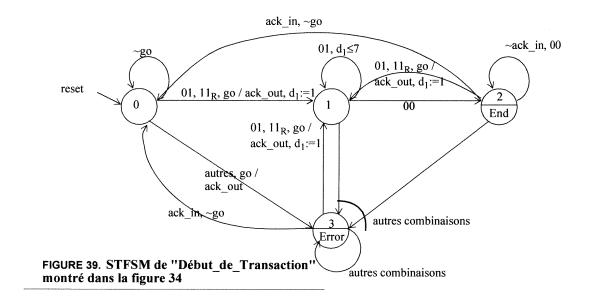

| FIGURE 39. | STFSM de "Début_de_Transaction" montré dans la figure 34         | 93 |

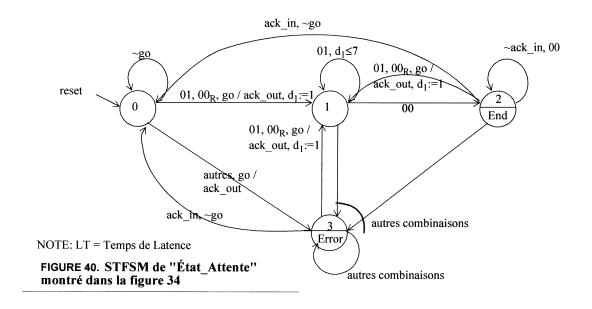

| FIGURE 40. | STFSM de "État_Attente" montré dans la figure 34                 | 93 |

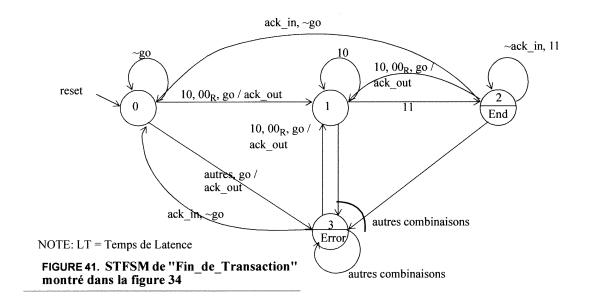

| FIGURE 41. | STFSM de "Fin_de_Transaction" montré dans la figure 34           | 94 |

| FIGURE 42. | STFSM de "Attente_et_Fin_de_Transaction" montré dans la          |    |

| fig        | ure 34                                                           | 94 |

| FIGURE 43. | STFSM de "Début_et_Fin_de_Transaction" montré dans la            |    |

| fig        | ure 34                                                           | 95 |

| FIGURE 44. | Diagramme feuille Frame_Irdy issu de la décomposition            |    |

| par        | rallèle de la figure 29                                          | 96 |

| FIGURE 45. | Diagramme feuille Frame_Trdy issu de la décomposition            |    |

| par        | allèle de la figure 29                                           | 96 |

| FIGURE 46. | Diagramme feuille Frame_Devsel issu de la décomposition          |    |

| par        | allèle de la figure 29                                           | 97 |

|            | Composition parallèle de diagrammes feuilles réduits issus de la |    |

| déc        | composition de la figure 25                                      | 97 |

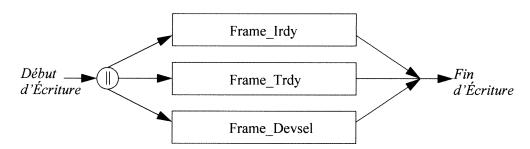

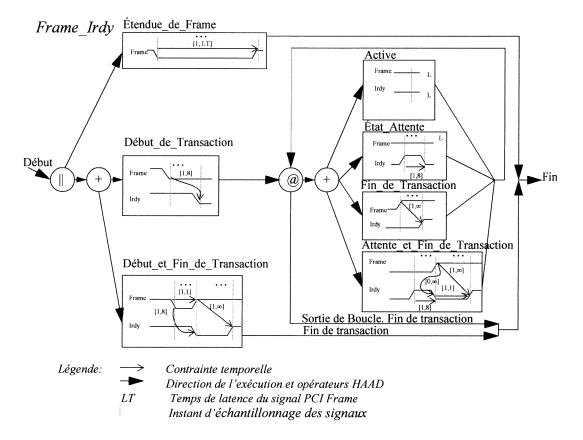

| FIGURE 48. 1 | Modèle HAAD du fragment Frame_Irdy de la transaction   |     |

|--------------|--------------------------------------------------------|-----|

| d'éd         | criture du bus PCI                                     | 98  |

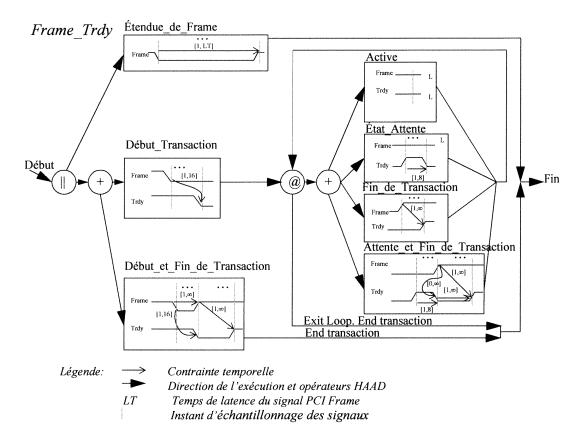

| FIGURE 49. N | Modèle HAAD du fragment Frame_Trdy de la transaction   |     |

| d'éc         | criture du bus PCI                                     | 99  |

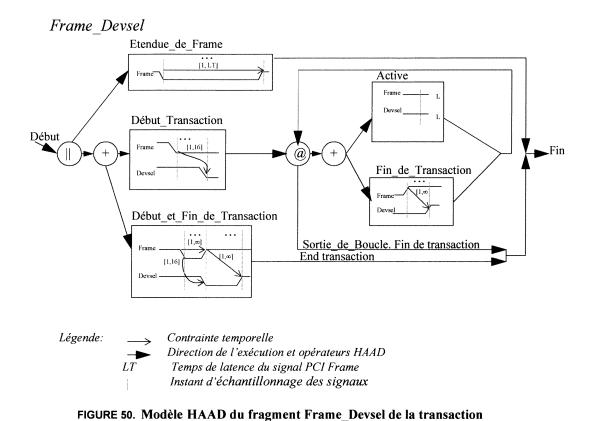

| FIGURE 50. N | Modèle HAAD du fragment Frame_Devsel de la transaction |     |

| d'éc         | criture du bus PCI                                     | 100 |

# Liste des signes et abbréviations

EFSM Extended Finite State Machine

HAAD Hierarchical Annoted Actions Diagram

HAD Hierarchical Actions Diagram

IP Intellectual Property

LAD Leaf Actions Diagram

PCI Peripheral Component Interconnect

RTL Register-Transfer Level

STFSM Synchronous Timed Finite State Machine

TD Timing Diagram

# Remerciements

Je rends grâce à Dieu en notre Seigneur Jesus Christ pour toutes ces années.

Il y a un temps pour toute chose. Un temps pour commencer, et un temps pour finir ce qu'on a commencé. D'après la citation de Hudson Taylors, il y a trois étapes dans le cycle de vie de toute tâche: l'imposibilité, la difficulté et l'accomplissement.

Pour ma part, ce travail aurait été impossible sans l'aide de personnes spéciales. Je pense particulièrement au professeur Eduard Cerny, mon directeur. Je tiens à le remercier sincèrement pour m'avoir donné ce sujet, et avoir toujours été là pour moi. Chaque fois que j'ai franchi le seuil de son bureau, il a toujours été disponible pour aider, conseiller, soutenir, encourager et lorsque c'était nécessaire, reprimander et remettre les choses sur les rails. Je tiens à le remercier davantage pour le généreux soutien financié qu'il m'a accordé. Ce soutien est d'autant plus apprécié que cela est arrivé à un moment où j'étais prêt à tout laisser tomber par manque de moyens financiers.

Le professeur Eduard Cerny est tout simplement le meilleur directeur qu'un étudiant puisse souhaiter avoir.

Je remercie ma très chère Lady pour son aide. Son soutien de tous les jours est apprécié.

Je remercie mon ami Moustapha Azizi, le temoin attentif de mes nuits blanches au laboratoire, le soutien infaillible de la vérification de la méthode que nous avons proposée, et de la préparation de mes conférences.

Je remercie aussi mon ami Ismaël Ben Barka et ses parents qui m'ont soutenu sur beaucoup de plans, pour les bons moments et les privations que nous avons partagés au 1160 rue St. Mathieu à Montréal.

La rédaction du mémoire a été difficile lorsque je suis allé à Nortel Networks pour le projet OPC. Le travail à Nortel est tellement absorbant et épuisant que je me suis demandé si je finirais un jour mon mémoire. À Nortel, j'ai eu le soutien et les encouragements de plusieurs personnes comme Bogdan Boruslawski, Michel Langevin, David Fisher, David Carpenter, Paul Welton, et bien d'autres.

Finalement, l'accomplissement de ce mémoire est une reconnaissance à mes parents, surtout à mon père, Emile Koffi Ogoubi, pour qui j'ai beaucoup d'affection et de qui j'ai beaucoup reçu.

# CHAPITRE 1 Introduction

The work actually began in 1969 when Intel agreed to build some chips for a Japanese calculator company. In the course of my work at Intel, I had occasion to look at the design for those chips and I felt it could be improved. One of the ways to improve it was to replace the chip family with a single chip general purpose computer and memory to contain programmes that would then programme that computer to perform the calculator functions. That basically is how the first microprocessor started.

T. Hoff, Monaco, 30-10-1996

De nos jours, le développement des systèmes électroniques a comme principal défi la vérification fonctionnelle. La complexité des systèmes microélectroniques et l'augmentation considérable du nombre de portes logiques dans les puces ont entrainé *de facto* une augmentation des efforts de vérification; 60% à 80% des efforts économiques et temporels dans le cycle de développement d'un système sont consacrés à la vérification. Pour réduire ces efforts de développement, plusieurs méthodes ont été créées, d'abord lors de la synthèse des systèmes et ensuite lors de leur vérification. Sur le plan de la synthèse, nous remarquons la construction de blocs fonctionnels spécifiques (Intellectual Property (IP) blocs), réutilisables dans la composition de systèmes plus complexes. Pour lier ces blocs fonctionnels, il est indispensable de définir des protocoles de communication appropriés pour le bus qui joue le rôle de liaison, et de vérifier ensuite si les blocs respectent les protocoles spécifiés pour ce bus. L'objectif ici n'est pas la vérification des composants qui participent à la communication, mais celle de leur comportement sur le bus qui les lie.

Sur le plan de la vérification, plusieurs méthodes utilisent de nouvelles approches de simulation et des méthodes formelles en combinant la simulation, l'émulation et les méthodes formelles pour s'assurer que le comportement des IPs connectés aux bus respectent leurs spécifications.

## 1.1. La vérification des systèmes numériques

La vérification est considérée comme l'ensemble des moyens mis en oeuvre pour s'assurer qu'un système numérique est conforme à sa spécification, tant aux points de vue qualitatif (l'ordre des événements), quantitatif (conservation de l'information traitée), que temporel (le comportement par rapport au temps). Nous distinguons trois grandes classes de méthodes de vérification: la *simulation*, les *méthodes formelles* et *symboliques*, et l'*émulation*.

#### 1.1.1. La simulation

Par définition, la simulation est soit une reproduction expérimentale des conditions réelles dans lesquelles une opération complexe s'est produite, soit une représentation d'un système par un modèle analogue plus facile à étudier.

Techniquement, la méthodologie de la simulation consiste à soumettre à un système numérique réactif un ensemble de données appelé *stimuli* en entrée et à analyser les résultats de la réaction de ce système en sortie. Il faut ensuite déterminer si le comportement du système par rapport aux *stimuli* respecte ses spécifications.

Pour être efficace, le principe de la simulation doit tenir compte de toutes les combinaisons possibles des *stimuli*. Cependant, un problème se pose lorsqu'il s'agit de vérifier des systèmes numériques plus ou moins complexes. Le nombre de configurations (entrée, sortie) résultant de la combinaison des données des *stimuli* devient exponentiellement élevé. La simulation exhaustive se révèle alors trop longue et très coûteuse.

Une solution au problème de la simulation est l'utilisation de méthodes formelles qui sont considérées comme plus rigoureuses.

#### 1.1.2. Les méthodes formelles [20]

Les méthodes formelles dans la conception des systèmes numériques représentent un ensemble de principes basé sur des approches mathématiques qui permettent d'établir formellement qu'une implémentation satisfait à sa spécification. Depuis l'avènement des méthodes formelles, des moyens comme la "preuve de théorèmes" et surtout la "vérification d'équivalence" et la "vérification de modèle" ont émergé comme des solutions pratiques pour certains aspects des problèmes de la vérification. Ces moyens peuvent être appliqués a posteriori (test, preuve, vérification et mesures) ou en cours de conception (validation de spécification, création de maquettes, dérivation et synthèse, prédiction des performances). Les références [10], [27], [18], [55], [22] et [45] sont des exemples d'études et d'applications des méthodes formelles.

Plusieurs travaux ont été réalisés afin de répondre aux questions sur le niveau d'abstraction de la description et sur les méthodes alternatives pour la vérification des propriétés des processeurs [22], [45], [53], [47]. D'autres méthodes ont été développées [55], [37] pour faciliter les spécifications et la vérification des systèmes numériques utilisant des chronogrammes (Timing Diagrams).

Bien que les méthodes formelles aient apporté une amélioration à la vérification de systèmes numériques par rapport à la simulation, cette amélioration reste néanmoins insuffisante.

#### 1.1.3. Les méthodes symboliques [33]

Les méthodes symboliques ont émergé comme solutions alternatives à la simulation et aux méthodes formelles. Elles consistent en une représentation compacte et symbolique des données à propager, alors que la simulation utilise la propagation des valeurs de ces données à travers le système. Les configurations sont alors basées sur

des ensembles de valeurs qui regroupent des données relatives. Dans ce cas, le nombre de configuration diminue considérablement. Les mêmes approches sont utilisées en méthodes formelles symboliques. Par exemple, Berkane et Cerny [44] pour explorer l'espace des états d'un automate temporisé, raisonnent en terme de zones temporelles relatives, ce qui consiste en un regroupement des états de l'automate dans des ensembles. Dans le même ordre d'idée, Bryant présente une nouvelle méthode dite "simulation symbolique" dans la référence [26], qui consiste à utiliser des valeurs symboliques spéciales pour encoder un ensemble de conditions d'opération d'un circuit éléctronique. Cette méthode peut-être appliquée à la fois à la vérification logique et temporelle. Par ailleurs, Seger et Bryant présentent dans la référence [50] une version modifiée de la simulation symbolique appelée "évaluation symbolique de trajectoire" (STE - Symbolic Trajectory Evaluation), dans laquelle les propriétés d'un système sont exprimées dans une forme restrainte de la logique temporelle. L'expression de la logique utilisée est limitée à la description des propriétés temporelles de circuits et à celle de leur transition des états. L'algorithme de décision utilisé par l'évaluation symbolique de trajectoire teste la validité d'une assertion en déterminant si oui ou non tout comportement causé par une séquence d'états qui satisfait un antécédent est un comportement qui satisfait son conséquent. Plusieurs autres travaux sur les méthodes symboliques ont été développés, comme les algorithmes itératifs proposés par Wong-Toi et Dill [41] qui opèrent sur des approximations de l'ensemble des propriétés temporelles du système.

#### 1.1.4. L'émulation

Étymologiquement, l'émulation, du latin æmulatus, veut dire imiter ou exceller. L'émulation des systèmes numériques est considérée aujourd'hui comme la solution là où la simulation et les méthodes formelles et symboliques ont échoué. Elle consiste en l'interconnection d'un ensemble de puces électroniques reprogrammables, comme les FPGA (Field-Programmable Gate Arrays), et d'un ensemble de logiciels de synthèse et d'analyse, qui permettent de créer rapidement des représentations de systèmes

numériques ou des ASIC (Application Specific Integreated Circuits) au niveau matériel. Cette technique peut être utilisée très tôt pour vérifier exactement le système lors de sa conception. Elle permet aussi de détecter rapidement et exactement des erreurs à des niveaux d'abstraction très élevés ou à des niveaux portes logiques dans des circuits de plusieurs centaines de milliers, voire de millions de portes. Beaucoup de techniques dans le domaine de l'émulation logique ont été développées comme le SFE (Serial Fault Emulation) de la compagnie Meta Systems. Le SFE consiste à emuler séparément chaque circuit erronné du niveau "blocs fonctionnels" jusqu'au niveau "signaux" afin de déterminer des fautes ou des bloquages de signaux dans un état quelconque.

Bien que l'émulation soit vue comme solution d'avenir pour la vérification de systèmes numériques, plusieurs problèmes se posent toujours et les travaux pour réduire les efforts de vérification ne cessent de se diversifier.

Dans nos travaux, nous nous sommes intéressés à la vérification de bus, comme le PCI, qui permettent de lier plusieurs composants d'un système numérique.

## 1.2. Proposition d'une solution pour la vérification de bus

Dans le cas de la validation du protocole d'un bus, une des façons les plus simples de vérifier si les éléments numériques liés par ce bus respectent les spécifications de ce protocole en utilisant la simulation, l'émulation ou les méthodes formelles, est de connecter un observateur du protocole au bus. Cet observateur observe les activités sur le bus et signale toute violation du protocole de ce dernier. Le but de notre travail est de construire ce modèle observateur pour un bus synchrone à partir de sa spécification sous forme de Diagramme d'Actions Annotés Hiérarchiques ou HAAD [59].

Dans la référence [59], les auteurs présentent la méthode HAAD comme des scénarios de comportements finis ou de diagrammes qui, étant donnée une encapsulation appro-

priée, peuvent être composés pour former une description hiérarchique d'un comportement fini ou infini (cyclique). Par ailleurs, la méthode HAAD permet de généraliser la notion de chronogramme en incluant les signaux ou les ports de tous genres. L'attribution d'une valeur à un port est appelée ici une action. Une action peut représenter un changement de valeur sur un port (une transition ou un événement) ou peut être une mise à jour d'un signal sur un port sans nécessairement changer sa valeur. Les chronogrammes sont appelés dans la méthode HAAD, Diagramme à Action Feuille et Hiérarchique. Ces Diagrammes peuvent être annotés par des variables, des appels de procédures, etc., d'où vient le nom de Diagrammes d'Actions Annotés Hiérarchiques (Hiérarchical Annotated Action Diagrams (HAAD)).

Le modèle observateur synthétisé à partir des spécifications HAAD est implémenté sous la forme de machine à états finis étendue (Extended Finite State Machine (EFSM)) qui est décrite en langages HDL Verilog (ou VHDL) synthétisable et synchrone [60] [17] [52].

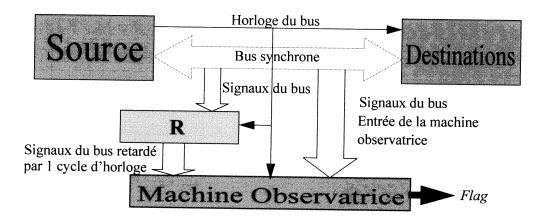

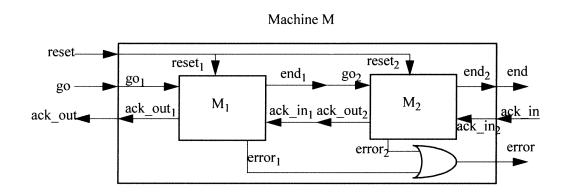

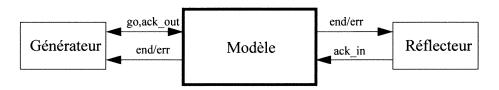

Lorsqu'elle est utilisée en émulation, la machine observatrice est instanciée avec le modèle du bus et connectée à ses ports d'entrée et de sortie, en les observant seulement. L'observateur génère un signal booléen qui indique si le comportement qui a été observé sur les ports du bus est conforme ou non à la spécification HAAD de ce bus. Figure 1.

Note: R est un régistre qui conserve les événements antérieurs à un cycle d'horloge du bus

FIGURE 1. Machine Observatrice sur un bus lors de la vérification d'une transaction

La figure 1 est une représentation schématique d'une machine observatrice instanciée sur un bus afin qu'elle observe son comportement. L'initiateur de la transaction, représenté par la boîte *source* et les *destinations*, sont synchrones à l'horloge du bus. Toute transaction sur le bus synchrone est observée par la machine observatrice, comparée avec la transaction précédente (cycle d'horloge précédente) et enregistrée dans le registre R pour déterminer si la progression des événements est conforme à la spécification. Sur la figure 1, la machine observatrice est connectée au bus par l'ensemble des signaux que nous avons appelé "*Signaux du bus*, *entrée de la machine observatrice*". De même, le registre R est connecté à un ensemble de signaux appelé "*Signaux du bus*, *entrée du registre R*".

Dans la référence [37], les auteurs indiquent qu'ils peuvent produire des spécifications en logique temporelle à partir de leur dialecte de diagrammes temporels. Ceci aurait pu aider à l'approche que nous avons utilisée pour la méthode de la synthèse des

machines observatrices. Toutefois, le style de la spécification est limité par rapport aux contraintes temporelles et ne tient pas compte de certains comportements spécifiques.

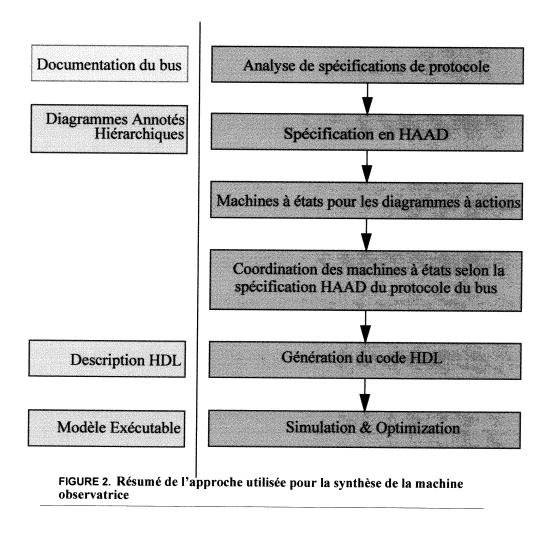

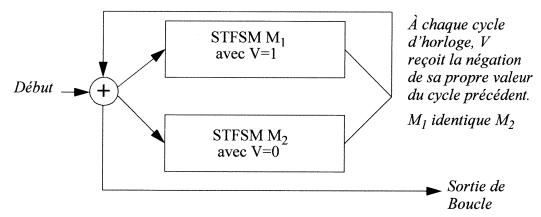

Notre approche peut être résumée comme suit, voir figure 2. Très souvent les spécifications des protocoles de bus sont des fragments de chronogrammes et de longues descriptions verbales. Premièrement, nous avons proposé de transformer ces spécifications dans des formats - HAAD - de chronogrammes plus complets et plus rigoureux. Ceci implique une subdivision des transactions du bus en des chronogrammes fonctionnels plus petits en utilisant des diagrammes à actions feuilles (Leaf Action Diagrams (LAD)) [59] pour ensuite les combiner en utilisant les opérateurs de la composition hiérarchique du HAAD. L'étape la plus difficile de cette démarche est celle de transformer les spécifications de protocoles en spécifications HAAD, dans la mesure où les spécifications des protocoles sont objets à des interprétation subjectives, à des incomplétudes et à des ambiguïtés. Les diagrammes à actions feuilles (LAD) de la spécification HAAD décrivent les transitions sur les signaux et les contraintes temporelles entre elles. Ces LADs sont alors transformés en Machines à États Finis Synchrones Temporisées (Synchronous Timed Finite State Machines (STFSM)), qui peuvent s'étendre à des opérations de données si la spécification du HAAD est annotée. Toutes les machines à états des diagrammes feuilles fonctionnent de manière concurrente. Les diagrammes à actions hiérarchiques (HAD) qui lient les diagrammes feuilles (LAD) de la définition de protocole HAAD sont utilisés pour imposer la coordination des opérations des machines à états LAD, en utilisant des signaux dérivés des valeurs des états de ces machines et des opérateurs hiérarchiques spécifiques. Le réseau de machines à états STFSM ainsi créé devient un réseau de machines à états finis étendus EFSM, dans lequel les variables temporelles de ces machines sont implémentées comme des compteurs réinitialisables des pulsions de l'horloge du système, et ensuite converti dans un langage synthétisable synchrone c'est-à-dire Verilog ou VHDL pour produire un modèle RTL de la machine observatrice. Aucune action du bus n'est générée par la machine observatrice. Elle n'a qu'une seule sortie (flag) qui

reste initialisée à 0 (*Pas d'erreur*) et garde cette valeur tant que la spécification du protocole de communication n'est pas violée. Chaque fois que le protocole de communication est violé, le signal en sortie de l'observateur devient 1 (*erreur*).

La synthèse des machines à états, comme celle des contrôleurs d'interface à partir des chronogrammes, a fait l'objet de plusieurs recherches qui ont commencé avec la thèse de G. Borriello [19], et ont pris de l'importance avec la co-vérification matériels-

logiciels (HW/SW) et la synthèse des systèmes basée sur les IP. Toutefois, la technique présentée par Borriello dans sa thèse pourrait être potentiellement utilisée dans la synthèse de la machine observatrice si elle pouvait tenir compte de la hiérarchie complexe de la spécification HAAD. D'autre part, dans la référence [56], Delgado et al. présentent comment convertir des chronogrammes synchrones isolés en des propriétés en logique temporelle. Cette approche aussi aurait pu être utilisé dans la synthèse des machines observatrices, mais comme dans le cas de la méthode de Borriello, celle-ci ne peut pas accepter des spécifications complètes et exécutables des protocoles de bus sous la forme HAAD, en particulier lorsque les diagrammes sont composés par les opérations de composition hiérarchique. Il existe plusieurs autres techniques pour déduire des protocoles à partir de la dérivation des structures d'implémentation comme l'interconnexion des composantes à partir de la spécification de système [19] [58] [36] [29]. Ces méthodes ainsi décrites pouvaient nous aider pour la construction du protocole de communication entre les diagrammes à actions feuilles (LAD), pour en faire une machine observatrice. Mais dans notre cas, la structure de communication est spécialisée, régulière et récursive, et les techniques générales de synthèse ne lui sont pas appropriées. Bref, un modèle HAAD a une hiérarchie comportementale et non structurale.

Pour prouver l'exactitude de la méthode proposée pour la synthèse de machines observatrices des protocoles de bus, nous l'avons vérifiée formellement en utilisant des modèles abstraits.

La vérification de l'exactitude de la méthode pour la synthèse de la machine à états observatrice est faite en deux étapes: la vérification par simulation et celle par méthodes formelles. Pour ce faire, nous avons développé des modèles abstraits de la machine observatrice. Ces modèles sont comme des moules dont les structures servent à construire les machines STFSM et permettent de vérifier leur exactitude.

La simulation seule ne permet pas de vérifier les opérations de synchronisation pour un protocole arbitraire, c'est-à-dire un protocole qui spécifie une hiérarchie HAAD arbitraire, et d'affirmer sans équivoque son exactitude. C'est la raison pour laquelle, pour vérifier que les équations de synchronisation que nous avons proposées sont toujours vraies dans toutes les situations, nous avons utilisé une méthode formelle (vérification de modèle). Nous avons utilisé un modèle abstrait des diagrammes à actions feuille dans lequel nous avons introduit des signaux de synchronisation qui sont différents des signaux du bus et qui ne participent pas aux activités de ce dernier. Ensuite, nous avons utilisé une approche de composition que nous avons vérifiée par VIS, un vérificateur de modèle [3]. La vérification comporte les phases suivantes:

- 1. Le modèle abstrait satisfait les propriétés des équations de synchronisation, et

- 2. La propriété des équations de composition des machines à états représentées par les instances des modèles abstraits des diagrammes à actions feuilles doit être préservée. Ceci veut dire que les interfaces d'une machine représentant une interconnexion de STFSM doivent êtres équivalentes aux interfaces des STFSM ellesmêmes. Ceci nous permet de parler d'une encapsulation récursive.

De ce fait, nous pouvons affirmer et conclure que les machines à états qui font partie du réseau que constitue la machine observatrice sont correctement synchronisées, quelque soit la hiérarchie HAAD donnée.

Les spécifications abstraites et les vérifications hiérarchiques ont permis de travailler sur des circuits de densité très grande, par des approches indirectes. Ces approches sont possibles grâce à la preuve par théorème et à la vérification de modèles comme celles présentées dans les références [10] [43] [23]. Notre modeste contribution est de montrer comment ces techniques peuvent être utilisées pour démontrer l'exactitude de protocoles de synchronisation dans un réseau de machines à états qui implémente une hiérarchie comportementale arbitraire.

#### 1.3. Plan du mémoire

La suite de ce document se présente comme suit:

Dans le chapitre 2, nous faisons un résumé de la méthode de diagrammes annotés à actions hiérarchiques -HAAD-. Nous présentons premièrement les diagrammes à actions de type feuille qui constituent la base de cette méthode. Les diagrammes feuilles sont des chronogrammes classiques augmentés de données et de procédures. Nous présentons dans la deuxième partie de ce chapitre les diagrammes hiérarchiques qui permettent de composer les diagrammes feuilles pour en faire des spécifications complètes. Nous donnons dans la dernière partie de ce chapitre une brève description des diagrammes à actions hiérarchiques synchrones.

Dans le chapitre 3, nous présentons la méthode de construction de la machine à états observatrice. Nous définissons en premier lieu une machine appelée *machine à états finis synchrone temporisée (STFSM)* et la traduction d'un diagramme feuille en STFSM. Nous parlons ensuite de la coordination des STFSM en fonction des diagrammes à actions hiérarchiques, et enfin de la construction de machines STFSM pour les différentes opérations hiérarchiques.

Dans le chapitre 4, nous présentons la vérification de la méthode pour la synthèse de la machine à états observatrice. Ce chapitre est composé de deux parties principales, à savoir: la vérification des STFSM génériques et la vérification de la composition des STFSM en fonction des opérateurs HAAD.

Dans le chapitre 5, nous appliquons la méthode de la synthèse des machines à états observatrices aux fonctions de lecture et d'écriture du bus PCI. Nous donnons premièrement une description des opérations de lecture et d'écriture sur le bus PCI en nous basant sur les signaux de contrôle du bus. Nous présentons également dans la suite de ce chapitre la décomposition des fonctions de lecture et d'écriture en sous

fonctions, selon leur spécification HAAD, leur traduction en machines à états synchrones temporisées et leur composition pour créer une machine à état observatrice.

Nous concluons ce mémoire avec le chapitre 6 dans lequel nous résumons toutes les étapes que nous avons parcourues lors de ce projet et nous proposons une extension de ces travaux aux éléments de la méthode HAAD qui n'ont pas été traités dans ce projet. Nous proposons aussi des perspectives pour des travaux futurs à savoir le développement d'un compilateur de HAAD pouvant générer des codes source RTL pour la synthèse de la machine observatrice.

Avant de parler de la synthèse de la machine observatrice, nous présentons dans le chapitre suivant la méthode HAAD [1] sur laquelle se base notre projet.

# Spécification d'un système par le HAAD

About 1000 instructions is a reasonable upper limit for the complexity of the problems now envisioned.

- Herman Goldstine and John Von Neumann (1946)

#### 2.1. Introduction

Les méthodes traditionnelles de spécification d'un système numérique sont basées sur la description informelle ou semi-formelle, en anglais pour la plupart, et sur des chronogrammes (Timing Diagrams - TD). Ces méthodes se sont avérées insuffisantes et incomplètes avec l'évolution prodigieuse des systèmes numériques, et la complexité de plus en plus grande de leurs fonctions, dans la mesure où les spécifications informelles sont le plus souvent sujettes à confusion et que les chronogrammes ne représentent que partiellement une fonction et une seule à la fois.

Bien concevoir un système commence par une spécification claire et adéquate qui représente le système dans son ensemble. L'évolution des systèmes numériques et leur complexité nous mène à proposer des techniques de spécifications formelles et rigoureuses pour leur conception.

La spécification formelle a pour objectif de décrire le comportement d'un système et de ses propriétés avant sa mise en oeuvre. Ces techniques sont plus souvent utilisées dans le cas des systèmes critiques (c'est-à-dire ceux pour lesquels le coût d'une erreur de fonctionnement est largement supérieur au coût de la conception) car il est alors possible de raisonner sur la spécification (prouver des propriétés) et de la vérifier avant l'implémentation du système.

La spécification formelle utilise un langage dont la syntaxe et la sémantique sont basées sur des procédés mathématiques. Bien que les propriétés des systèmes numériques incluent les comportements fonctionnels et temporels, les performances et les structures internes, leur spécification n'a connu un succès qu'en ce qui concerne les propriétés fonctionnelles. La tendance actuelle est d'intégrer différents langages de spécification, chacun capable de traiter différents aspects, de manipuler les performances, les contraintes temporelles et les contraintes de sécurité et architecturales de ces systèmes.

Plusieurs formalismes ont été utilisés pour représenter les spécifications à savoir:

- 1. La logique classique, la logique propositionnelle, la logique des prédicats de premier ordre, la logique d'ordre supérieur, la logique temporelle, etc...

- 2. Les automates à états finis sur des mots finis, les automates à états finis sur des mots infinis, les automates temporisés, etc...

Des méthodes formelles, telles que le Z, VDM et Larch [32], permettent de spécifier le comportement de systèmes séquentiels. Les états sont décrits en structures mathématiques ensemblistes (relations, fonctions). Les transitions sont données en terme de "pré" et "post" conditions. D'autres méthodes comme le Constraint Satisfaction Problem (CSP) [34], le Constraint Logic Programming (CLP) [8] [42], les logiques temporelles et les automates à entrées/sorties se concentrent sur la spécification des systèmes concurrents.

Un autre aspect des techniques de spécification est l'acte de décrire précisément les choses et d'obtenir une profonde compréhension du système; cela élimine des inconsistances, des ambiguïtés et des incomplétudes.

La méthode HAAD, dont la présentation se fait dans la suite de ce chapitre, est une description formelle et intuitive de diagrammes temporisés, vus comme des *scénarios* de comportements d'un système qui, en leur donnant des encapsulations appropriées, peuvent être composés pour donner une description finie ou infinie (cyclique) d'un comportement d'un système [59]. Cette méthode est constituée de deux niveaux de description: *les diagrammes à actions de feuilles et les diagrammes à actions hiérarchiques*.

### 2.2. Diagrammes à actions annotés et hiérarchiques (HAAD)

#### 2.2.1. Diagrammes à actions feuille

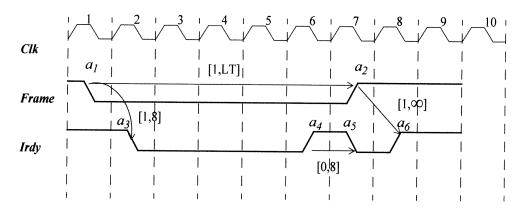

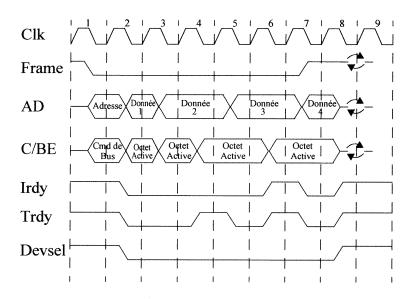

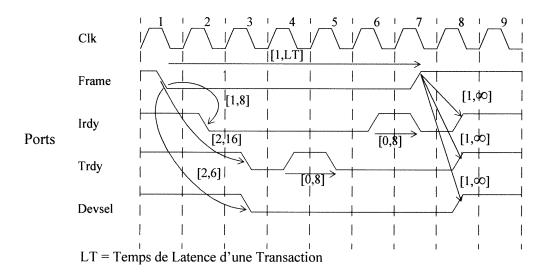

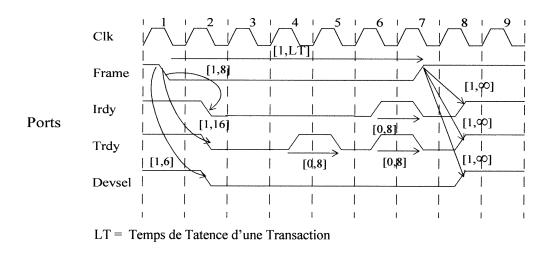

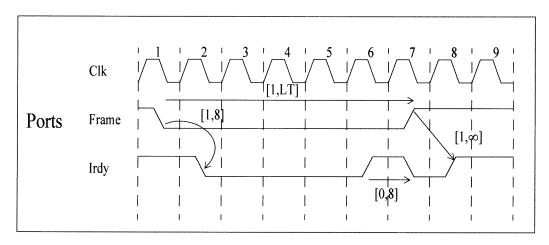

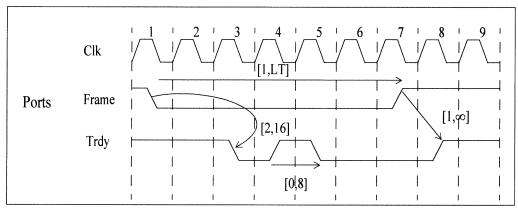

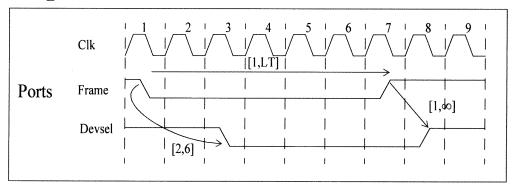

Un diagramme à actions feuille est tout d'abord un chronogramme traditionnel, représentant un comportement élémentaire d'un système numérique. Par exemple, la fonction de lecture ou d'écriture sur le bus PCI. Un diagramme feuille est constitué d'un ensemble de *ports* et d'événements qui se produisent sur ces ports. Ces événements sont liés entre eux par des contraintes temporelles. Pour mieux comprendre les caractéristiques d'un diagramme à actions feuille, considérons l'exemple de la figure 3, qui est un fragment de la spécification de la fonction de lecture sur le bus PCI, basée sur la description de la référence "PCI System Architecture" version 2.1. [57].

FIGURE 3. Diagramme à actions feuille représentant un fragment de la spécification de la fonction de lecture sur le PCI

La figure 3 montre que le diagramme feuille est défini par un ensemble de *ports*: *CLK*, *FRAME* et *IRDY*, qui ne sont autres que les liens de communication entre le système numérique et son environnement. Chaque port a un type. Celui-ci peut être tout type compatible avec le langage VHDL. Dans la référence [57], la spécification de la fonction de lecture ou d'écriture montre deux genres de types pour les ports: le type *booléen* encore appelé *std\_logic* en VHDL, comme le *FRAME*, *IRDY*, et le type *donnée*, *adresse ou bus* comme AD[31:0] ou AD[63:0] qui représentent respectivement un bus d'adresse de 32 ou 64 bits. Les ports ont aussi une direction: *entrée* (*in*), *sortie* (*out*) ou *bidirectionnelle* (*inout*), ou encore des ports internes invisibles de l'extérieur, que nous appelons *signaux*.

Sur chaque *port* du diagramme à actions feuille, nous avons des *actions* ou des *messages*. Les *actions* sont des changements d'état ou de valeur sur les ports en un instant donné (par exemple, dans la figure 3, le changement de valeur de 1 à 0 sur *IRDY* au deuxième cycle d'horloge). Les *messages* consistent en une mise à jour des valeurs des *ports*. Ces actions quant à elles gardent les propriétés des ports comme leur

direction sauf pour les *ports* d'entrée-sortie (inout) où chaque action doit être suivie de sa direction.

Dans la description des diagrammes à actions de type feuille, référons-nous à la figure

- 4. Chaque action possède l'une des étiquettes suivantes:

- 1. *constante*, qui dénote un symbole ou une valeur constante que le *port* doit atteindre et rester stable sur cette valeur jusqu'à ce qu'une nouvelle action se produise.

- 2. *valid*, qui indique que le port peut recevoir une valeur booléenne quelconque et gardera cette valeur jusqu'à ce qu'une prochaine action se produise.

- 3. Don't-care, qui signifie que le port a un comportement arbitraire ou non spécifié.

Tel que signalé précédemment, des actions peuvent être liées les unes aux autres par des relations temporelles. Une relation temporelle notée

$$C_{ij} = (a_i, a_j, [l_{ij}, u_{ij}])$$

indique que les temps d'occurrences  $t_i$  et  $t_j$  des actions  $a_i$  et  $a_j$  doivent satisfaire la relation suivante

$$l_{ij} \le t_j - t_i \le u_{ij}$$

Une contrainte est représentée par une flèche entre deux actions  $a_i$  et  $a_j$ , et étiquetée par un intervalle de temps. Dans la figure 3, l'exemple suivant

$$a_1 = \underbrace{[1,LT]} a_2$$

indique que l'action  $a_1$  si elle a lieu à un temps que l'on considère comme le temps  $t_1$ , alors l'action  $a_2$  aura lieu au plus tôt à la prochaine unité de temps ou au plus tard au temps d'occurrence LT > 0 (LT représente le temps maximal que doit durer une transaction de lecture ou d'écriture sur le bus PCI). On appelle  $a_1$  l'action source et  $a_2$  l'action puits.

Se référant à l'inégalité exprimée plus haut, si  $l_{ij} > 0$  alors la relation qu'elle exprime est une précédence, tant que l'action  $a_i$  a toujours lieu avant l'action  $a_j$  dans le temps (exemple de la figure 4). Si  $l_{ij} \le 0 \le u_{ij}$  alors la relation est une concurrence. Dans une relation de concurrence, les actions  $a_i$  et  $a_j$  peuvent avoir lieu dans un ordre quelconque. L'essentiel est que la séparation de temps entre les temps d'occurrences  $t_i$  et  $t_j$  soit d'au moins  $l_{ij}$  unités de temps ou d'au plus  $u_{ij}$  unité de temps.

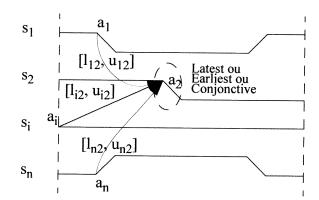

Lorsqu'une action *puits* dépend de plusieurs relations d'actions *sources* du même genre, celles-ci sont composées par les opérateurs *conjonctive*, *latest* ou *earliest*, et forment les contraintes temporelles. Voir Figure 4.

FIGURE 4. Diagramme à actions feuille avec des opérations

Soit  $\{(a_1, t_1), ..., (a_m, t_n)\}$ , l'ensemble des couples des événements et de leur temps d'occurrence, et soit  $C_j = \{c_{ij} | i \in I\}$ , l'ensemble de contraintes temporelles qui ont un événement puits  $a_j$ .

Un opérateur Conjonctive (linéaire) indique que les temps d'occurrences  $t_i$  et  $t_j$  doivent satisfaire la relation suivante

$$max(t_i + l_{ij}) \le t_j \le min(t_i + u_{ij})$$

avec  $i \in I$

Le temps d'occurrence est un élément de l'intervalle  $[t_i + l_{ij}, t_i + u_{ij}]$ , avec i appartenant à I; ceci signifie que toutes les relations de  $C_j$  doivent êtres satisfaites simultanément.

Un opérateur Latest (max), indique que les temps d'occurrence doivent satisfaire la relation suivante

$$max(t_i + l_{ij}) \le t_j \le max(t_i + u_{ij})$$

avec  $i \in I$

Ceci signifie que le temps d'occurrence  $t_j$  est déterminé par la dernière action source  $a_i$  qui s'est produite en fonction des bornes  $l_{ij}$  et  $u_{ij}$ . La relation entre les actions sources et l'action puits est dite causale. Ce qui implique que la relation temporelle  $C_{ij}$  est une relation de précédence où l'action  $a_j$  est le prédécesseur de toutes les actions  $a_i$  avec i appartenant à I.

Un opérateur Earliest (min) indique que les temps d'occurrence doivent satisfaire la relation suivante

$$min(t_i + l_{ij}) \le t_j \le min(t_i + u_{ij})$$

avec  $i \in I$

Ceci signifie que le temps d'occurrence  $t_j$  de  $a_j$  est déterminé par la première action source  $a_i$  qui s'est produite. La relation entre l'action source et l'action puits est aussi causale. Ce qui implique que la relation temporelle  $C_{ij}$  est une relation de précédence où l'action  $a_j$  est le prédécesseur de la première action  $a_i$  avec i appartenant à I.

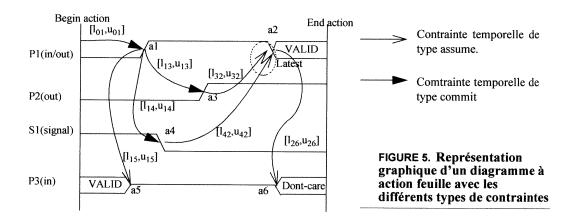

Les contraintes de temps peuvent être classées en deux genres: les contraintes assume et les contraintes commit. Les contraintes de temps assume indiquent des suppositions faites sur le temps d'occurrence des actions entrées (inputs).

Les contraintes du genre *commit* spécifient l'intervalle de temps d'occurence des actions *sorties* (*output*). L'instant d'occurence doit être à l'intérieur de l'intervalle temporel défini par la contrainte *commit* dont l'action est le *puits*. Les bornes temporelles des contraintes *commit* doivent avoir des valeurs finies.

Pour faciliter la composition hiérarchique, tout diagramme à actions feuille est délimité par deux actions virtuelles et implicites appelées *Begin* et *End*; Figure 5. L'action *begin* précède toute action du diagramme feuille alors que *end* succède à toutes les actions du diagramme feuille.

Satisfaire la spécification d'un diagramme à action feuille: La sémantique opérationnelle d'un diagramme à action est définie par son exécution dans l'environnement auquel sont rattachés les ports in et inout et l'observation des ports out et inout. Durant une exécution, un diagramme à actions est dit satisfait ou dans un état satisfaisant quand:

- 1. les spécifications des valeurs initiales sont satisfaites sur les ports in et inout,

- 2. les actions d'entrées respectent la séquence spécifiée, les contraintes de type assume et les valeurs spécifiées par les intervalles de temps d'occurrence.

Lorsqu'une erreur est détectée sur un port ou un signal durant l'exécution du diagramme à actions, celui-ci entre dans un état de non-satisfaction et son exécution est arrêtée. Une erreur d'exécution est produite si la spécification des valeurs initiales des ports n'est pas respectée, si les relations temporelles *assume/commit* ne sont pas satisfaites et si des actions inattendues se produisent sur un port.

Un diagramme est dit complètement satisfait si son exécution ne rencontre pas d'erreur, c'est-à-dire s'il reste constamment dans un état satisfaisant (autre que l'état d'erreur), de l'action *begin* jusqu'à l'action *end*.

La figure suivante est un schéma récapitulatif qui regroupe des caractéristiques d'un diagramme à actions feuille que nous avons évoqué plus tôt à savoir les actions *begin* et *end* ainsi que les étiquettes *Latest* ...

#### 2.2.2. Annotation des diagrammes feuilles [59]

Un diagramme à actions feuille peut être annoté par des paramètres (entrées, sorties, entrées-sorties), des variables locales, des constantes génériques, des prédicats (fonctions booléennes) et des procédures compatibles aux types du langage VHDL.

Les paramètres et les variables locales peuvent être attachés aux événements d'un diagramme feuille. Les étiquettes d'une action ou d'une valeur initiale peuvent en général être des symboles arbitraires. Pour des étiquettes comme VALID, la sémantique est la même. L'étiquette symbolique a l'effet d'une déclaration automatique de variable qui est correspondante au type de la donnée de l'action du diagramme. Dans le cas de la spécification d'un événement en *entrée*, la valeur actuelle du port est attachée à la variable associée. Pour les événements en *sortie*, la valeur de l'action est assignée à la variable une fois que l'action est produite (dans ce cas, l'attachement d'une variable à la spécification de l'événement est obligatoire).

Les prédicats et les procédures ayant comme paramètres d'entrée des variables et/ou les paramètres des diagrammes feuilles peuvent être attachés à n'importe quelle action. Lorsque les événements se produisent, les procédures et les prédicats qui leur sont attachés sont exécutés dans un temps considéré comme *nul*. Ces prédicats ou procédures ne doivent pas contenir des références au temps, au délai ou à la synchronisation (par exemple: *WAIT* en VHDL). Les procédures décrivent la fonction d'un diagramme à actions. Si le prédicat attaché à un événement spécifique retourne *faux* après son évaluation, le diagramme à actions est *désactivé* et entre dans un état de *non satisfaction*.

À chaque événement donné sont attachés au plus une procédure et un prédicat. La sémantique de l'exécution au temps où un événement a lieu (ou plusieurs événements ont lieu au même moment) sont:

- 1. Mettre à jour toutes les variables associées aux événements d'entrées qui sont exécutés à l'instant même où les événements se produisent.

- 2. Évaluer tous les prédicats qui sont attachés aux événements dans (1) et aux événements de sortie qui sont supposés être exécutés dans l'instant courant.

- Exécuter dans un ordre arbitraire toutes les procédures attachées aux événements de (2).

- 4. Mettre à jour les ports correspondants aux événements de sortie qui sont exécutés dans l'instant courant.

#### 2.2.3. Diagrammes à actions hiérarchiques

Les diagrammes à actions peuvent être composés hiérarchiquement. Un diagramme à action hiérarchique Q est défini par un ensemble de ports *externes*, une liste de diagrammes à actions fils  $(A_1,...,A_n)$ , un opérateur de composition hiérarchique et un port de lien pour chaque  $A_i$  avec  $i \in [1,...,n]$ . Le lien des ports établit la correspondance entre les ports externes des  $A_i$  et les ports *internes* ou *externes* de Q.

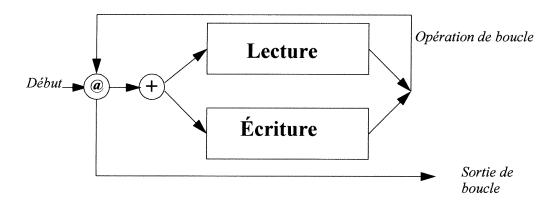

Les opérations de composition hiérarchique sont: *la concaténation*, *la boucle*, *la concurrence*, *le choix* et *l'exception*.

Soit Q un diagramme hiérarchique et  $L = (A_1, ..., A_n)$  une liste de diagrammes à actions,  $Q \neq A_i$ .

La Concaténation (Concatenation) lie l'exécution de la liste des  $A_i$  dans leur ordre d'apparition.  $A_I$  commence quand Q commence;  $A_{i+1}$  commence quand  $A_i$  finit; Q finit quand  $A_n$  finit.

La Boucle (Loop) répète l'exécution d'un  $A_i$  en un nombre fini ou infini de fois. La boucle est une concaténation particulière qui lie un diagramme à actions à lui même.

La Concurrence (Parallel) exécute les  $A_i$  en parallèle.  $A_1$ , ...,  $A_n$  commencent quand Q commence et Q finit son exécution quand tous les  $A_i$  ont fini.

Le Choix (Delayed Choice) fait une sélection entre les diagrammes à actions fils de la liste L. Ce choix est basé sur l'évaluation des prédicats et/ou les violations des hypothèses sur l'exécution des événements.  $A_1,...,A_n$  représentent des comportements alternatives (branches) de la composition.  $A_1,...,A_n$  commencent lorsque Q commence. Q finit lorsqu'un seul  $A_i$  finit. Si tous les  $A_i$  rentrent dans un état de non satisfaction, alors Q rentre dans un état de non satisfaction. Lorsque l'exécution Q commence, des prédicats attachés à tous les  $A_i$  de l'opération sont appelés et évalués, et l'opération décide du  $A_i$  qui continuera l'exécution selon le critère de choix. Si plusieurs  $A_i$  de la liste L sont évalués et acceptés pour continuer l'exécution, alors le choix est retardé et les branches qui passent dans un état de non satisfaction sont abandonnées au fur et à mesure que l'exécution progresse. Signalons que toutes les branches qui sont évaluées et acceptées ont le même comportement jusqu'à ce qu'une branche  $A_i$  se démarque des autres. Si une branche  $A_i$  termine son exécution alors que plusieurs autres b ranches

sont en cours d'exécution alors  $A_i$  est un *préfixe* des branches en cours d'exécution, ce qui est une erreur. Q passe alors dans un état de *non satisfaction*.

L'*Exception* contient trois diagrammes à action fils:  $A_N$  décrit le comportement normal,  $A_C$  le comportement de la condition d'exception et  $A_H$  le comportement de l'exception.  $A_N$  et  $A_C$  commencent lorsque Q commence. Si  $A_C$  termine son exécution avant le comportement normal  $A_N$ , l'exécution de  $A_N$  est arrêtée et l'exécution de  $A_H$  commence. Si  $A_H$  termine son exécution, alors Q aussi termine son exécution. Si  $A_N$  termine complètement son exécution avant  $A_C$ , alors  $A_C$  est arrêté et Q termine.

#### 2.2.4. Annotation des diagrammes hiérarchiques

Comme les diagrammes à actions feuilles, les diagrammes hiérarchiques peuvent avoir des paramètres (entrée, sortie, entrée/sortie), des variables locales compatibles à tout type VHDL et des constantes génériques. Pour les diagrammes de type choix, un prédicat peut être attaché à chaque branche du diagramme. Les arguments des prédicats peuvent être n'importe quelle variable et constante du diagramme. Les prédicats sont évalués à chaque exécution au début de l'exécution du diagramme choix. Seules les branches dont les prédicats ont été évalués vrai sont activées. De façon semblable, un prédicat peut être attaché à un diagramme Boucle. Il est évalué au début de chaque exécution du diagramme à actions fils de la boucle. Si la valeur du prédicat est fausse, alors l'exécution de la boucle est complétée. En cas contraire le diagramme boucle est arrêté. Le prédicat de la boucle peut être une variable ou une constante quelconque. Par ailleurs, des procédures ou des prédicats peuvent être attachés à la spécification des événements virtuels Begin/End des diagrammes à actions d'un diagramme hiérarchique Q. Ces procédures ou prédicats peuvent prendre leurs valeurs dans un sous-ensemble de l'ensemble des variables et des constantes du diagramme Q.

#### 2.2.5. Description d'un diagramme à actions feuille en langage HAAD

La figure 6 représente un exemple de la spécification d'un diagramme feuille de la figure 5 en langage HAAD. Le langage HAAD est un langage basé sur la structure syntaxique du langage LISP. Toutes les clauses sont constituées d'un emboîtement de paires (Mot\_clé, Liste\_des\_valeurs). Pour une description complète de la grammaire du langage de HAAD, nous vous prions de vous rapporter à l'Appendice A de la référence [59].

Un modèle HAAD, même s'il contient un seul diagramme à actions, débute avec le mot clé *DefBehavior* suivi du nom que l'utilisateur donne au modèle. Il est suivi par une liste de ports. À chaque port est associé un nom, un mode (in, out, inout), un type conformément à la syntaxe de VHDL, et les interprétations des actions sur les ports comme *EVENT* pour les événements ou *MESSAGE* pour les messages. Une spécification HAAD peut être remplacée par un paramètre en utilisant les mots clés appropriés. Toute déclaration de paramètre est constituée par son nom, son mode, son type et ce, de façon analogue à la déclaration des ports. Les paramètres sont passés par référence et leur impact se limite au HAAD dans lequel ils sont déclarés. La déclaration des paramètres est suivie par la déclaration des signaux internes *(mot clé SIGNAL)*, des variables locales *(mot clé VARIABLE)* et des constantes *(mot clé CONSTANT)*.

Ce bref aperçu de la syntaxe du langage HAAD est tout aussi valable pour les diagrammes à actions feuille que les diagrammes de composition hiérarchique. Les diagrammes à actions feuille sont déclarés par le mot clé *LEAF* qui permet d'ouvrir une nouvelle région déclarative. Chaque port est spécifié comme une succession d'une ou de plusieurs actions. Le *mode* (in, out, et inout) des actions au niveau des feuilles leur est légué par la direction des ports. Dans le cas d'un port à direction *inout*, le mode de chaque action de ce port doit être spécifié à chaque fois que l'action est déclarée. La séquence des actions de chaque port est définie par le mot clé *CARRIER\_SPEC*, suivie par la spécification de la valeur initiale de chaque port et par la liste de la spécification des actions. Chaque action est identifiée par le mot clé *ACTION SPEC*. Une action est

spécifiée par son nom suivi de son étiquette qui peut être une constante ou un symbole dénotant une constante, un symbole spécifique *VALID* ou *DONT CARE*.

```

(DEFBEHAVIOR EXAMPLE HAAD FIGURES

(PORTS

(PORT P1 INOUT "std logic" EVENT)

(PORT P2 OUT "std logic" EVENT)

(PORT P3 IN "std logic" EVENT))

(SIGNAL S1 "std logic" EVENT "1")

(LEAF

(CARRIER-SPEC P1 (INITIAL-SPEC (CONSTANT "0"))

(ACTION-SPEC 'a1 (CONSTANT "1") (DIRECTION OUT))

(ACTION-SPEC 'a2 (VALID) (DIRECTION IN))

(CARRIER-SPEC P2 (INITIAL-SPEC (CONSTANT "0"))

(ACTION-SPEC 'a3 (CONSTANT "1"))

(CARRIER-SPEC S1 (INITIAL-SPEC (CONSTANT "1"))

(ACTION-SPEC 'a4 (CONSTANT "0"))

(CARRIER-SPEC P3 (INITIAL-SPEC (VALID))

(ACTION-SPEC 'a5 (CONSTANT "Z"))

(ACTION-SPEC 'a6 (DONT-CARE)))

(PRECEDENCE 'start-action 'a1 (INTENT COMMIT) (CMIN l<sub>01</sub>) (CMAX u<sub>01</sub>))

(PRECEDENCE 'a1 'a3 (INTENT COMMIT) (CMIN l<sub>13</sub>) (CMAX u<sub>13</sub>))

(PRECEDENCE 'a1 'a4 (INTENT COMMIT) (CMIN I<sub>14</sub>) (CMAX u<sub>14</sub>))

(LATEST

(PRECEDENCE 'a3 'a2 (INTENT ASSUME) (CMIN l<sub>32</sub>) (CMAX u<sub>32</sub>))

(PRECEDENCE 'a4 'a2 (INTENT ASSUME) (CMIN l<sub>42</sub>) (CMAX u<sub>42</sub>)))

(PRECEDENCE 'a1 'a5 (INTENT ASSUME) (CMIN l<sub>15</sub>) (CMAX u<sub>15</sub>))

(PRECEDENCE 'a2 'a6 (INTENT ASSUME) (CMIN I<sub>26</sub>) (CMAX u<sub>26</sub>))))

FIGURE 6. Spécification en langage HAAD du diagramme à actions feuille de la figure 5

```

#### 2.2.6. Diagrammes synchrones

Les diagrammes synchrones ont les mêmes caractéristiques que les diagrammes feuilles à la seule différence qu'une horloge leur est ajoutée, et tout comportement temporel est spécifié en terme de cycles de cette horloge. L'exécution des séquences des actions sur un port est synchronisée par l'horloge.

Deux types de temps sont distingués dans les horloges: le temps discret ou par intervalles et le temps continu ou  $r\acute{e}el$ . Mathématiquement, le temps tel que nous le vivons quotidiennement nous apparaît continu parce qu'il se déroule de façon ininterrompue. On ne passe pas tout à coup d'une minute à l'autre, en laissant un trou. Le temps, en effet, parcourt tous les points qui séparent un instant t et un instant suivant t+1 augmenté d'une minute. Contrairement au temps continu ou réel, un temps est discret si le temps n'est considéré qu'à certains points discrets du déroulement du temps. Ces points ou instants sont des intervalles de temps bien définis et de longeurs égales, et résultent d'un découpage à part égale du déroulement du temps continu. Chaque intervalle est considéré comme une unité de temps appelée dans notre cas cycle d'horloge.

Dans le cas d'un diagramme à actions synchrone, le temps discret veut dire que les événements sont produits et pris en compte seulement à des instants précis qui sont les fronts actifs d'une horloge (montant ou descendant). Les procédures et prédicats sont évalués entre les fronts actifs de deux cycles d'horloge et les sorties sont produites à chaque front actif du cycle du temps indiqué par la spécification. Dans le cas de notre étude, le temps est discrètement continu et chaque graduation est un entier naturel; une unité étant égale à un cycle d'horloge.

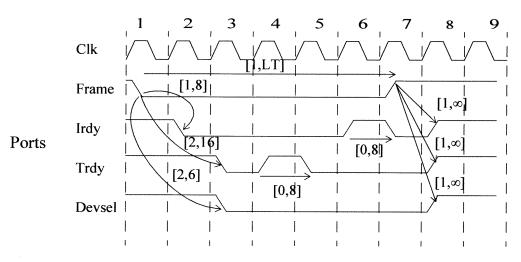

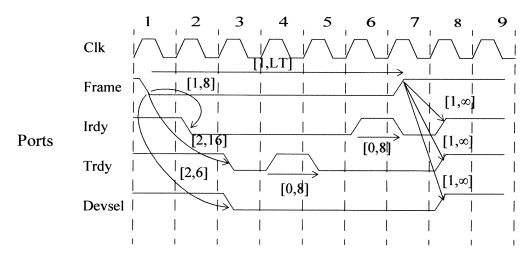

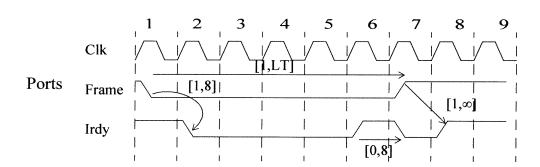

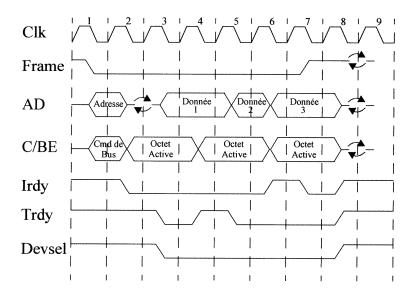

La figure 7, prise ici comme exemple de diagramme synchrone, représente les caractéristiques des signaux de contrôle d'une transaction de lecture du bus PCI. Cette figure permet non pas de montrer la sémantique de la transaction de lecture du bus PCI, mais de montrer les spécifications d'un diagramme synchrone. Sur cette figure, l'horloge *clk* est active au front montant. Chaque cycle est délimité par les lignes verti-

cales en pointillés et numéroté par des entiers naturels. La première action du signal *Frame* a lieu au 1<sup>er</sup> cycle d'horloge et sa dernière au 7<sup>ème</sup> cycle.

LT est le temps de latence d'une Transaction de Lecture sur le PCI

FIGURE 7. Exemple de diagramme synchrone: Transaction réduite de lecture sur le bus PCI.

#### 2.3. Conclusion

La conception d'un système numérique dépend du niveau de clarté de sa spécification. Plusieurs équipes se sont penchées sur le problème de la spécification formelle pour réduire les ambiguïtés et les interprétations subjectives dans les protocoles. La plupart des approches trouvées par ces équipes, aussi efficaces soient elles, ne sont capables de traiter que des aspects particuliers de la spécification. La méthode HAAD proposée dans la référence [59] est la plus complète. Elle prend en compte les aspects fonctionnels du système et traite des protocoles de système quel que soit le degré de leur complexité, par une description de chronogrammes rigoureuse, basée sur une structure hiérarchique assez complète.

Le chapitre suivant présente la méthode de la construction de la machine à états observatrice. Il introduit premièrement la description des machines à états et montre comment ces machines sont utilisées pour construire une machine à état observatrice. Il parle également de la décomposition des diagrammes à actions feuilles en diagrammes plus simples et de l'introduction de signaux spécifiques qui sont utilisés pour coordonner les activités de ces diagrammes.

**CHAPITRE 3**

# Construction des machines observatrices à partir des spécifications HAAD

The understanding of the theory of a routine may be greatly aided by providing, at the time of construction one or two statements concerning the state of the machine at well chosen points... In the extreme form of the theoretical method a watertight mathematical proof is provided for the assertions. In the extreme form of the experimental method the routine is tried out on the machine with a variety of the initial conditions and is pronounced fit if the assertions hold in each case.

Both methods have their weaknesses.

Alan Mathison Turing, Ferranti Mark | Programming Manual (1950)

#### 3.1. Introduction

Dans ce chapitre, nous allons considérer que la spécification littérale des protocoles de bus est tansformée en spécification HAAD.

La structure générale d'une machine observatrice après sa réalisation peut être vue comme un réseau de machines à états liées les unes aux autres par des modules de composition hiérarchiques. Pour la construire, nous avons utilisé une approche simple qui peut être regroupée en trois points :

- 1. Décomposer les diagrammes feuilles de la spécification du protocole de bus en diagrammes plus simples et les lier par des opérations de composition hiérarchique, de telle sorte que la spécification du protocole du bus soit respectée par la composition des diagrammes feuilles qui résultent de la décomposition.

- 2. Définir pour chaque diagramme feuille qui résulte de la décomposition une machine à états finis.

3. Connecter ces machines à états par des modules logiques qui réalisent les règles de la composition hiérarchique définies lors de la décomposition.

Cette technique en trois points permet de décrire de façon plus concise la machine à états observatrice et d'éviter le problème d'explosion de la description si tous les diagrammes feuilles sont décrits par une seule machine à états.

Dans ce chapitre, nous allons présenter la décomposition des diagrammes feuilles, la transformation des diagrammes résultant de la décomposition en machine à états finis synchrone et temporisée (STFSM) et l'interconnexion de ces machines pour produire la machine observatrice.

# 3.2. Décomposition des diagrammes feuilles.

Lors de notre étude, nous avons remarqué qu'il est très difficile de transformer un diagramme feuille représentant une fonction d'un système (par exemple, la lecture du bus PCI) en machine STFSM sans se confronter au problème d'explosion de la description. La complexité d'une machine numérique croît alors de façon exponentielle par rapport à la complexité du diagramme feuille. En effet, la machine observatrice doit prendre en considération toutes les combinaisons des entrées dans chaque état. Pour remédier à ce problème, nous proposons de décomposer les diagrammes feuilles en diagrammes de même nature, mais moins complexes. Cette décomposition est basée sur des relations entre les diagrammes feuilles et les diagrammes hiérarchiques, et sur des techniques de décomposition de circuits numériques [5], [7], [4], [2], [6].

Dans la suite de cette section, nous présentons l'approche de base que nous avons utilisée dans la décomposition d'un diagramme feuille en plusieurs sous diagrammes moins complexes. Nous avons basé notre étude sur des cas généraux et avons montré quelques exemples sur un fragment de la spécification de la fonction de lecture sur le

bus PCI. Nous avons utilisé deux méthodes de décomposition: la décomposition parallèle et la décomposition en cascade. De plus, nous avons défini des règles de façon ad hoc pour faciliter la décomposition.

#### 3.2.1. La Décomposition en Parallèle d'un Diagramme Feuille

La décomposition parallèle permet un découpage d'un diagramme feuille f en sous diagrammes dont les exécutions se font dans le même intervalle de temps. Dans le cas de notre étude, nous avons basé cette décomposition parallèle sur le lien que les ports ont les uns avec les autres. Si une action  $a_p$  sur un port p est liée par une flèche à une autre action  $a_q$  sur un port q, alors les ports p et q sont isolés et vont constituer un sous diagramme de f. Si nous prenons l'exemple du diagramme de la fonction de lecture sur le bus PCI représenté par la figure 7 au chapitre 2, nous pouvons faire une décomposition parallèle si nous regroupons les signaux selon leur dépendance et obtenir l'exemple de la figure 3 au chapitre 2 comme sous diagramme.

LT est le temps de latence d'une Transaction de Lecture sur le PCI

FIGURE 8. Transaction réduite de lecture sur le bus PCI représentant un diagramme feuille f

La décomposition parallèle d'un diagramme feuille suit les règles suivantes:

Règle1: Regrouper deux à deux des paires d'actions sur des ports différents liés par une ou plusieurs contraintes pour en faire des diagrammes feuilles.

La règle 1 peut être illustrée par la figure 9. Si nous regardons bien la figure 8 à partir de laquelle nous avons obtenu la figure 9, nous remarquons que les ports *FRAME* et *IRDY* ont deux paires d'actions qui sont liées. Nous pouvons ainsi isoler les comportements des deux ports et en faire un diagramme feuille.

Règle2: Créer des diagrammes feuilles pour tous les ports du diagramme f qui ne sont pas couverts par la règle 1.

La règle 2 permet de créer des diagrammes feuilles pour des ports dont les actions ne sont pas liées avec d'autres actions de ports différents. Dans le cas de la figure 8, nous n'avons pas de port qui n'est pas lié à un autre par une contrainte.

FIGURE 9. Exemple de diagramme feuille résultant de l'application de la règle 1 de la décomposition parallèle sur le diagramme f

#### 3.2.2. La Décomposition en cascade d'un diagramme feuille

La décomposition en cascade se fait par rapport au temps chronologique du diagramme feuille. Ce découpage du diagramme principal doit tenir compte de la progression temporelle de celui-ci. Un diagramme feuille obtenu de la décomposition en cascade doit traiter au moins d'une contrainte entre une paire d'actions de deux ports différents ou une paire d'actions d'un même port.

Dans le cas où il y a eu au préalable une décomposition parallèle du diagramme feuille principal, il est plus judicieux d'utiliser ces sous diagrammes pour les décomposer en cascade afin d'obtenir des sous diagrammes encore plus simples. Prenons par exemple la figure 9 précédente qui est le résultat d'une décomposition parallèle. En la décomposant en cascade, on obtient les boîtes de la figure 10. Chaque boîte représente un diagramme feuille plus petit qui peut être représenté plus facilement par une machine à états.

diagramme feuille représenté par la figure 9

Nous présenterons plus tard comment les diagrammes feuilles représentés par les boîtes de la figure 10 sont liés par des opérateurs de composition pour que la figure 10 soit fonctionnellement équivalente à la figure 9. La décomposition en cascade d'un diagramme suit la règle suivante:

Règle3: Décomposer les diagrammes feuilles (résultant d'une décomposition parallèle préalable si possible) en diagrammes feuilles plus petits et décrits comme suit:

- i). Créer un diagramme feuille pour une paire d'actions liée par une contrainte sur le même port ou sur des ports différents. (Exemple de la figure 11).

- ii). Créer un diagramme feuille pour chaque combinaison logique des ports deux à deux regroupés par la règle 1. Exemple de la boîte "active" dans la figure 10.

FIGURE 11. Exemple de diagramme feuille résultant de l'application de la règle 3. i) de la décomposition cascade sur le diagramme feuille de la figure 9

Une fois la décomposition faite, une machine STFSM est construite pour chaque fragment de diagramme feuille.

Un problème simple, mais important, de la décomposition est de pouvoir recomposer les machines afin de retrouver le comportement original. À cet effet, nous allons parler de la composition parallèle et de la composition en cascade, et montrer que le choix et

la boucle sont des opérations de composition qui sont déduites des deux précédentes. Nous allons nous baser sur les opérateurs de la méthode HAAD [59].