Université de Montréal

# Integrating MDG Variable Ordering in a VHDL-MDG Design Verification System

par Yi Feng

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

Thèse présentée à la Faculté des études supérieures en vue de l'obtention du grade de Philosophiæ Doctor (Ph.D.) en Informatique novembre, 2001

<sup>©</sup> Yi Feng, 2001

QA 76 US4 2002 V. 011

Université de Montréal Faculté des études supérieures

Cette thèse intitulée

# Integrating MDG Variable Ordering in a VHDL-MDG **Design Verification System**

présentée par

Yi Feng

a été évaluée par un jury composé des personnes suivantes:

Professor Marc Feeley président-rapporteur

Professor Eduard Cerny directuer de recherche

Professor Hanifa Boucheneb membre du jury

Professor Xiaoyu Song examinateur externe

Han Pauchen représentant du doyen de la FES

## Résumé

Les méthodes de vérification formelle consistent en l'utilisation des techniques analytiques pour prouver que l'implantation d'un système se conforme bien à la spécification. Comme une représentation efficace de Machines à États Finis Étendues, les *Multiway Decision Graphs* (MDG) sont appropriés pour la vérification formelle automatique du matériel pour la conception au niveau transfert de registres (*Register Transfer Level*).

Pour réduire l'effet du problème d'explosion d'états dans un système basé sur un MDG, nous présentons des algorithmes statiques et dynamiques de l'ordonnancement automatique des variables. L'ordonnancement des variables sur MDG est plus compliqué que celui sur ROBDDs à cause de la présence des termes du premier ordre dans MDG.

L'algorithme de l'ordonnancement des variables statiques génère un ordre des variables avant qu'un MDGs soit construit et le choix de l'ordre dépend de l'information sur la topologie du circuit en considération. L'algorithme de reordonnancement dynamique minimise la taille des MDGs au cours du processus de vérification et permet de terminer en succès une tâche de vérification qui peut échouer avec un ordre fixe. Nous discutons aussi du problème de l'ordonnancement des termes standards causé par l'ordre lexicographique que les MDGs utilisent pour ordonnancer certains termes. Une solution est présentée qui est basée sur le re-étiquetage des fonctions et la reécriture des termes.

Le MDG devient plus efficace avec le développement de l'ordonnancement automatique de variables. Mais, un système MDG n'accepte que le langage MDG-HDL. Nous avons alors développé un traducteur qui accepte un modèle décrit en VHDL, au niveau RTL synthétisable, et qui produit la représentation requise pour le système MDG.

Nous avons intégré les algorithmes de traduction et ceux de (re)ordonnancement dans le système de vérification de conception basé sur MDG. L'ordonnancement efficace des variables est essentielle pour le bon fonctionnement du système et la traduction automatique du VHDL au MDG-HDL rend possible la vérification des conceptions industrielles décrites en VHDL. Les résultats expérimentaux ont démontré que ce système amélioré est capable de traiter une classe de modèles plus large que celui sans l'introduction de ces améliorations. Donc notre système étend la classe des circuits vérifiables.

Mot clés :

- vérification formelle

- Graphes de Décision Multidirectionnels

- intégration de logiciels

- ordonnancement des variables

- traduction automatique de VHDL

- vérification de propriétés

## Abstract

Formal verification methods involve the use of analytical techniques to prove that the implementation of a system conforms to the specification. As an efficient representation of Extended Finite State Machines, Multiway Decision Graphs (MDG) are suitable for automatic hardware formal verification of Register Transfer Level (RTL) designs.

To reduce the effects of the state explosion problem in the MDG-based system, we explore automatic static and dynamic variable ordering algorithms. Compared with ROBDDs, the situation is complicated by the presence of first order terms in MDGs.

The static variable ordering algorithm generates a variable order before an MDG is built and the order is chosen using information about the circuit topology. The dynamic reordering algorithm minimizes the size of the MDG during the verification process and allows a verification task to finish when the task may not complete with a fixed order due to insufficient memory or execution time. We also identify a standard term ordering problem caused by the standard term order used in MDG to order some specific terms. A solution based on function renaming and term rewriting is presented.

The MDG system has become more efficient with the development of automatic variable ordering. However, the system only accepts MDG-HDL and most of designs in industry are described in VHDL or Verilog. We present a translator which can accept a VHDL model given at the synthesizable RTL level and produce the required representation by the MDG system.

We integrated the translation and the (re)ordering algorithms into the MDG design verification system. Efficient variable ordering is essential for good functioning of the verification system and automatic translation from VHDL to MDG-HDL makes possible the verification of industrial designs. Experimental results proved that this updated system can handle a larger class of designs than before, thus alleviating the effects of the state exploration problem and increasing the range of the circuits that can be verified.

Key words:

- formal verification

- Multiway Decision Graphs

- software integration

- variable ordering

- automatic translation of VHDL

- property checking

# **Table of Contents**

| 2.3 Reduced Ordered Binary Decision Graphs                           | .22 |

|----------------------------------------------------------------------|-----|

| 2.3.1 Binary Decision Diagrams                                       | .22 |

| 2.3.2 Variable Ordering on ROBDD                                     | .23 |

| 2.3.3 Static Variable Ordering                                       | .25 |

| 2.3.4 Dynamic Variable Ordering                                      | .26 |

| Chapter 3 Multiway Decision Graphs                                   | .28 |

| 3.1 Formal Logic                                                     | .29 |

| 3.1.1 Syntax                                                         | .29 |

| 3.1.2 Semantics                                                      | .30 |

| 3.1.3 Directed Formulas                                              | .32 |

| 3.2 Multiway Decision Graphs                                         | .33 |

| 3.2.1 Structure                                                      | .33 |

| 3.2.2 Basic Algorithms                                               | .36 |

| 3.3 Abstract State Machines                                          | .38 |

| 3.3.1 Representing Sets using MDGs                                   | .38 |

| 3.3.2 Describing State Machines with MDGs                            | .38 |

| 3.3.3 State Exploration                                              | .40 |

| 3.4 MDG-based Verification Applications                              | .42 |

| Chapter 4 Static Variable Ordering on MDG                            | .45 |

| 4.1 Constraints on Variable Ordering on MDG                          | .45 |

| 4.2 Heuristic Rules for Variable Ordering                            | .47 |

| 4.3 A Static Variable Ordering Algorithm for MDG                     | .53 |

| 4.3.1 Static Variable Ordering Algorithms for Combinational Circuits | .54 |

| 4.3.2 Static Variable Ordering Algorithms for Sequential Circuits    | .60 |

| 4.4 Proof of Convergence of the Algorithms                           | .61 |

| 4.5 Experimental Results                                             | .64 |

| 4.5.1 Experiments on the IFIP Benchmark Circuits                     | .65 |

| 4.5.2 Invariant Checking on the Island Tunnel Controller             | .66 |

| 4.5.3 Property Checking on the Fairisle ATM Switch Fabric            | .67 |

-

| Chapter               | 5 Dynamic Variable Ordering on MDG                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71                                                              |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 5.1                   | Variable Swapping in Multiway Decision Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                                              |

|                       | 5.1.1 Implementation of a Variable Swapping Operation                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                                                              |

|                       | 5.1.2 The Effects of the Swapping Operation on Variable Order                                                                                                                                                                                                                                                                                                                                                                                                                      | 76                                                              |

|                       | 5.1.3 Constraints on a Variable Swap                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77                                                              |

| 5.2                   | A Basic Sifting Algorithm on MDG                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78                                                              |

| 5.3                   | Sifting-based Variable Reordering Algorithm on MDG                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80                                                              |

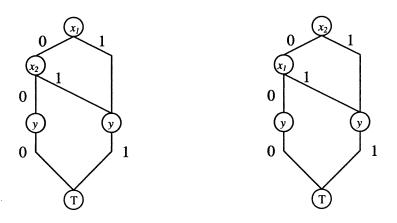

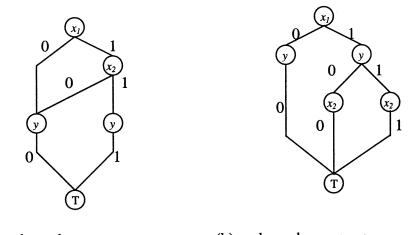

|                       | 5.3.1 Symmetry Sifting                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81                                                              |

|                       | 5.3.2 Group Sifting                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84                                                              |

| 5.4                   | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86                                                              |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |

| Chapter               | 6 Standard Term Ordering Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90                                                              |

| 6.1                   | Introduction to the Standard Term Ordering Problem                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90                                                              |

|                       | 6.1.1 Internal Representation of Terms and TermID Assignment                                                                                                                                                                                                                                                                                                                                                                                                                       | 91                                                              |

|                       | 6.1.2 Identification of the Standard Term Ordering Problem                                                                                                                                                                                                                                                                                                                                                                                                                         | 92                                                              |

|                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |

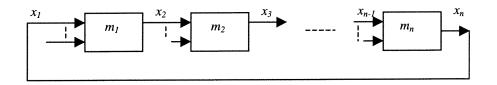

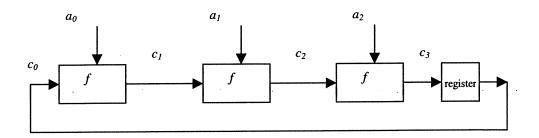

|                       | 6.1.3 A Chain Circuit Structure with the Standard Term Ordering                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95                                                              |

| 6.2                   | 6.1.3 A Chain Circuit Structure with the Standard Term Ordering                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |

| 6.2                   | 6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br>Problem                                                                                                                                                                                                                                                                                                                                                                                                         | 96                                                              |

| 6.2                   | <ul><li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li><li>A Solution to the Standard Term Ordering Problem</li></ul>                                                                                                                                                                                                                                                                                                                             | 96<br>97                                                        |

|                       | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem</li> <li>6.2.1 Function Renaming</li> </ul>                                                                                                                                                                                                                                                                                         | 96<br>97<br>98                                                  |

| 6.3                   | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem</li> <li>6.2.1 Function Renaming</li> <li>6.2.2 An Unconditional Cross-term Rewriting System</li> <li>A Case Study</li> </ul>                                                                                                                                                                                                       | 96<br>97<br>98<br>102                                           |

| 6.3<br>Chapter        | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem</li></ul>                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>98<br>102<br>105                                    |

| 6.3<br>Chapter        | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem</li> <li>6.2.1 Function Renaming</li> <li>6.2.2 An Unconditional Cross-term Rewriting System</li> <li>A Case Study</li> </ul>                                                                                                                                                                                                       | 96<br>97<br>98<br>102<br>105                                    |

| 6.3<br>Chapter<br>7.1 | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem</li></ul>                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>98<br>102<br>105<br>105                             |

| 6.3<br>Chapter<br>7.1 | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     | 96<br>97<br>98<br>102<br>105<br>105<br>107                      |

| 6.3<br>Chapter<br>7.1 | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     | 96<br>97<br>98<br>102<br>105<br>105<br>107<br>109               |

| 6.3<br>Chapter<br>7.1 | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem.</li> <li>6.2.1 Function Renaming.</li> <li>6.2.2 An Unconditional Cross-term Rewriting System.</li> <li>A Case Study</li> <li>7 Translation from VHDL to MDG-HDL.</li> <li>7 Transformation from VHDL to a DAG.</li> <li>7.1.1 Generation of CDFG.</li> <li>7.1.2 Loop Unrolling and Expansion of Procedures/Functions.</li> </ul> | 96<br>97<br>98<br>102<br>105<br>105<br>107<br>109<br>109        |

| 6.3<br>Chapter<br>7.1 | <ul> <li>6.1.3 A Chain Circuit Structure with the Standard Term Ordering<br/>Problem</li> <li>A Solution to the Standard Term Ordering Problem</li></ul>                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>98<br>102<br>105<br>105<br>107<br>109<br>109<br>109 |

-

| 7.2 Translation from a DAG to a MDG-HDL Model           | 112 |

|---------------------------------------------------------|-----|

| 7.3 Examples of Translation from VHDL to MDG-HDL        | 115 |

| 7.3.1 Island Tunnel Control Counter                     | 115 |

| 7.3.2 A Moore Finite State Machine                      | 117 |

| Chapter 8 Conclusions and Future Work                   | 121 |

| 8.1 Conclusions                                         | 121 |

| 8.2 Future Work                                         | 123 |

| Bibliography                                            | 127 |

| Appendix A. Verification of an Island Tunnel Controller | 138 |

| A.1 The Island Tunnel Controller                        | 138 |

| A.2 Verification                                        | 141 |

| Appendix B Verification of an ATM Switch Fabric         | 143 |

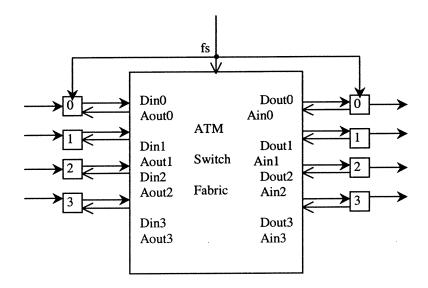

| B.1 The Fairisle ATM Switch Fabric                      | 143 |

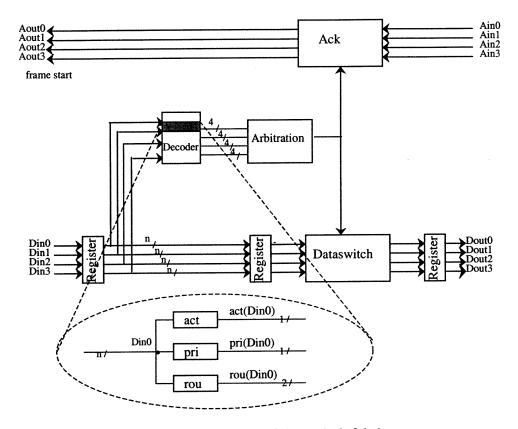

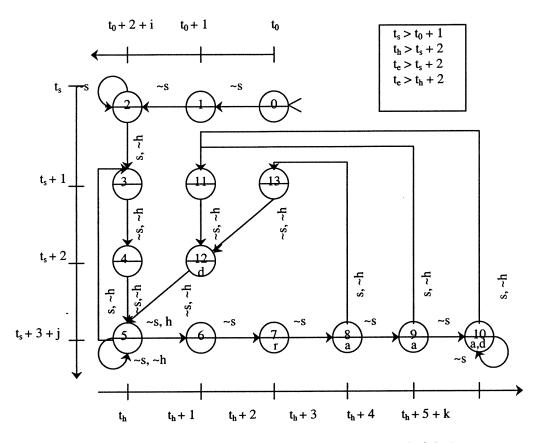

| B.2 Hardware Description                                | 145 |

| B.2.1 Gate and RT Implementation                        | 145 |

| B.2.2 Behavioral Specification                          | 146 |

| B.3 Property Checking of ATM model                      | 148 |

| а́                                                      |     |

viii

# List of Tables

| Table 4.1 | An example of a circuit component in tabular form          | 59   |

|-----------|------------------------------------------------------------|------|

| Table 4.2 | Experimental results for IFIP benchmark circuits           | 65   |

| Table 4.3 | Experimental results for invariant checking on ITC         | 67   |

| Table 4.4 | Experimental results of property checking on the ATM model | 69   |

|           |                                                            |      |

| Table 5.1 | Experimental results for IFIP benchmark circuits           | 87   |

| Table 5.2 | Experimental results of property checking on the ATM model | 87   |

| Table 5.3 | Experimental results for invariant checking on ITC         | 88   |

|           | -                                                          |      |

| Table 6.1 | Experimental results for an ATM congestion controller      | .103 |

# **List of Figures**

| Figure 2.1 | A model checking system13                                          |

|------------|--------------------------------------------------------------------|

| Figure 2.2 | ROBDDs for the same function under two different variable orders24 |

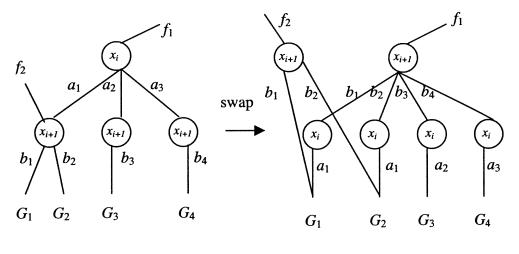

| Figure 2.3 | Variable swapping: node distribution before and after swapping27   |

| Figure 4.1 An example of MDG                                                 | 46 |

|------------------------------------------------------------------------------|----|

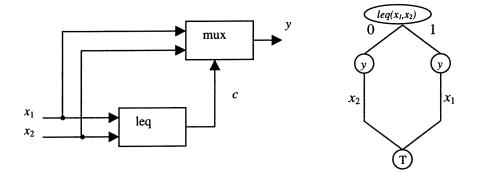

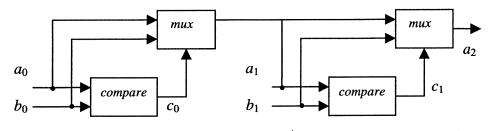

| Figure 4.2 An MDG representation of the circuit that selects a smaller value | 47 |

| Figure 4.3 MDGs for a 2-level AND-OR circuit                                 | 48 |

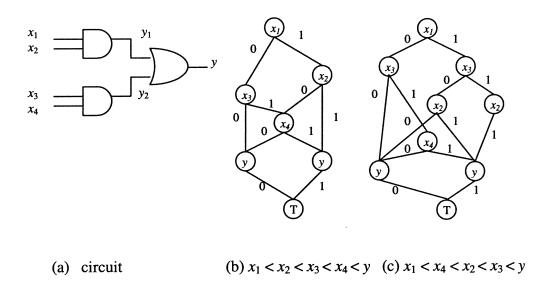

| Figure 4.4 MDGs for 3-sort multiplexer                                       | 49 |

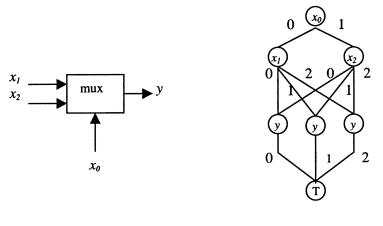

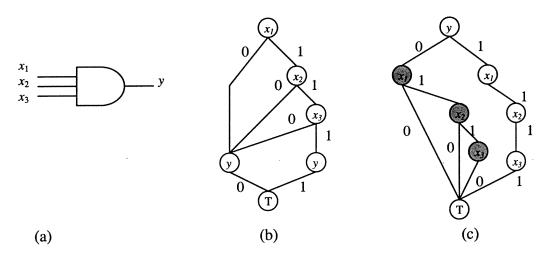

| Figure 4.5 MDGs for 3-input AND gate                                         | 50 |

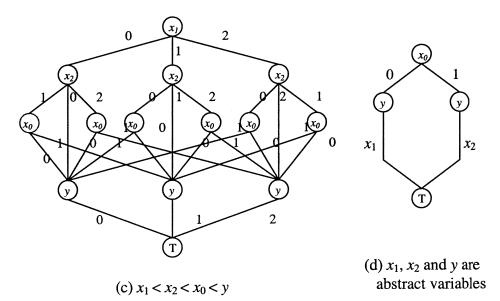

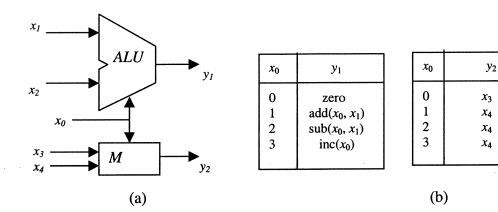

| Figure 4.6 MDGs for an ALU and a multiplexer                                 | 52 |

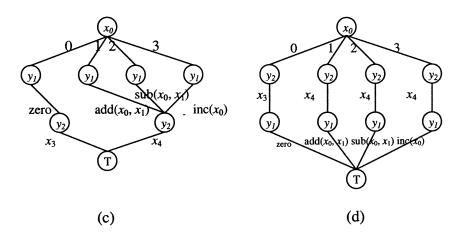

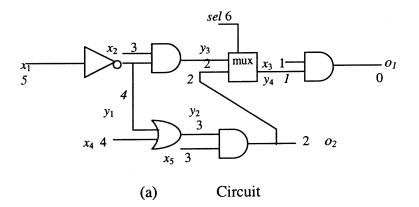

| Figure 4.7 A combinational circuit                                           | 54 |

| Figure 4.8 A static variable ordering algorithm for combinational circuits   | 57 |

| Figure 4.9 An example of application of the <i>svoc</i> algorithm            | 58 |

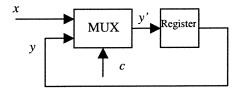

| Figure 4.10 A static variable ordering algorithm for sequential circuits     | 61 |

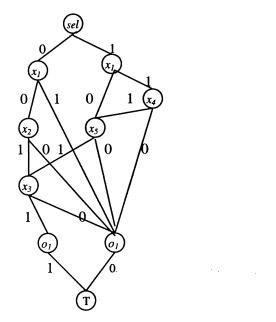

| Figure 4.11 An example of a register                                         | 63 |

| Figure 4.12 A circuit causing non-termination of procedure constraint-       |    |

| adjusting                                                                    | 63 |

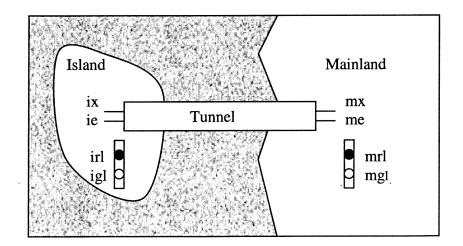

| Figure 4.13 The Island Tunnel Controller                                     | 66 |

| Figure 4.14 The Fairisle ATM Switch                                          | 68 |

| Figure 4.15 The header (routing tag) of a Fairisle ATM cell                  | 69 |

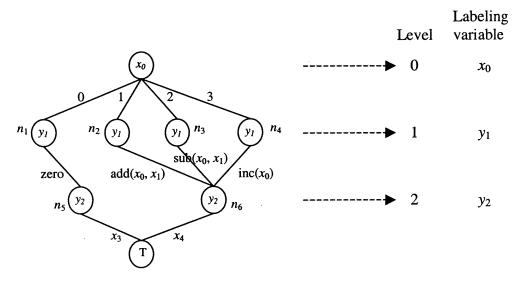

| Figure 5.1 A 3-level MDG                                                     | 72 |

| Figure 5.2 Variable swap between two abstract variables                      | 73 |

| Figure 5.3 Variable swapping between an abstract variable and a concrete     |    |

| variable                                                                     | 75 |

| Figure 5.4 Effects of swap operation on the order                            | 77 |

| Figure 5.5 | Sifting algorithm example        | .79 |

|------------|----------------------------------|-----|

| Figure 5.6 | An example of symmetry variables | 81  |

| Figure 5.7 | MDGs for an AND gate             | .82 |

| Figure 5.8 | An example of symmetry sifting   | .83 |

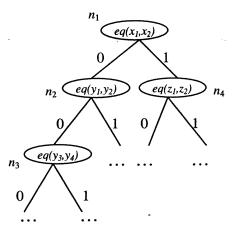

| Figure 6.1 TermID assignment for cross-terms with the same function symbol92   |

|--------------------------------------------------------------------------------|

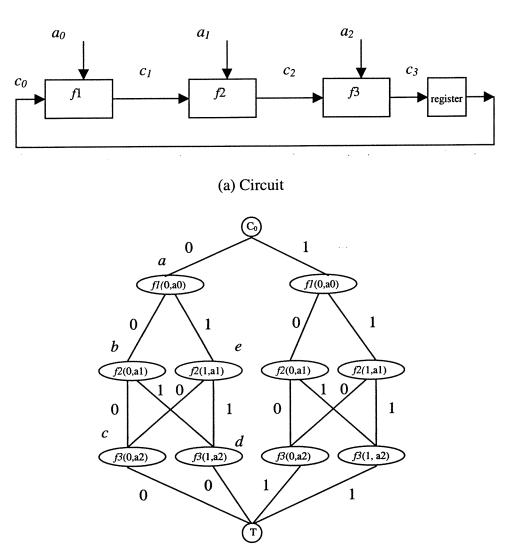

| Figure 6.2 A circuit with standard term ordering problem                       |

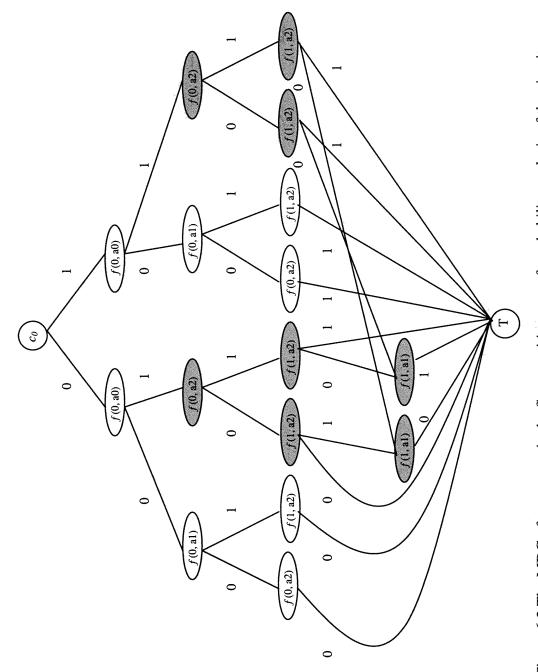

| Figure 6.3 The MDG of new states in the first transition step of reachability  |

| analysis of the circuit94                                                      |

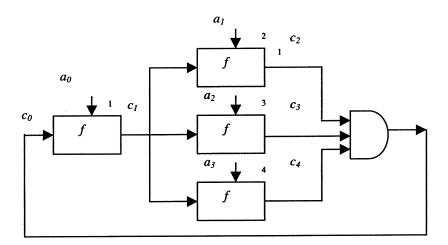

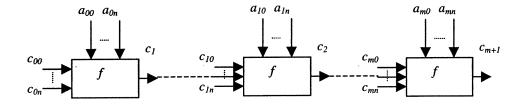

| Figure 6.4 Parallel structure of cross-functions                               |

| Figure 6.5 A common circuit structure resulting standard term ordering         |

| problem96                                                                      |

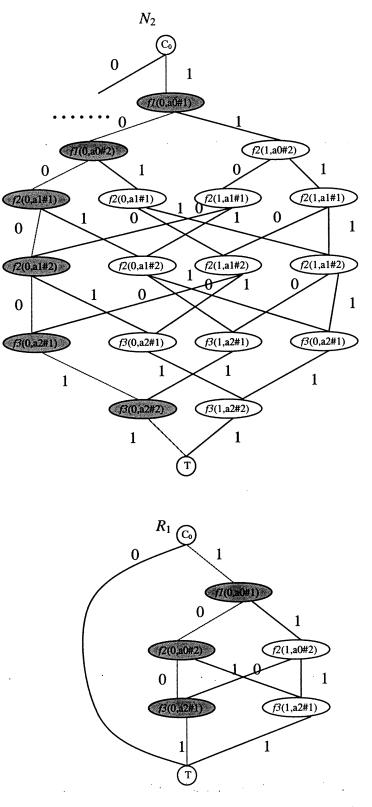

| Figure 6.6 The MDG after function renaming                                     |

| Figure 6.7 An example of the PbyS operation to compute the new froniter set101 |

| Figure 6.8 An ATM congestion controller103                                     |

•

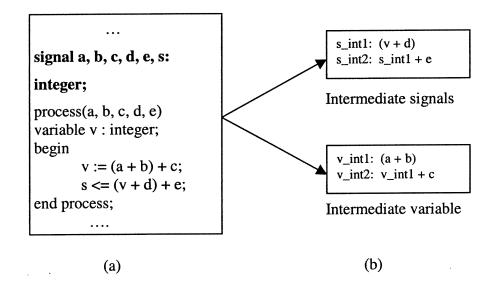

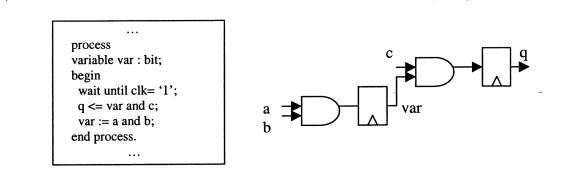

| Figure 7.1  | An example of definition of intermediate signals/variables | .106 |

|-------------|------------------------------------------------------------|------|

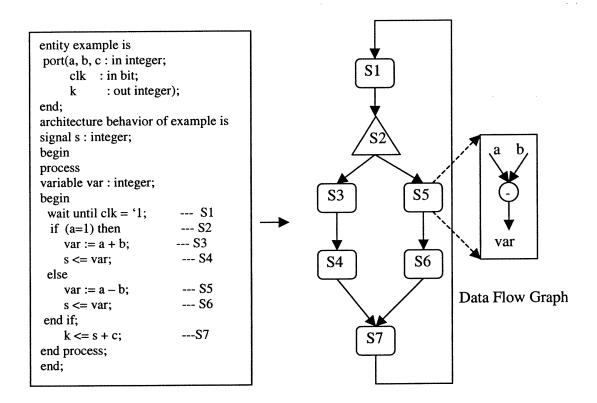

| Figure 7.2  | An example of a CDFG                                       | .108 |

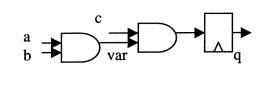

| Figure 7.3  | Illustration of rule 1 and 2                               | .110 |

| Figure 7.4  | Illustration of rule 3                                     | .111 |

| Figure 7.5  | An example of array abstraction                            | .114 |

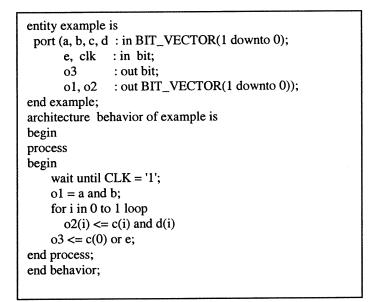

| Figure 7.6  | The VHDL model for ITC counter                             | .115 |

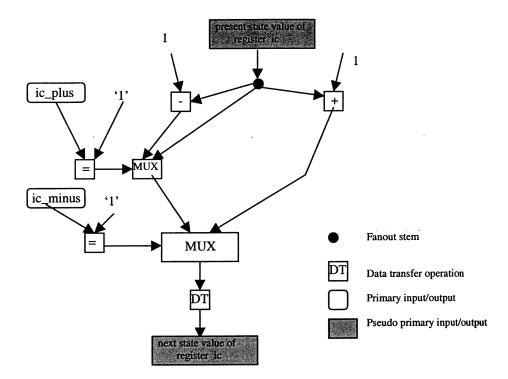

| Figure 7.7  | The DAG and the MDG-HDL model for the ITC counter          | .116 |

| Figure 7.8  | The VHDL model of a Moore machine                          | .117 |

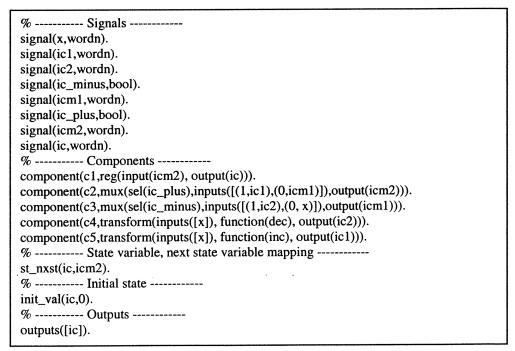

| Figure 7.9  | Directed Acyclic Graph for the Moore machine               | .118 |

| Figure 7.10 | 0 MDG-HDL model of the Moore machine                       | .119 |

|             |                                                            |      |

| Figure A.1 | The Island Tunnel Controller                                  | 139 |

|------------|---------------------------------------------------------------|-----|

| Figure A.2 | The state transition diagrams of the Island Tunnel Controller | 140 |

| Figure B.1 | The block diagram of the Fairisle ATM switch fabric           | 145 |

-

# List of Initials and Abbreviations

| ASM     | Abstract State Machine                                |

|---------|-------------------------------------------------------|

| ATM     | Asynchronous Transfer Mode                            |

| BTTL    | Branching Time Temporal Logic                         |

| CDFG    | Control/Data Flow Graphs                              |

| CTL     | Computation Tree Logic                                |

| DAG     | Directed Acyclic Graph                                |

| DF      | Directed Formula                                      |

| DNF     | Disjunctive Normal Form                               |

| EFSM    | Extended Finite State Machine                         |

| FSM     | Finite State Machine                                  |

| HDL     | Hardware Description Language                         |

| ITC     | Island Tunnel Controller                              |

| LTL     | Linear Temporal Logic                                 |

| MDG     | Multiway Decision Graph                               |

| MDG-HDL | Multiway Decision Graph-Hardware Description Language |

| PbyS    | Pruning by subsumption                                |

| ROBDD   | Reduced Ordered Binary Decision Graph                 |

| RTL     | Register Transfer Level                               |

| VHDL    | VHSIC Hardware Description Language                   |

. .

# Acknowledgements

First and foremost, I would like to express my heartfelt thanks to my supervisor, Dr. Eduard Cerny, for his extensive time, extreme patience, valuable suggestions and constant encouragement during my entire doctoral studies. It is he who looks after me as an international student, academically, financially and socially, always with great responsibility, which I appreciate so much and will always remain deeply in my memory.

I would also like to thank Michel Reid for his technical and administrative support, which is invaluable in working for this thesis. Many thanks to my friends and fellow graduate students in Lab Lasso, Jin Hou, Ying Zhang, and Mohammad-Sadegh Jahanpour for their help.

Last, but not least, I would like to thank all my family members: my parents, my sister, brother, and my husband for their full support and encouragement for my studies.

## **Chapter 1** Introduction

Technological advances in microelectronics have increased the complexity of digital hardware designs. Their correctness thus becomes a major concern, especially in critical applications where failure is unacceptable. Traditionally, the task of design validation is carried out by means of simulation. In a simulation-based approach, the designer needs to create a set of test vectors that represents the possible inputs to the system. The output for each of these test vectors is compared with the expected response. This method is very costly and incomplete because of the large number of input sequences to consider. In almost all practical situations it is infeasible to exhaustively simulate a design to guarantee its correctness.

Complement to simulation is the use of formal verification. Formal verification methods intend to establish that an implementation satisfies a specification by mathematical reasoning [33]. In this thesis, we refer to an implementation as the hardware design to be verified, and a specification as the property with respect to which the correctness of the implementation is to be determined. Formal verification conducts an exhaustive exploration of all possible behaviors. Thus, when a design is pronounced correct by a formal verification method, it implies that all behaviors relative to the property have been explored [14].

In this introduction, we first present the background for this thesis. The related research is introduced next. We then summarize the scope of this thesis in Section 1.3, and give an outline of the thesis in Section 1.4.

### **1.1 Background**

Formal verification methods can be classified in two main categories: interactive verification with a theorem prover and automated Finite State Machine (FSM) verification based on state enumeration [33].

Interactive verification with a theorem prover uses a powerful formalism such as higher-order logic that allows the verification problem to be stated at many levels of abstraction. This approach has achieved significant successes in verifying microprocessor designs. However, interactive verification has the drawback that the user is responsible for coming up with the proof of correctness and feeding it to the theorem prover, which requires great expertise.

Automated FSM verification based on state enumeration techniques provides automation for behavior comparison and model checking. Model checking works on a finite-state model of the system to be verified, and the logical specification of the desired behavior of the system model. Since model checking can be completely automatic and has been used successfully to verify complex sequential circuit designs and communication protocols, it is beginning to be used in industry.

A model checking approach to formal verification is based on exploring the reachable state space of its model. Finite state models of concurrent systems grow exponentially as the number of components of the system increases. This is known as the *state explosion* problem in automatic verification. The main challenge in model checking is dealing with this problem.

The most promising approach to the state explosion problem has been the application of ROBDD (Reduced Ordered Binary Decision Diagrams) to the representation of state graphs [7]. ROBDD can encode sets of states as well as transition and output relations, and perform an implicit enumeration of the state

space, thus making it possible to verify finite state machines with a larger number of states. Since the size of an ROBDD is largely influenced by the choice of the variable order, several approaches have been researched to find a good variable order [9, 21, 28, 29, 45, 55, 57].

For automated hardware verification, ROBDDs have proved to be a powerful tool. However, because they require a Boolean representation of the circuit, the size of an ROBDD grows, sometimes exponentially, with the number of Boolean variables. Therefore, ROBDD-based verification cannot be directly applied to circuits with complex and large datapaths.

To overcome this limitation, the verification group at the University of Montreal has proposed a new class of decision graphs called Multiway Decision Graphs (MDG). MDGs efficiently represent a class of formulas of a many-sorted first-order logic with a distinction of abstract and concrete sorts [16]. In an MDG, a data signal is represented by a single variable of abstract sort rather than by a vector of Boolean variables, and a data operation is represented by an uninterpreted function symbol. MDGs compactly encode sets of (abstract) states and transition/output relations for abstract description of state machines. The implicit enumeration technique is lifted from the Boolean level to the abstract level and referred to as implicit abstract enumeration. MDGs are thus much more compact than ROBDDs for circuits having complex and large datapaths. This greatly increases the range of circuits that can be verified.

However, both MDG-based and ROBDD-based verification systems still suffer from the problem of state explosion when handling realistic systems. To reduce the effects of this problem, one of the most important approaches is to select a good variable order. Like ROBDD, the size of the MDG heavily depends on its variable order. A good variable order can keep the size of MDG as small as possible and reduce the memory requirement and processing time. The concept of ordering in MDG concerns two orders: the standard term order and the custom symbol order. The standard term order is a total order of all the terms of the logic. The custom symbol order is a total order of a set of symbols that includes the concrete variables, abstract variables, and some but not necessarily all of the operators. The custom symbol order does not need to be compatible with the standard term order.

In this thesis, automatic static and dynamic variable ordering (custom symbol ordering) algorithms for MDG are explored. They are much more complicated than ROBDD because of the presence of first order terms in MDG. A standard term ordering problem is also identified and a solution is proposed. These algorithms and solutions are integrated into a VHDL-MDG design verification system.

## **1.2 Related Research**

Many researchers have been working on the state explosion problem in automatic formal verification. In this section we describe another approach called model reduction. It has been implemented on MDG [34]. The research on variable ordering on ROBDD will also be presented.

#### **1.2.1 Model Reduction**

A reduction method reduces the correctness problem to a similar problem with a smaller state space. This is generally done by replacing processes in the model by smaller processes that have similar or identical communication behaviors. The common reduction methods on ROBDDs include homomorphic reduction in language containment tests [43, 65], structural symmetry exploration [23] and partition refinement [18, 19].

Hou and Cerny have presented a model reduction algorithm for property checking [34]. For the property to be verified, the algorithm first constructs a property dependency graph that represents the function dependency of the property on the state variables. Starting from the set of state variables appearing in the property, the algorithm searches through the dependency graph and adds a non-correlated set of state variables to the current set of state variables to construct a more detailed model at each reduction iteration step [35]. This reduction algorithm is completely automatic and has been implemented on MDG. Experiments show that this method can achieve efficient reduction on benchmark circuits and has significantly increased the useful domain of MDG.

Model reductions and variable ordering both reduce the state space to alleviate state explosion and increase the number of circuits that can be verified. However, they each contribute in their own ways. Model reduction tries to build a smaller model based on the property to be verified. Variable ordering reduces the size of a decision graph by choosing a good variable order.

#### **1.2.2 Variable Ordering on ROBDD**

Bryant first presented the variable ordering problem in his landmark paper on ROBDD in 1986 [7]. Since then, there have been many researchers working on this problem. It is usually classified into three categories: static variable ordering to find an appropriate order before generating an ROBDD by using the logic circuit information that is the source of the Boolean function to be represented; dynamic variable ordering to reduce the ROBDD size by permuting the variables of a given ROBDD starting with the initial static order; and finally optimal variable ordering to find the best order for the ROBDD. It has been proven that

finding the optimal order is co-NP complete [3]. Many variable ordering algorithms produce acceptable results, so it is not necessary to find the optimal order. The most successful static ordering algorithm was proposed by Fujita in 1988 by minimizing the number of crosspoints of nets when the circuit graph is drawn [28]. Rudel first introduced a dynamic algorithm based on variable exchanges, called sifting [57]. Sifting allows many ROBDD operation sequences to succeed, when they would have failed with a fixed variable order. However, sifting is extremely expensive in both time and space.

## **1.3 Scope of the Thesis**

This thesis explores static and dynamic variable ordering algorithms on MDG. Compared to ROBDD, ordering on MDG has to deal with the constraints caused by abstract variables and uninterpreted function symbols. In this thesis an efficient static ordering method for combinational and sequential circuits and a dynamic ordering method for choosing an order in the middle of the verification process are proposed. Moreover, because some special decision nodes adopt standard term ordering, this situation may cause state explosion for circuits which have certain specific structures. This is called the standard term ordering problem. We propose a solution using function renaming and rewriting rules. All these methods make MDG work more efficiently.

Our MDG-based verification system only accepts a Prolog-style HDL, MDG-HDL, which allows the use of abstract variables for representing data signals. We developed a software to translate a VHDL model to MDG-HDL. The translator accepts a VHDL model as input and produces the representation for the MDG system. The VHDL model must be given at the synthesizable Register Transfer Level (RTL). Each VHDL process is transformed into a Directed Acyclic Graph (DAG) [58]. Then, MDG-HDL is generated from this DAG. This translator and

variable ordering make the MDG verification system more suitable for a large class of problems than before the introduction of these improvements.

My contributions in this thesis are as follows:

- 1. The development and implementation of automatic static variable ordering algorithms on MDG.

- 2. The development and implementation of dynamic variable ordering algorithms on MDG.

- 3. The identification of and a solution to the standard term ordering problem.

- 4. Automatic translation from DAG to MDG-HDL.

- 5. Integration of automatic variable ordering with the MDG package.

- 6. Experiments on benchmark circuits.

## **1.4 Outline of the Thesis**

This thesis discusses formal verification techniques, MDG-based verification approaches, variable ordering algorithms on MDG and a translation between VHDL and MDG-HDL. The thesis is organized as follows:

In Chapter 2, we review several formal hardware verification techniques.

In Chapter 3, we begin with describing the basic concepts of MDG. We then present MDG-based verification approaches.

In Chapter 4, we discuss the static variable ordering algorithms on MDG and the constraints on variable ordering that MDGs impose. It is difficult to derive a method that always yields the best order to minimize MDGs, but with our static algorithms, we can find a fairly good order in most cases.

In Chapter 5, we present dynamic variable ordering algorithms on MDG. When using a fixed static variable order, some MDG operations may run out of memory. Dynamic variable ordering allows these operation sequences to succeed when a new order is chosen mid-stream.

In Chapter 6, we start by explaining what the standard term ordering problem is. We then propose a solution based on function renaming and rewriting.

In Chapter 7, a translation method from VHDL to MDG-HDL is presented.

Finally, conclusions and future directions of research are stated in Chapter 8.

# **Chapter 2 Formal Hardware Verification**

Several approaches to formal verification have been proposed over the years. This chapter concentrates on the method called model checking by which a desired behavioral property of a reactive system is verified through exhaustive enumeration (explicit or implicit) of all the states reachable by the system and the behaviors that traverse though them [14]. We first review several modeling languages of design systems. We then describe model checking property specifications and systems. Finally, we discuss how to represent finite state reactive systems symbolically using Reduced Ordered Binary Decision Diagrams (ROBDDs) and review variable ordering on ROBDDs. This chapter introduces the related research and provides the theoretical basis for the subsequent chapters.

### 2.1 Modeling Languages

.

At their most detailed level, digital systems may consist of millions of elements, as would be the case if we view a system as a collection of logic gates or transistors. From a more abstract viewpoint, these elements may be grouped into a handful of functional components such as cache memories, floating-point units, signal processors, or real-time controllers. Hardware description languages have evolved to aid in the design of systems with this large number of elements with a wide range of electronic and logical abstractions [63]. Different design and verification systems may have different system description languages. Here we will review some of them, including Verilog, VHDL, SMV input language, Synchronous Verilog, and MDG-HDL.

#### 2.1.1 Verilog and VHDL

Verilog and VHDL are hardware description languages used to design and document electronic systems. They allow a designer to describe designs at a high level of abstraction such as at the architectural or behavioral level as well as the lower implementation levels (gate and transistor switch) [12].

Verilog and VHDL describe a digital system as a set of modules. Each of these modules has an interface to other modules as well as a description of its contents. A module represents a logical unit that can be described either by specifying its internal logical structure - for instance describing the interconnection of the actual logic gates it is comprised of, or by describing its behavior in a program-like manner - in this case focusing on what the module does rather than on its logical implementation. These modules can be interconnected with signals, allowing them to communicate.

The notion of a process plays a central role in VHDL and Verilog. All timedependent behavior is defined in terms of process statements. A process can be thought of as an independent thread of control, which may be quite simple, involving only one repeated action, or very complex, resembling a software program. It might be implemented as a sequential state machine, as a microcoded controller, as an asynchronous clearing of a register, or as a combinational circuit.

#### 2.1.2 SMV Input Language and Synchronous Verilog

The SMV system is a formal verification tool for checking finite state systems against specifications in the temporal logic CTL [47]. The input language of SMV is designed to allow the description of finite state systems that range from completely synchronous to completely asynchronous, and from the detailed to the abstract. One can readily specify a system as a synchronous Mealy machine, or as

an asynchronous network of abstract, nondeterministic processes. The language provides for modular hierarchical descriptions, and for the definition of reusable components. Because it is intended to describe finite state machines, the only data types in the language are finite ones: Booleans, scalars and fixed arrays. Static, structured data types can also be constructed. The primary purpose of the SMV input language is to describe the transition relation of a finite Kripke structure. Any expression in the propositional calculus can be used to describe this relation. The logic CTL allows a rich class of temporal properties, including safety, liveness, fairness constraints and absence of deadlock, to be specified using a concise syntax.

Those who are familiar with the Verilog modeling language may find it easier to write models for SMV in Synchronous Verilog (SV). This language is syntactically only a slight variation of the Verilog language. However, its semantics is not based on an event queue model, as in Verilog. Rather, SV is a synchronous language, in the same family as SMV [49]. Because SV provides a functional description of a design rather than an operational description of how to simulate it, SV is better suited than Verilog to such applications as hardware synthesis, cycle-based (functional) simulation and model checking [48].

#### **2.1.3 MDG-HDL**

Synchronous RT (Register-Transfer) level hardware designs can be suitably represented by Multiway Decision Graphs (MDGs), a class of decision graphs that subsumes the class of Reduced Ordered Binary Decision Graphs (ROBDDs) while accommodating abstract sorts and uninterpreted function symbols. The MDG tools are a prototype implemented in Prolog for the verification of RTL designs. They are intended for the verification of abstract descriptions of state machines rather than Finite State Machines (FSM). An abstract description of a state machine, called abstract state machine (ASM), is obtained by letting some data input, state

or output variables be of an abstract sort, and the operations on them be uninterpreted function symbols.

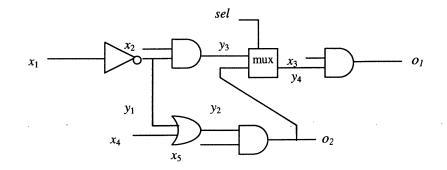

The hardware description language that MDG tools accept is a Prolog-style HDL, MDG-HDL, which allows the use of abstract variables for representing data signals. The MDG-HDL description is then compiled into the ASM synchronous model in internal MDG data structures. MDG-HDL supports structural descriptions, behavioral ASM descriptions, or a mixture of structural and behavioral descriptions. A structural description is usually a netlist of components (predefined in MDG-HDL) connected by signals. A behavioral description is given by a tabular representation of the transition/output relation or by a truth table [70].

### 2.2 Model Checking Property Specifications and Systems

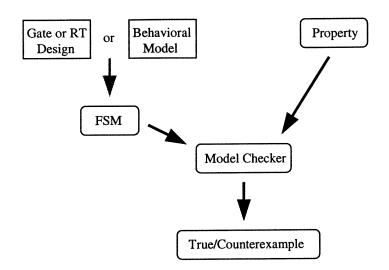

Model checking is an automatic technique for verifying finite-state reactive systems, such as sequential circuit designs and communication protocols. Specifications are expressed in a propositional temporal logic, and the reactive system is modeled as a state-transition graph. An efficient search procedure is used to determine whether or not the state-transition graph satisfies the specifications. A model checking system is described in Figure 2.1. This technique was originally developed by Clarke and Emerson in 1981 [14].

Model checking has several important advantages over mechanical theorem provers for verification of circuits and protocols. The most important is that the procedure is highly automatic. In general, a model checker builds or accepts a finite-automaton model of the system and checks whether or not the specified property holds on the model. If it does not, the model checker returns a failure trace. Normally, the property is expressed in a temporal logic which we describe next.

Figure 2.1 A model checking system

### **2.2.1 Temporal Logics**

A temporal logic is a formalism for describing sequences of transitions between states in a reactive system. It provides a formal system for qualitatively describing and reasoning about how the truth values of assertions change over time [33]. There are four basic operators in temporal logic:

- $\Box P$  is true in state s, if P is true in all future states from s (including s).

- $\Diamond P$  is true in state s, if P is true in some future states from s.

- OP is true in state s, if P is true in the next state from s.

- PUQ is true in state s, if either Q is true in s itself, or it is true in some future state of s, and until then P is true at every intermediate state.

The following three classes of properties can be easily expressed in temporal logic:

• Safety properties - assert that nothing "bad" happens, typically represented as |= □ P, i.e., P holds at all times in all models;

- Liveness properties assert that eventually something "good" happens, typically represented as |= P ⇒ ◊Q, i.e., in all models, if P is initially true then Q will eventually be true;

- *Precedence properties* assert the precedence order of events, typically represented as |= *PUQ*, i.e., in all models, *P* will hold until *Q* becomes true.

Based on the difference in viewing the notion of time, temporal logics can be classified into two kinds. In one case, time is characterized as a single linear sequence of events, leading to *Linear Time (Temporal) Logic*. In the other case, a branching view of time is taken, such that at any instant there is a branching set of possibilities into the future. This view leads to *Branching Time (Temporal) Logic*.

#### 2.2.2 Propositional Linear Temporal Logic

In a linear temporal logic the underlying structure of time is assumed to be isomorphic to the natural numbers with their usual order (N, <)[22]. Let AP be an underlying set of atomic proposition symbols. A linear-time structure M=(S, x, L) is defined such that

- S is a set of states,

- x: N-> S is an infinite sequence of states, and

- L: S->  $2^{(AP)}$  is a labeling of each state with the set of atomic propositions in AP that are true in the state.

Usually, the notation  $x = (s_0, s_1, s_2,...) = (x(0), x(1), x(2), ...)$  is employed to denote the *timeline* x, which is also referred to as a *fullpath*, or *computation sequence*, or *computation*.

The basic temporal operators of a Propositional Linear Temporal Logic (PLTL) are  $\mathbf{F}p$  ("sometimes p", also read as "eventually p"),  $\mathbf{G}p$  ("always p", also read as "henceforth p"),  $\mathbf{X}p$  ("nexttime p"), and  $p \mathbf{U}q$  ("p until q") [33].

#### 2.2.3 Computation Tree Logic

Different kinds of Branching Time Temporal Logic (BTTL) have been proposed depending on the exact set of operators allowed. The common feature is that they are interpreted over branching tree-like time structures, where each moment may have many successor moments. The structure of time corresponds to an infinite tree. The usual temporal operators ( $\mathbf{F}$ ,  $\mathbf{G}$ ,  $\mathbf{X}$ ,  $\mathbf{U}$ ) are regarded as state quantifiers. Additional quantifier called the path quantifier is provided to represent all path ( $\mathbf{A}$ ) and some path ( $\mathbf{E}$ ) from a given state. Here we only describe the Computation Tree Logic (CTL), a restricted form of BTTL.

Clarke and Emerson first proposed CTL and presented efficient algorithms for CTL model checking within a larger framework of automatic synthesis of synchronization skeletons from CTL specifications [14].

CTL severely restricts the type of formulas that can appear after a path quantifier only single linear time operator  $\mathbf{F}$ ,  $\mathbf{G}$ ,  $\mathbf{X}$ , or  $\mathbf{U}$  can follow a path quantifier and time operators cannot be combined directly with propositional connectives. The syntax of CTL is:

- Every atomic proposition is a CTL formula.

- If f and g are CTL formulas, then so are  $\neg f$ ,  $(f \land g)$ , AXf, EXf, A(fUg), E(fUg)

The remaining operators are derived from these according to the following rules:

$$f \lor g = \neg(\neg f \land \neg g)$$

$$\mathbf{AF}g = \mathbf{A}(\text{true U } g)$$

$\mathbf{EF}g = \mathbf{E}(\text{true } \mathbf{U} g)$  $\mathbf{AG}f = \neg \mathbf{E}(\text{true } \mathbf{U} \neg f)$  $\mathbf{EG}f = \neg \mathbf{A}(\text{true } \mathbf{U} \neg f)$

Because all the operators are prefixed by A or E, the truth or falsehood of a formula depends only on the given state s, and not on the particular branch.

Clarke, Emerson and Sistla demonstrated that CTL is an efficient means for verifying finite-state systems. In their approach, a finite-state system is modeled as a labeled transition graph which can be viewed as a *finite Kripke structure* represented as a triple M=(S, R, P), where

- *S* is a finite set of states,

- R is a total binary relation on states and represents possible transitions, and

- *P* is a mapping that assigns to each state the set of atomic propositions that are true in the state.

A path within this structure is naturally defined as an infinite sequence of states, with each adjacent pair related by R.

As its name suggests, CTL interprets temporal formulas over structures that resemble infinite computation trees. In the context defined above, given M and an initial state  $s_0$ , it considers the infinite computation tree rooted at  $s_0$ , generated by considering all possible nondeterministic transitions at every state. The truth of a CTL formula is defined inductively as follows:

- $(M, s_0) \models p$  iff  $p \in P(s_0)$ , where p is an atomic proposition

- $(\mathbf{M}, s_0) \models \neg f \text{ iff } (\mathbf{M}, s_0) \not\models f$

- $(M, s_0) \models f \land g \text{ iff } (M, s_0) \models f \text{ and } (M, s_0) \models g$

- $(M, s_0) \models AX f \text{ iff for all states } t \text{ such that } (s_0, t) \in \mathbb{R}, (M, t) \models f$

- $(M, s_0) \models EX f \text{ iff for some states t such that } (s_0, t) \in \mathbb{R}, (M, t) \models f$

- (M,  $s_0$ )  $\models \mathbf{A}(f \mathbf{U}g)$  iff for all paths ( $s_0, s_1, s_2 \dots$ ),  $\exists k \ge 0$  such that (M,  $s_k$ )  $\models g$ , and  $\forall i, 0 \le i < k, (M, s_i) \models f$

- (M, s<sub>0</sub>) |= E(f U g) iff for some paths (s<sub>0</sub>, s<sub>1</sub>, s<sub>2</sub> ...), ∃k≥0 such that (M, s<sub>k</sub>) |= g, and ∀i, 0≤i<k, (M, s<sub>i</sub>) |= f

Clarke, Emerson and Sistla showed that there is an algorithm for determining whether a CTL formula f is true in state s of the Kripke structure M = (S, R, P) which runs in time O(length(f)×(|S|+|R|)) [13].

An important consideration in the modeling of concurrency is the notion of *fairness*. Each fairness condition specifies a set of states in the machine, and requires that in any acceptable behavior these states must be traversed infinitely often. Fairness constraints are used to restrict the behavior of the design. Among possible fairness constraints, the following are very common ones [22]:

- Unconditional fairness: an infinite sequence is impartial iff every process is executed infinitely often during the computation.

- Weak fairness: an infinite computation sequence is weakly fair iff every process enabled almost everywhere is executed infinitely often.

- Strong fairness: an infinite computation sequence is strongly fair iff every process enabled infinitely often is executed infinitely often.

Since fairness cannot be expressed in CTL, Clark et al. modified the semantics of CTL to introduce the notion of fairness [13]. The new logic, called  $\text{CTL}^F$ , has the same syntax as CTL, but the structure is now a 4-tuple (S, R, P, F). S, R, P have the same meaning as in CTL and F is a collection of predicates on S. Fair paths in this context are defined as those along which states occurring infinitely often satisfy each predicate that belongs to F.

Because  $CTL^{F}$  still can not express strong fairness, Emerson and Lei defined Fair CTL by extending the notion of fairness in CTL to consider fairness constraints that are Boolean combinations of Fp (infinitely often p, same as GFp) and Gp (almost always p, same as FGp) operators [24]. Combinations of these operators can express strong fairness as well as unconditional and weak fairness.

Clarke and Emerson further extended CTL to  $CTL^*$  [14].  $CTL^*$  is sometimes referred to as full branching time logic. It combines both branching time and linear time operators; a path quantifier, either A or E can prefix an assertion composed of arbitrary combinations of the usual linear time operators G, F, X, and U. For example, EFp is a basic modality of CTL; E(Fp/Fq) is a basic modality of CTL\*.

LTL versus BTTL. In linear time logics, temporal operators are provided for describing events along a single future time line, although when a linear formula is used for program specification there is usually an implicit universal quantification over all possible futures. In contrast, in branching time logics the operators usually reflect the branching nature of time by allowing explicit quantification over possible futures. One argument presented by the supporters of branching time logic is that it offers the ability to reason about existential properties in addition to universal properties [33].

#### 2.2.4 ω-automaton based Model Checking

Basically,  $\omega$ -automata is the same as conventional automata that accept strings, except that the final states of the latter (signaling the end of an accepted string) are replaced by an acceptance condition on the set of states, visited infinitely often. It is useful for modeling non-terminating processes [41].

$\omega$ -automaton based model checking considers containment rather than equivalence between the languages representing the implementation and the specification (L(Imp) and L(Spec), respectively). In other words, it determines whether L(Imp)  $\subseteq$  L(Spec), thereby verifying that every behavior of the implementation satisfies the property expressed by the specification. This allows easier handling of partial specifications as well as abstractions, thereby facilitating hierarchical verification across different levels of abstraction. Kurshan implemented this approach in COSPAN which is the verification engine in the commercial tool FormalCheck [42].

In his work, Kurshan defined modified versions of finite-state automata and finitestate machines that accept sequences, called L-automata and L-processes, to represent specifications and implementations, respectively. A specification is typically represented by a deterministic L-automaton T (called a "task" in Kurshan's terminology) and an implementation by a nondeterministic L-process. A verification is cast in term of testing for a language containment, i.e., testing if  $L(A) \subseteq L(T)$ .

One of the greatest strengths of Kurshan approach is its use of reductions both to control the complexity of state-space analysis and to provide a basis for hierarchical verification. Because most techniques based on state-space analysis suffer form the problem of state-explosion, i.e., an exponential increase in the number of states with an increasing number of components, complexity management becomes a critical issue in practice. This is especially so since formal verification is expected to work on large problems that are beyond the reach of traditional simulation methods. Devoting effort to develop an underlying semantics that supports reduction methods has potentially many advantages, as it has been demonstrated by the work with COSPAN. Also, a method of hierarchical verification that includes stepwise refinement of specifications allows much larger systems to be handled in practice.

Though the approach described above has a strong theoretical basis with due regard to complexity issues, its application in practice is sometimes limited by the fact that the burden of providing a reduction transformation lies with the user. In order to realize the full potential of the system, some means of using its reduction mechanism is required. It is not always obvious which transformation works best, though the automated facility to check its validity does help in exploring different options.

#### 2.2.5 Symbolic Model Checking

One of the serious limitations of the model checking approach is its reliance on an explicit state-transition graph representation of the hardware system to be verified. Typically, the number of states in a global graph increases exponentially with the number of gates/processes/elements (parallel components) in the system, resulting in what is popularly called the state explosion problem. This restricts the application of direct state enumeration approaches to small circuits only. Several alternatives have been explored to alleviate this problem.

McMillan presented a method for model checking that reduces the state explosion problem by representing the Kripke model implicitly with a Boolean formula represented in computer memory using Bryant's ROBDDs [7]. This method is called symbolic model checking because symbolic variables are used to represent the components of the system state rather than numeric values. Using symbolic model checking, it is possible to verify automatically some regularly structured systems with literally astronomical numbers of states [47].

The symbolic model checking algorithm is implemented by a procedure *Check* that takes the CTL formula to be checked as its argument and returns an ROBDD that represents exactly those states of the system that satisfy the formula.

McMillan et. al. developed the Symbolic Model Verifier (SMV) to check finite state systems against specification in CTL [47, 48, 49]. McMillan and Schwalbe successfully applied SMV to the verification of the Encore Gigamax cache consistency protocol and found some critical design errors, thus demonstrating the effectiveness of symbolic model checking techniques for industrial applications.

#### 2.2.6 Existing Model Checkers

Several model checking tools have been developed over the last 10 years. The well-known ones are as follows:

- SMV (Symbolic Model Verifier): a symbolic model checking system developed by McMillan at Carnegie-Mellon University [48, 49]. This system permits the automatic verification of programs written in a specialized language for describing concurrent finite state systems and protocols.

- VIS (Verification Interacting with Synthesis): an integrated tool for verification, simulation and synthesis of finite state systems, developed at University of California at Berkeley. It contains a Fair CTL Model Checker and a behavioral equivalence checker for sequential circuits, language emptiness check for Büchi automata and combinational verification [6].

- CVE: an industrial verification environment developed at Siemens. It supports model checking of designs described in VHDL or EDIF against specifications given in a temporal logic called CIL [60].

- FormalCheck: an ω-automata based model checker based on Cospan developed at Bell Labs Design Automation, Lucent Technologies. The

reduction algorithms and refinement methodologies embedded in FormalCheck make the tool applicable to industrial-size designs [75].

The advantage of model checking techniques is that they can be made completely automatic. The major obstacle for model checking to be widely used in an industrial design flow is the state explosion problem. The most promising approach to this problem is the application of Reduced Ordered Binary Decision Diagrams (ROBDDs) to the representation of state graphs [7]. In the next section, we introduce ROBDDs and variable ordering on them.

## 2.3 Reduced Ordered Binary Decision Graphs

Model checking verification systems have been considerably improved by the application of BDDs to the representation of Boolean functions. In this approach, the explicit construction of state graphs is avoided. Instead, the state graph is implicitly represented by means of Boolean functions from sets of states to sets of states (predicate transformers).

#### 2.3.1 Binary Decision Diagrams

"BDD" stands for "Binary Decision Diagram". A BDD over a set of  $X_n = \{x_1, ..., x_n\}$  of Boolean variables is a directed acyclic graph with one source and at most two sinks labeled by 0 and 1 [1]. Each non-sink (internal) node is labeled by a variable in  $X_n$  and has two outgoing edges, corresponding to where the variable evaluates to a 0 and to a 1, respectively. For a given assignment to the variables, the function value is evaluated by tracing a path from the root to the terminal. For a given input  $m = (m_1, ..., m_n)$ , the evaluation starts at the root and at an internal node with label  $x_i$  the outgoing edge with label  $m_i$  is chosen [7].

Although BDDs have been researched for about four decades, their widespread use occurred only after Bryant showed that under two restrictions such graphs are canonical and can be easily manipulated. The first restriction is that a total ordering of the variables is enforced in the graph. That is, if we consider variables to be ordered as  $x_1 < x_2 < ... < x_n$ , then every path from the root to a sink encounters the variables in that order. The second restriction is that the graph is reduced. A graph can be reduced by the repeated application of the following two rules until they are no longer applicable [7]. These rules are:

- Merging Rule: Two isomorphic subgraphs should be merged.

- Deletion Rule: A vertex whose two branches point to the same vertex should be deleted.

The resulting BDD is called a Reduced Ordered BDD (ROBDD). The important symbolic manipulation procedures introduced by Bryant are *apply* and *compose*; these techniques operate on two identically ordered ROBDDs. *apply* allows two ROBDDs to be combined under some Boolean operations, and *compose* allows the substitution of an ROBDD variable with a function.

#### 2.3.2 Variable Ordering on ROBDD

The size of an ROBDD representing a Boolean function can be exponential in the number of primary inputs in the worst case. This problem is commonly referred to as the "memory explosion" problem. One solution is to find a good variable order to reduce the size of an ROBDD because the size of an ROBDD is strongly dependent on this order [37].

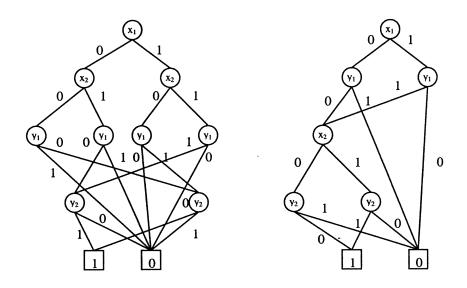

For example, suppose we wish to build a BDD for the function  $(x_1 \oplus y_1) \lor (x_2 \oplus y_2)$ . Figure 2.2 shows two BDDs for this function using two different variable

orders. In general, the choice of the variable order can make the difference between a linear size BDD and an exponential one.

Figure 2.2 ROBDDs for the same function under two different variable orders

Much of the prior research in ROBDD has focused on finding good variable orders to reduce the size of an ROBDD representing a Boolean function. The methods for finding a good variable order can be classified into three categories:

- Static ordering: static methods based on information derived from the analysis of a multilevel logic implementation.

- Dynamic ordering: gradual improvement based on variable exchanges.

- Optimal ordering: exhaustive methods aimed at finding the best order.

The best published algorithms for the computation of an optimal variable order is a dynamic programming approach proposed in 1987 by Fridman and Supowit with a run time of  $O(n^23^n)$  [26]. Bollig and Wegener have proved in 1994 that finding the best order is co-NP complete [3].

Since static and dynamic heuristic ordering methods can find a suitable order for most of realistic systems, it is not necessary to find the best order. Thus we only discuss static and dynamic methods here.

#### 2.3.3 Static Variable Ordering

Because the choice of a good variable order is essential for the use of ROBDDs', many heuristics have been suggested. As any heuristic methods, they sometimes lead to a good variable order and sometimes they fail to compute a suitable order. The first and most successful static ordering algorithm was proposed by Fujita in 1988 [28]. His algorithm is based on two theorems:

*Theorem 1* One of the best orders for a tree circuit (the number of fanouts of all inputs and gates is one) composed of only AND, OR and NOT gates is acquired by the following procedure: Traverse the gates from an output to the inputs in depth-first order (selection of input nets of a gate is arbitrary), and when an input is found, append that variable to the end of the current order.

Theorem 2 One of the best orders for a circuit which is composed of only AND, OR and NOT gates where only one input or gate has fanout of more than one (number of fanouts of all the other inputs and gates is one) is acquired by the following procedure which is slightly modified from that in Theorem 1: Traverse the gates from an output to the inputs in depth-first order, but a net which has fannout of more than one is selected first. When we find an input, append that variable to the end of the current order.

A heuristic ordering algorithm was developed from the two theorems. It gives a natural order by a depth-first traversal of a circuit (according to Theorem 1) and inputs which have fanout more than one are considered first (according to Theorem 2). The algorithm gives a good order for most of examples.

#### 2.3.4 Dynamic Variable Ordering

Dynamic variable ordering was developed to allow ROBDD operation sequences that fail when using a fixed variable order to succeed when a new order is chosen mid-stream. This is done dynamically since ordering is performed by periodically applying a minimization algorithm which reorders the variables of the ROBDD to reduce its size. The sifting algorithm developed by Richard Rudel is one of the best reordering algorithms [57].

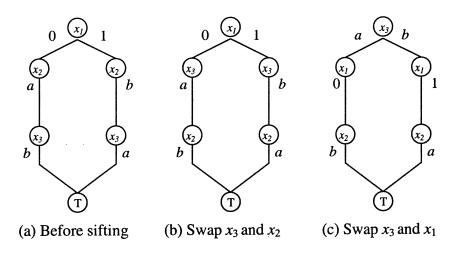

In the sifting algorithm, given an ROBDD G, a variable v is successively moved to each position in the order and the resulting graph size is examined. The variable is finally assigned the position which results in the smallest graph size. This process is known as sifting and is repeated for each variable in the graph.

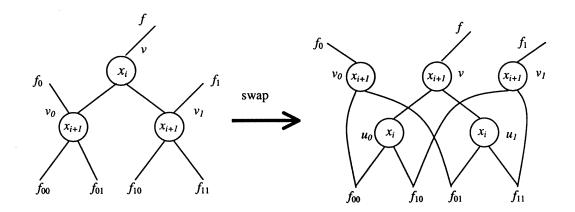

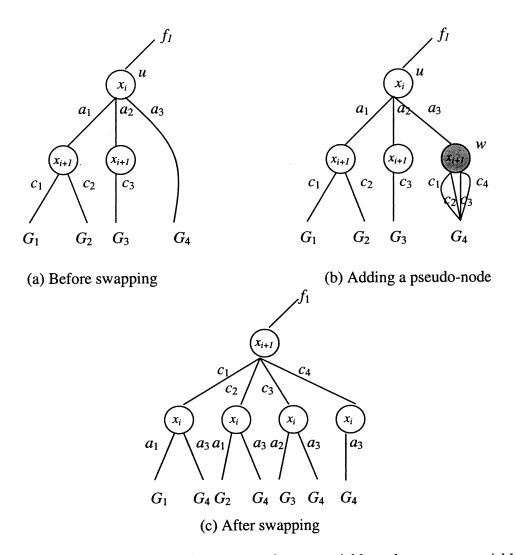

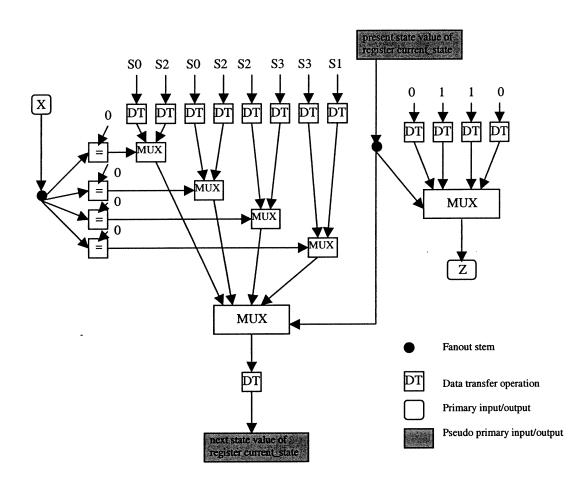

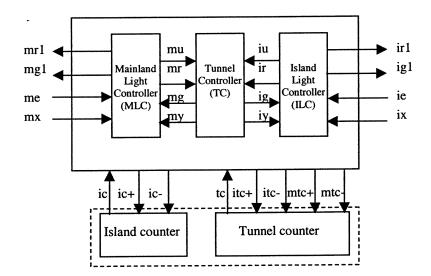

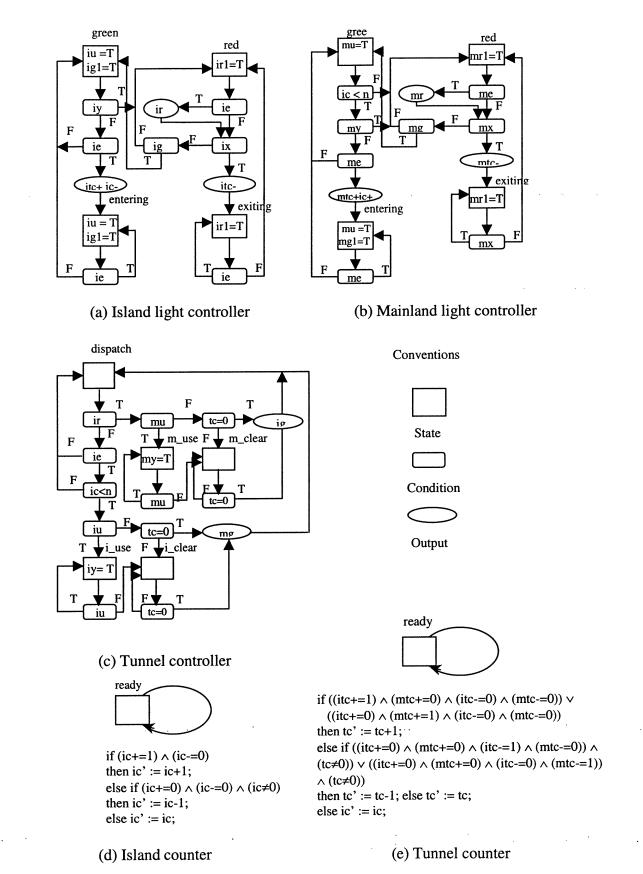

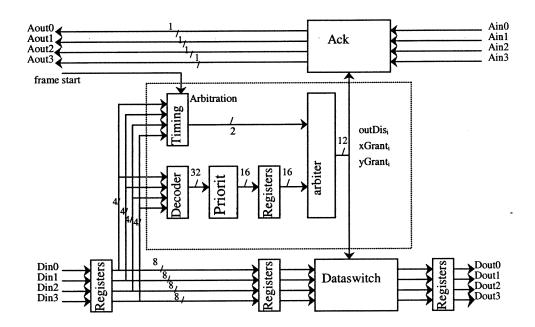

The basic operation in reordering is the exchange of two adjacent variables (swap operation), which can be done in linear time [8]. Variable swapping involves moving all ROBDD nodes at level *i* to level *i* + 1 and nodes at level *i* + 1 to *i*. Figure 2.3 illustrates the procedure for swapping variables  $x_i$  and  $x_{i+1}$  in an ROBDD. Suppose in the original order, function *f* is indicated by a pointer to a node *v* in the ROBDD, where node *v* is labeled by variable  $x_i$ . After swapping, function *f* is indicated by a pointer to a node labeled by  $x_{i+1}$ ; this node has branches to nodes labeled by  $x_i$ ; these nodes in turn have branches to the subgraphs  $f_{00}$ ,  $f_{10}$ ,  $f_{01}$ , and  $f_{11}$ ). Function *f* is still indicated by a pointer to node *v*, and other pointers to existing functions (shown as  $f_0$  and  $f_1$ ) remain undisturbed.