#### Université de Montréal

## Compositional Verification Using Interface Recognizers/Suppliers (IRS)

Par

#### Mohammad-Sadegh Jahanpour

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

Thèse présentée à la Faculté des études supérieures en vue de l'obtention du grade de Philosophiae Doctor (Ph. D.) en informatique

Juillet 2001

© Sadegh JAHANPOUR, 2001

9A 76 USY 2002 V. 004

•

. . .

J

# **Compositional Verification Using Interface Recognizers/Suppliers (IRS)**

Mohammad-Sadegh Jahanpour

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

# Université de Montréal Faculté des études supérieures

Cette thèse intitulée

## Compositional Verification Using Interface Recognizers/Suppliers (IRS)

présenté par

### Mohammad-Sadegh JAHANPOUR

a été évaluée par un jury composé des personnes suivantes:

| 1. Michel BOYER          |

|--------------------------|

| (président-rapporteur)   |

| 2. Eduard CERNY          |

| (directeur de recherche) |

| 3. Ivo ROSENBERG         |

| (membre du jury)         |

| 4. Gert SABIDUSSI        |

| (membre du jury)         |

| 5. Radu NEGULECU         |

| (examinateur externe)    |

### Acknowledgment

I am grateful to my advisor professor Eduard Cerny for encouraging and guiding me during my Ph.D. study. He teaches, listens and trusts his students, and my biggest fortune was in having him as my supervisor. I thank him for guidance over the years.

I would like to give my gratitude to the enthusiastic friends in lab LASSO at the University of Montreal for creating such a wonderful environment. In particular, I would like to thank professors E. M. Aboulhamid and S. Tahar for their encouragements and colaborations. I thank our friendly administrator Michel Reid for his quick and fast maintenance of lab equipments.

Iranian Ministry of Research and Higher education and my parents were instrumental in my coming Canada for graduate education. My wife, Rita supported me during my stay in Montreal. Without her love, affection and understanding, this thesis would have not been possible.

### **Sommaire**

Les blocs pre-conçus et pre-vérifiés, appelés les blocs de propriété intellectuelle (IP), sont de plus en plus utilisés dans la conception des systèmes microélectroniques. D'une part, ils facilitent la conception des systèmes et, d'autre part, ils contribuent de façon significative à l'évolution du produit.

Cependant la vérification de ces systèmes, intégrant les blocs IP devient un véritable défi et une tâche très laborieuse. En effet, la difficulté réside dans le fait qu'un bloc IP fonctionne correctement seulement dans son propre environnement et il est peu probable qu'il maintient ses propriétés dans un environnement arbitraire.

Afin de garantir le bon fonctionnement de ces systèmes, un bloc IP non seulement doit être certifié mais son environnement doit être aussi mis en exergue. Dans cette direction, l'approche supposition/garantie¹ est un support idéal aussi bien pour spécifier le comportement attendu du système que pour prouver certaines de ses propriétés. Ainsi, la spécification des blocs IP se subdivise en deux parties. La première partie décrit les hypothèses que le composant suppose sur son environnement tandis que la deuxième partie spécifie les propriétés du composant. D'une manière intuitive, cette décomposition est justifiée par le fait que le composant garantit ses propriétés lorsque son environnement satisfait les hypothèses que le composant suppose.

L'inconvénient du paradigme supposition/garantie est que les hypothèses et les propriétés sont souvent exprimées en logique temporelle ou bien dans un langage

propre des outils qui supportent ce type de spécification, comme MOCHA à titre d'exemple [37]. Cette dépendance de la logique ou d'un outil particulier n'est pas acceptable à la spécification des blocs IP car il limite généralité, réutilisablilité et portabilité des blocs. C'est pourquoi, nous introduisons les automates acceptants/imposants pour la spécification supposition/garantie des blocs IP. Ensuite, nous proposons un paradigme formel pour la vérification compositionnelle des systèmes intégrants de ces blocs.

Cette thèse est constituée de 6 chapitres :

Dans le premier chapitre, nous introduisons le problème d'intégration des blocs IP. Nous discutons aussi les objectives des travaux présentés dans les chapitres suivants.

Dans le deuxième chapitre, nous présentons une synthèse de la littérature récente reliée à la vérification formelle des composants matériels<sup>2</sup>. Ce chapitre introduit les notions mathématiques utilisées dans la thèse et regroupe un ensemble de méthodes supposition/garantie et les méthodes de vérification sémantique compositionelles<sup>3</sup>. Nous classifions ces méthodes par deux critères : (1) Est-ce que la méthode en question permet un raisonnement/composition circulaire des propriétés des composants de système? (2) Est-ce que cette méthode peut être appliquée aux compositions des propriétés de sûreté ainsi qu'aux propriétés de vivacité?

Dans le troisième chapitre, nous proposons d'utiliser les automates acceptants/imposants<sup>4</sup> pour spécifier les hypothèses d'environnement de composant, par exemple, un bloc IP. Un automate acceptant/imposant est un automate qui a été augmenté par certaines contraintes booléennes. Ces contraintes décrivent ce que doit être fourni à l'entrée de l'automate dans ses états. Les contraintes restent satisfaites tant que le comportement de l'environnement de l'automate est conforme au

<sup>&</sup>lt;sup>1</sup> Assume-guarantee

<sup>&</sup>lt;sup>2</sup> Hardware

<sup>&</sup>lt;sup>3</sup> Compositional model checking

<sup>&</sup>lt;sup>4</sup> Interface Recognizers/Suppliers (IRS)

comportement décrit par ces contraintes. Ainsi, on représente le comportement par l'automate acceptant. Supposons que nous modélisons les hypothèses d'environnement d'un composant par un automate acceptant. Nous composons cet automate avec le composant et nous imposons une condition que les contraintes d'automate soient maintenues (vrais) pendant toute la vérification du composant. Le vérificateur sémantique<sup>5</sup> doit appliquer toute la séquence de données qui satisfait les contraintes de l'automate. De cette façon, l'automate acceptant caractérise les séquences de données du composant. Ce dernier nous permet de vérifier le composant dans un environnement propre. Nous décrivons la syntaxe et la sémantique de ce type d'automate dans ce chapitre.

En guise d'exemple, nous décrivons un modèle d'un commutateur ATM<sup>6</sup> dans les chapitres 4 et 5. Notre objectif est d'illustrer l'application de l'automate acceptant/imposant à la spécification et vérification d'un système complexe. Ce commutateur est comosé d'un ensemble de contrôleurs et un commutateur. Nous décrivons les hypothèses des environnements du contrôleur et du commutateur. Dans le chapitre 4, nous démontrons que les hypothèses des contrôleurs sont respectées par le commutateur et vice-versa, les hypothèses du commutateur sont respectées par le commutateur. De la même façon, nous illustrons dans le chapitre 5 que ce type d'automate peut être utilisé pour la spécification et la vérification compositionelle des propriétés de sûreté et de vivacité du commutateur ATM.

Nous concluons ce travail en chapitre 6 en mettant en évidence les aspects pratiques de l'automate proposé, en particulier son application à la vérification des processeurs ainsi qu'aux systèmes de protocoles de télécommunication multicouche.

<sup>5</sup> Model checker

<sup>&</sup>lt;sup>6</sup> Asynchronous Transfer Mode

## **Abstract**

In this thesis, we review recent developments in compositional and assume guarantee verification. We discuss whether each method supports circular/non circular reasoning and whether it can be used when proving safety/liveness properties.

We formulate interface recognizers/suppliers (IRS), which are recognizers augmented with Boolean constraints. The constraints specify what values may occur on IRS inputs at each state. In other words, IRS can constrain its inputs.

We discuss a composition theorem for circular reasoning using IRS. In this way, IRS framework extends non-circular constraint model checking [25] to a circular constrainted model checking.

We demonstrate an application of IRS in (1) specifying environment assumptions and in (2) modeling pre conditions / post conditions of properties of an ATM switch. Using IRS, we specify and then verify the switch.

# **Abreviations**

A/G Assume guarantee

ATM Asynchronous Transfer Mode

CMC Constraint Model Checking

CTL Computation Tree Logic

CV Compositional Verification

FIFO first in first out

FSM Finite State Machine

IP Intellectual Property

**IRS** Interface Recognizer/Supplier

LTL Linear Temporal Logic

RTL Register Transfer Level

TBL tableau

TLA Temporal Logic of Actions

WFC Well-foundedness Conditions

# **List of Symbols**

| $C_{x}$                             | A constraint over signal x                                             | 34 |

|-------------------------------------|------------------------------------------------------------------------|----|

| F                                   | Linear Temporal Logic Eventually operator                              | 10 |

| f <sub>RS</sub> (s)                 | Characteristic function of reachable state (RS)                        | 40 |

| G                                   | Linear Temporal Logic Globally operator                                | 10 |

| $I(C_x)$                            | Constraint C <sub>x</sub> of interface recognizer I is set always true | 31 |

| $\mathbf{p} ^{t}$                   | property $p$ from time 0 upto (including) time $t$                     | 16 |

| p(t)                                | property p at time t                                                   | 16 |

| RS                                  | Set of reachable states                                                | 40 |

| U                                   | Linear Temporal Logic Until operator                                   | 10 |

| X                                   | Linear Temporal Logic Next-time operator                               | 10 |

| $\xrightarrow{k}$                   | $k$ -delay dependency, $k \ge 0$                                       | 33 |

| $\stackrel{k}{\longleftrightarrow}$ | Conditional $k$ -dependency. $k \ge 0$                                 | 34 |

# **Table of Contents**

| Chapter 1 Introduction                                | 1  |

|-------------------------------------------------------|----|

| 1.1 Motivations                                       | 1  |

| 1.2 Contributions                                     | 4  |

| Chapter 2 Compositional verification rules            | 7  |

| 2.1 Assume guarantee reasoning (A/G)                  | 12 |

| 2.2 Compositional verification                        | 13 |

| 2.2.1 Non circular compositional verification         | 14 |

| 2.2.2 Circular compositional verification             | 14 |

| 2.2.3 Reactive modules [35]                           | 19 |

| 2.3 Summary                                           | 21 |

| Chapter 3 Constraints in model checking               | 24 |

| 3.1 Constrained model checking                        | 24 |

| 3.2 Assume guarantee in constrained model checking    | 26 |

| 3.3 Constrained model checking with monitors          | 27 |

| 3.4. Interface recognizer/suppliers                   | 28 |

| 3.5 Logical foundation of composition using IRS       | 33 |

| 3.5.1 Well-foundedness/compatibility conditions (WFC) | 38 |

| 3.5.2 Generalization                                  | 48 |

| 3.6 Summary                                           | 50 |

| Chapter 4 ATM Switch Specification                    | 52 |

| 4.1 Fairisle ATM switch [32]                          | 53 |

| 4.2 Global specification                              | 56 |

| 4.3 Specification of the components                   | 57 |

| 4.3.1 In port controller specification.                             | 57  |

|---------------------------------------------------------------------|-----|

| 4.3.2 Fabric specification                                          | 59  |

| 4.4 Summary                                                         | 64  |

| Chapter 5 Formal Verification of an ATM Switch                      | 65  |

| 5.1 In Port controller implementation                               |     |

| 5.2 Arbiter abstraction                                             |     |

| 5.3 Receiver subsystem                                              |     |

| 5.3.1 FIFO/receiver interface machine I <sub>1</sub>                |     |

| 5.3.2 Receiver/memory interface                                     |     |

| 5.4 Queue R interface                                               |     |

| 5.5 Combining local properties of the receiver and the queue R      |     |

| 5.6 Dispatcher and scheduler subsystems                             |     |

| 5.7 Transmitter subsystem                                           |     |

| 5.7.1 Interface recognizers in the transmitter subsystem            | 86  |

| 5.7.2 Transmitter liveness                                          |     |

| 5.8 Composing local properties of the in port controller components | 90  |

| 5.8.1 Circular reasoning to prove liveness property                 | 95  |

| 5.9 Switch fabric verification                                      |     |

| 5.10 Composing in port controllers and the fabric                   | 104 |

| 5.11 Summary                                                        |     |

| Chapter 6 Conclusions and future work                               | 109 |

| 6.1 Future work:                                                    |     |

| References                                                          | 113 |

| Appendix I Assume guarantee in reactive modules[36]                 | 118 |

| Appendix II Technical details                                       |     |

| B1. Data abstraction by data independence assumption                |     |

| B2. Simulation relation                                             |     |

| B3. Realtionship between upto- and at-inductions                    |     |

| Appendix III SMV model of a queue                                   | 127 |

| Appendix IV VHDL models of the switch fabric and the port control | oller 131 |

|-------------------------------------------------------------------|-----------|

| C1. The receiver                                                  | 131       |

| C2. The dispatcher                                                | 145       |

| C3. The scheduler                                                 | 149       |

| C4. The transmitter                                               | 151       |

| C5. The arbiter                                                   | 156       |

| C6. The fabric                                                    | 157       |

# **List of Figures**

| Figure 2.1: a) A Moore machine M and b) the corresponding structure                        |    |

|--------------------------------------------------------------------------------------------|----|

| struct(M) [6]                                                                              | 9  |

| Figure 2.2: a) Cycle-of-gates. (b) The cycle is broken by a register                       | 15 |

| Figure 2.3: The assume guarantee rule. Steps b) and c) prove a)                            | 21 |

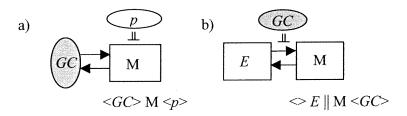

| Figure 3.1: Assume guarantee reasoning in constrained model checking                       | 27 |

| a) Module M under constraint GC satisfies property $p$ . b) $E  M$                         |    |

| discharges assumption GC                                                                   | 27 |

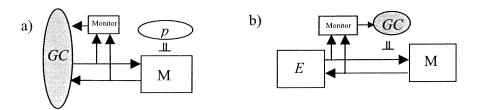

| <b>Figure 3.2</b> : Constrained model checking using monitors. a) $<$ GC $>$ M $\parallel$ |    |

| Monitor . b) <> E    M    Monitor <gc></gc>                                                | 28 |

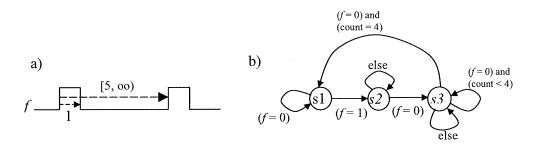

| Figure 3.3: A recognizer for the pulse generator f                                         | 29 |

| a) Specification. b) The recognizer. The "variable" count is zero                          |    |

| in state s1, one in state s2, and is incremented in state s3 until                         |    |

| reaching 5                                                                                 | 29 |

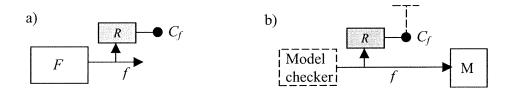

| Figure 3.4: Interface recognizer/supplier_a) Recognizer R for pulse                        |    |

| generator F. b) When $C_f = \text{true}$ , R shapes f for a module M                       | 30 |

| Figure 3.5: A drawing convention for interface recognizer/supplier_a)                      |    |

| Modules M1, $M2$ , and an interface recognizer $I(C_x, C_y)$ . b) $C_x$ is                 |    |

| activated and C <sub>y</sub> is checked.                                                   | 32 |

| Figure 3.6: Cycle of gates problem in IRS. a) An IRS I and its constraints                 |    |

| $C_x$ and $C_y$ . b) $C_x$ is activated and $C_y$ is checked in M1. C) $C_y$ is            |    |

| activated and C <sub>x</sub> is checked in M2                                              | 33 |

| Figure 3.7: Conditional cycle-of-gates in IRS I(C <sub>x</sub> , C <sub>y</sub> )          | 38 |

| <b>Figure 3.8</b> : Modules $M1$ and $M2$ and the IRS $I(C_x, C_y)$                        | 39 |

|                                                                                            |    |

| Figure 3.10: Projections of the constraints $C_x$ and $C_y$ over states of the IRS                                                           | 47 |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.11: Application example of the compositional rule using IRS_(a)                                                                     |    |

| Modules $M1$ and $M2$ and their IRS I( $C_x$ , $C_y$ , $C_z$ ). (b) Assume                                                                   |    |

| guarantee reasoning.                                                                                                                         | 48 |

| Figure 3.12: Three modules with IRS machines I <sub>1</sub> and I <sub>2</sub> .                                                             | 49 |

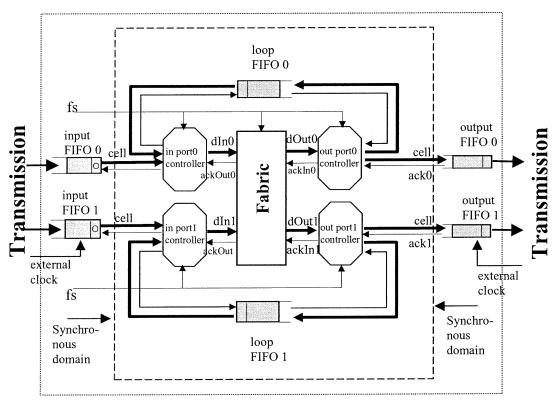

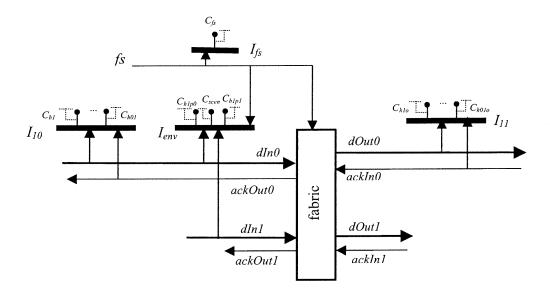

| Figure 4.1: A 2x2 Fairisle switch (the original switch is 4x4 [32])                                                                          | 55 |

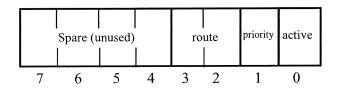

| <b>Figure 4.2:</b> Routing tag h1 for a 4x4 Fairisle switch [32]                                                                             | 55 |

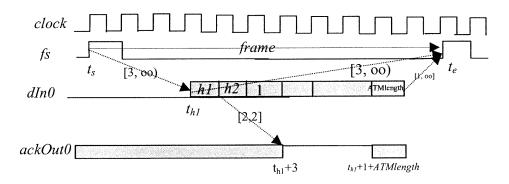

| Figure 4.3: Timing diagram specification for the in port0/fabric interface in                                                                |    |

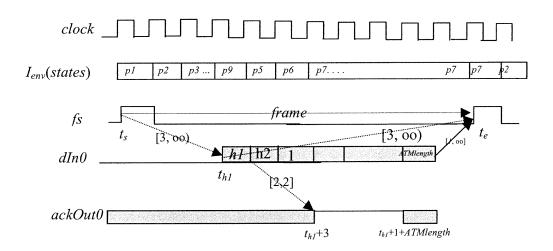

| Figure 4.1                                                                                                                                   | 60 |

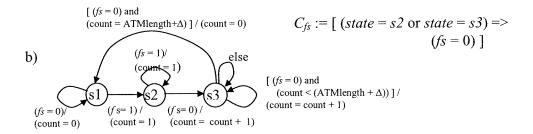

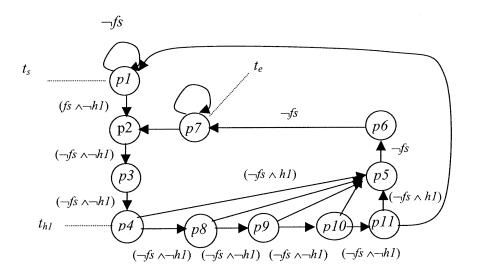

| <b>Figure 4.4</b> : IRS and its constraint $C_{fs}$ for frame start pulse $fs$ . A parameter                                                 |    |

| $(\Delta > 2 + t_{hl} - t_s)$ determines the frame size in Figure 4.3                                                                        | 61 |

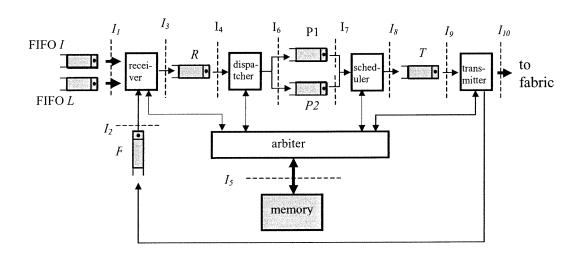

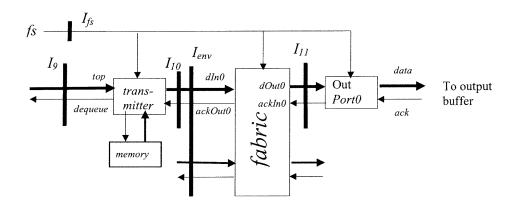

| Figure 5.1: An ATM switch in port controller                                                                                                 | 66 |

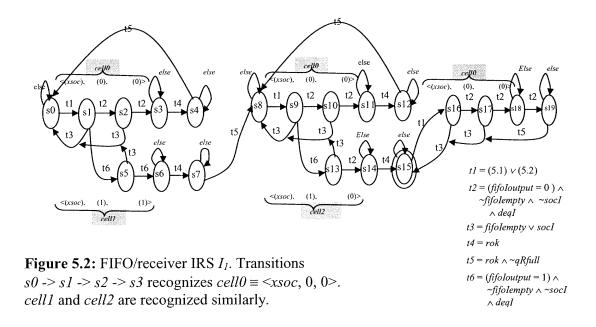

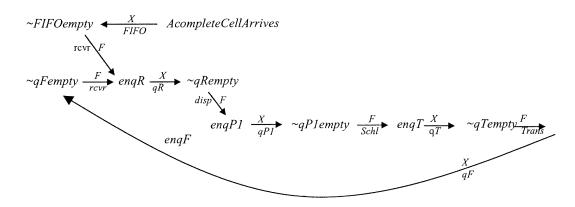

| <b>Figure 5.2:</b> FIFO/receiver IRS $I_1$ . Transitions_s0 -> s1 -> s2 -> s3                                                                |    |

| recognizes $cell0 \equiv < x soc, 0, 0 > . cell1$ and $cell2$ are recognized                                                                 |    |

| similarly                                                                                                                                    | 70 |

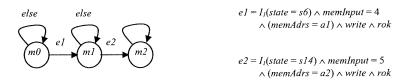

| Figure 5.3: IRS I <sub>5</sub> for the receiver/memory interface                                                                             | 71 |

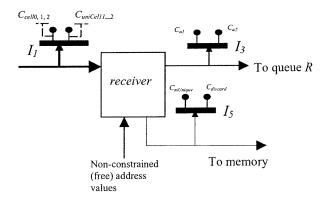

| Figure 5.4: Receiver subsystem. Constraints $C_{cell0}$ , $C_{cell1}$ , $C_{cell2}$ and $C_{uniCell1\_2}$                                    |    |

| are activated and (property) constraints C <sub>mUnique</sub> , C <sub>discard</sub> , C <sub>a1</sub> , and                                 |    |

| C <sub>a2</sub> , are checked.                                                                                                               | 73 |

| Figure 5.5: IRS I <sub>3</sub> for the receiver/queue R interface                                                                            | 74 |

| Figure 5.6: IRS I <sub>2</sub> for queueF/receiver interface                                                                                 | 75 |

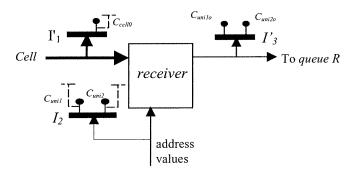

| Figure 5.7: IRS I' <sub>3</sub> to verify the address path                                                                                   | 75 |

| Figure 5.8: C <sub>cell0</sub> , C <sub>uni1</sub> , and C <sub>uni2</sub> , are activated and C <sub>uni10</sub> and C <sub>uni20</sub> are |    |

| checked to verify address path of the receiver                                                                                               | 76 |

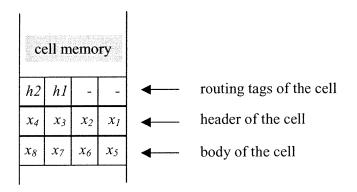

| <b>Figure 5.9</b> : Placement of a cell $< h1$ , h2, $x_1$ , $x_2$ , $x_3$ , $x_4$ , $x_5$ , $x_6$ , $x_7$ , $x_8 >$ in cell                 |    |

| memory                                                                                                                                       | 83 |

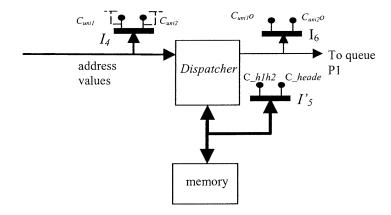

| Figure 5.10: Dispatcher verification. We verify that the headers of cells are                                                                |    |

| correctly updated in the memory                                                                                                              | 84 |

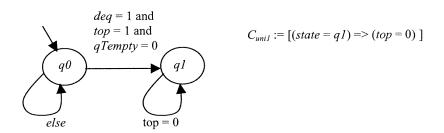

| Figure 5.11: An IRS for a data set reduced queue.                                                                                            | 86 |

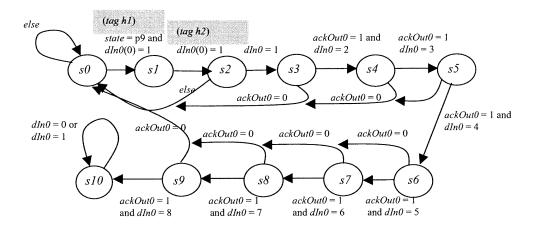

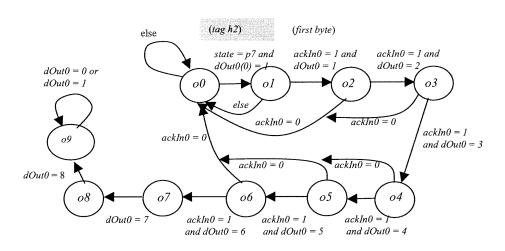

| Figure 5.12: IRS I <sub>10</sub> at the transmitter/fabric interface                                                                         | 87 |

| Figure 5.13: Timing diagram specification of the transmitter/fabric interface   |     |

|---------------------------------------------------------------------------------|-----|

| (Figure 5.1)                                                                    | 88  |

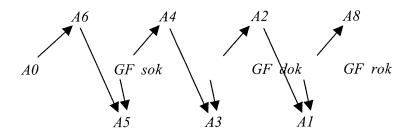

| Figure 5.14: Proof graph to discharge assumptions A1-A6                         | 94  |

| Figure 5.15: A proof graph for the in port controller global liveness           | 96  |

| Figure 5.16: Circular reasoning by induction over time. a) The rule. b) The     |     |

| proof graph                                                                     | 96  |

| Figure 5.17: IRS I <sub>11</sub> for the cells at the fabric/out port interface | 100 |

| Figure 5.18: The fabric subsystem for cell delivery property                    | 101 |

| Figure 5.19: Well-foundedness check for the compositional verification of       |     |

| the transmitter and the switch fabric                                           | 105 |

# Chapter 1

## Introduction

### 1.1 Motivation

Predesigned, preverified silicon building blocks or cores are finding increasing use in microelectronic system designs [50]. Examples of such cores or hardware intellectual properties (IP) are microprocessors, DSP, PCI, MPEG and JPEG cores. Integration of these application specific components into complex system-on-chip (SOC) designs is a new challenge for system-level designers. As the complexity and the density of ICs increase, verification becomes even more important than before. Traditionally, simulation has been used for design verification, but the increasing design complexity makes it very difficult, if not impossible, to create sufficient test vector sets. Even with partial vector sets, simulation usually takes too long for each iteration. International Technology Roadmap for Semiconductors (ITRS) [10] has identified test and verification of complex systems as the challenges of the system design in the next decade. ITRS has warned that these challenges are soon becoming crises. There are currently 2 to 3 times more verifications engineers than designers on microprocessor teams. Overall Cost of design threatens continuation of the semiconductor roadmap [10].

Formal verification may offer a viable approach to the verification of these complex systems. Instead of applying stimuli to a design and comparing its responses with expected results, formal verification tools examine a design and mathematically prove or disprove its functional properties. The huge effort needed to create functional test

vectors can be avoided except for those parts of the design where simulation is still necessary. Putting both methods together, a thorough verification can be achieved in a much shorter time than purely using simulation. Unlike nonexhaustive simulation, which only aims to show the presence of bugs, formal verification can prove their absence. When errors are found, formal verification tools can also generate counter examples to demonstrate the error conditions. Formal verification has become an essential technology for solving today's verification problems [48].

Most formal verification methods fall into one of two classes [31]; (1) proof based methods which use theorem provers, and (2) state-exploration methods which use model checkers to automatically search the state space of the design. Theorem provers use the full power of mathematics, so they are very flexible and can proof properties of entire classes of systems [31]. The main drawback of such methods is that they require a large amount of interaction from the users. In contrast, state-exploration methods restrict the model to be finite-state, and use state space search algorithms to check automatically that the specification is satisfied. The most serious drawback of the state-exploration methods is the state explosion problem [31]. This problem mostly arises in systems composed of multiple components operating in parallel. Composing finite state machines in parallel leads to an exponential explosion of states in the worst case, which imposes a strong limit on the size and complexity of systems that can be verified by state enumeration methods [14].

Two main techniques have been proposed to avoid state explosion problem [31]: (1) compositional verification and (2) abstraction. In compositional verification, the specification of the system is separated into properties of its components. Then, the properties of the components are separately verified. Finally, it is proven that the components specifications imply the specification of the entire system. In abstraction, the models are simplified by hiding details of the design. Then the simplified model is verified. Finally, a relation between the abstract model and the original one is established to assure that the correctness at the abstract level implies the correctness at the detailed or refined level.

Typically, a component works properly only in a given environment in the system. It is unlikely that the component satisfies any useful property in an arbitrary environment. This is called "the environment problem" [14]. In compositional verification, properties or abstract models of the other components constitute a constraining environment for verifying the given component.

The environment problem appears in a similar way when reusing IP cores in new applications. Given that the core works properly under specific environment assumptions, it is unlikely that it works in any arbitrary application. For a successful core reuse, a formalism is needed to specify these assumptions.

In this thesis, we study formal requirements for (reusable) component integration and propose a formalism for the specification of the properties and the environment assumptions of these cores. We use compositional verification methodologies to ensure correct integration of cores in systems.

Our objective is also to illustrate compositional reasoning on a relatively complex system. As a case study, we target telecommunication hardware systems. We study an asynchronous transfer mode (ATM) switch module that consists of port controllers and a switch fabric. ATM is a cell based switching and multiplexing technology designed to be a general purpose transfer mode for a wide range of services [52]. It is particularly well suited for the exchange and transfer of media intensive data such as real time audio, video, and high quality images.

The ATM switch includes a complex control path and handles large data structures like ATM cells. The switch is quite complex for current model checking tools, e.g., Formal Check [3], and consequently a compositional approach must be adapted for the overall verification. Although, there have been earlier efforts in the verification of switch fabrics [32], there is no published work on (the formal or informal) verification of port controllers. As data rates of networks increase and more services

are offered by network service providers, these port controllers are becoming more complex since they have to handle packets in a shorter time budget and with different qualities of service. For instance, with an OC-192 data link, the switch has a maximum time of 51 microseconds to read, convert the header, and route each ATM cell [26]. Becoming more complex, the switch module requires a parallel architecture to perform its functions. Currently, major semiconductor manufacturers are starting to sell a new type of integrated circuit, the network processors [26]. Network processors are programmable chips like general purpose microprocessors, but are optimized for packet processing required in network devices. This (network processor) industry is currently at its early stage. In this thesis, we implement a relatively simple switch module which (is not as complex as a network processor, however) performs basic operations, e.g., cell buffering, routing, header transformation, and cell prioritization. We aim to develop the following ideas:

- 1. If a switch fabric or a port controller is provided as an IP core, what would be the environment assumptions for each of them and which specification formalism can describe those assumptions?

- 2. Having specified the environment assumptions, what properties have to be specified for switch components? Although a set of well-defined, well-established properties is available for microprocessors, such a specification does not exist for port controllers of an ATM switch.

- 3. Having the assumptions and the properties, how could one verify a correct integration of switch components in an application? How could one show that each component satisfies the assumptions made by its neighbors?

### 1.2 Contributions

The principal contributions of this thesis are as follows:

- 1. We classify recent (and relatively poorly documented) compositional verification methods. In chapter 2, we describe assume guarantee reasoning implemented by theorem provers and non-circular and circular compositional verification methods implemented by state of the art model checkers.

- 2. We introduce interface recognizers/suppliers (IRS) as a practical mechanism to represent environment assumptions and interface properties of the components. IRS is a recognizer<sup>7</sup> augmented with a set of Boolean constraints. By forcing the constraints to be always true, IRS constrains its inputs. By checking the constraints of IRS, we verify that a component satisfies the specification modeled by the IRS. IRS can thus equally act as a recognizer of a property and as a supplier of assumptions on its inputs.

- 3. We extend the application of IRS from modeling environment assumptions to compositional verification. Given that the reasoning with IRS can be circular, we develop well-foundedness conditions to avoid erroneous conclusions.

- 4. We model an existing port controller and switch fabric modules of an ATM switch. (Port controllers are modeled in VHDL [9] and the fabric is translated from Verilog to VHDL. The controller and the fabric models are about 3500 and 500 lines of VHDL code respectively. (See Appendix 4.)) In a 4x4 setting, there are 4 in port controllers and one 4x4 switch fabric. This 4x4 model is about 14500 lines of VHDL code and includes 1500 state variables, which is far beyond the capacity of a commercial model checker. We use IRS to model environment assumptions of the switch fabric. Using the same IRS, we show that the in port controllers satisfy these assumptions. We also show that the fabric satisfies its properties when operating under the environment IRS.

- 5. We propose a specification and verification methodology for switch-type systems, e.g., for this class of network devices. We specify 5 properties for in port controllers

<sup>&</sup>lt;sup>7</sup> Recognizer is defined in Chapter 3.

and then use IRS to model and verify these properties. Due to the large complexity of ATM cells, we use the data-independence assumption and cell size reduction techniques to carry out successful verification.

We organize the thesis as follows: Chapter 2 introduces the mathematical notation needed to describe and classify compositional verification methods. Assume/guarantee reasoning and compositional model checking methods are also discussed there.

In Chapter 3, we propose interface recognizers/suppliers (IRS) as a means to specify environment assumptions and properties of (reusable) components.

Chapters 4 and 5 contain our case study: The ATM switch design is introduced and its properties are formally verified using the IRS methodology.

Chapter 6 presents conclusions and discusses possible extensions or improvements to the proposed compositional verification method.

The methodology proposed in this thesis has been published in [28][29][2]. We have also submitted a comprehensive article on the compositional reasoning using IRS to Formal methods in system design journal.

# Chapter 2

# Compositional verification rules

In this chapter, we present the computation models and the formal notation that are used to describe compositional verification rules. In particular, we represent the models that have been used in compositional verification of hardware systems.

**Definition 2.1** [31]: A Moore machine  $M = \langle S, Init, I, O, T, L \rangle$  is a tuple of the following form:

- 1. S is a finite set of states.

- 2.  $Init \subseteq S$  is a nonempty set of initial states.

- 3. *I* is a finite set of input propositions.

- 4. *O* is a finite set of output propositions.

- 5.  $T \subset S \times 2^{I} \times S$  is a transition relation.

- 6. L:  $S \rightarrow 2^{O}$  is a function that maps each state to the set of output propositions true in that state.

It is required that  $I \cap O = \emptyset$  and for every  $s \in S$  and  $v \subseteq I$ , there exists some  $t \in S$  such that T(s, v, t).

Moore machines that have disjoint sets of outputs can be composed in a natural way. The composition, for instance at the circuit level, corresponds to wiring outputs of one machine to the appropriate inputs of the other. Each machine receives some of its inputs from the other machine and some of its inputs from an environment. The next definition is a formal definition of the composition.

**Definition 2.2.** The composition of Moore machines  $M1 = \langle S_1, Init_1, I_1, O_1, T_1, L_1 \rangle$  and  $M2 = \langle S_2, Init_2, I_2, O_2, T_2, L_2 \rangle$  (denoted  $M1 \parallel M2$ ) is defined when  $O_{M1} \cap O_{M2} = \emptyset$  and it is the Moore machine M defined by:

- 1.  $S = S_1 \times S_2$ , where  $\times$  represents the Cartesian product. For instance,  $(s_1, s_2) \in S$  only if  $s_1 \in S_1$  and  $s_2 \in S_2$ .

- 2.  $Init = Init_1 \times Init_2$ .

- 3.  $I = (I_1 \cup I_2) (O_1 \cup O_2)$ .

- 4.  $O = O_1 \cup O_2$ .

- 5.  $T[(s_1, s_2), v, (s'_1, s'_2)]$  iff  $T_1[s_1, (v \cup L_2(s_2)) \cap I_1, s'_1]$  and  $T_2[s_2, (v \cup L_1(s_1)) \cap I_2, s'_2]$ .

- 6.  $L(s_1, s_2) = L(s_1) \cup L(s_2)$ .

This definition of  $M1 \parallel M2$  has the following properties:

- 1. Each machine must make a transition<sup>8</sup>, and

- 2. The inputs that each machine sees are the inputs from the overall environment plus the outputs from the other machine in the composition. Finally, the union of the outputs of the modules gives the outputs of the composed system. (It is possible to restrict the global outputs to a subset of this union, e.g.,  $O \subseteq O1 \cup O2$ . However, we have reported the original definition in [31].)

Kripke structures [41] are usually used in model checking of hardware systems. We study the relationship between Moore machines and Kripke structures. A Kripke structure  $M = \langle S, Init, T, A, L \rangle$  is defined as follows [31]:

- 1. S is a finite set of states.

- 2.  $Init \subseteq S$  is a nonempty set of initial states.

<sup>&</sup>lt;sup>8</sup> In this thesis, we have only assumed synchronous hardware systems.

- $3.T \subseteq S \times S$  is a transition relation.

- 4. A is a finite set of atomic propositions.

- 5. L is a function that maps each state to the set of output propositions true in that state.

A Kripke structure or structure for short does not distinguish inputs from outputs. Moore machines, on the other hand explicitly define inputs to interact with their environments. By incorporating inputs of a Moore machine to its states, it is possible to obtain the corresponding Kripke structure. Figure 2.1 shows a machine M and the corresponding structure struct(M).

Figure 2.1: a) A Moore machine M and b) the corresponding structure struct(M) [31]

Next, we review a temporal logic that is commonly used for property specification in the literature. Temporal logic is a logical language used in the formal verification of concurrent systems. We will use standard linear temporal logic (LTL) [51]to reason about the composition of properties in Chapter 5. A model for an LTL formula is an infinite sequence  $s_0$ ,  $s_1$ , ... of states, representing consecutive time instants. A formula is either an atomic proposition or one of  $\neg p$ ,  $p \land q$ ,  $p \lor q$ , where p and q are formulas. " $\neg$ " and " $\wedge$ " represent propositional operators *not* and *and*, respectively. The Until operator "U" and the Next operator "X" are defined as follows:

Each formula is either true or false in a given state.

We use the notation  $(M, s_i) \models p$  to indicate that M satisfies p at the ith state, i.e.,  $s_i$ .

- 1.  $(M, s_i) \models \neg p \text{ iff } (M, s_i) \not\models p$ .

- 2.  $(M, s_i) \models p \land q \text{ iff } (M, s_i) \models p \text{ and } (M, s_i) \models q.$

- 3. (M,  $s_i$ )  $\models p \cup q$  iff (M,  $s_i$ )  $\models q$  or there exists j > i such that (M,  $s_j$ )  $\models q$ , and for all  $i \le k < j$ , (M,  $s_k$ )  $\models p$ .

- 4.  $(M, s_i) \models Xp \text{ iff } (M, s_{i+1}) \models p$ .

The formula F p (eventually p) is an abbreviation to (true U p) and it predicts the eventual occurrence of p becoming true. G p (globally p) is equivalent to  $\neg F \neg p$  indicating that p is true from now on.

We will use finite state automata to specify interface behaviors. A finite state automaton (FA) is a 5-tuple (S, Init, A, T, F), where [30]

- 1. S is a finite set of states.

- 2.  $Init \in S$  is a start state.

- 3. A is a finite set called the alphabet.

- 4.  $T: S \times A \rightarrow S$  is the transition function.

- 5.  $F \subseteq S$  is the set of accepting (or final) states.

The input alphabet contains the allowed input symbols. If the automaton receives an allowed input symbol a in a state s, it moves to the next state indicated by the transition function T. When a machine accepts a string, it ends up in an accepting state. If L is the set of strings that machine M accepts, we say that L is the "language" of machine M [30].

A finite state machine (FSM) is a model similar to FA. An FSM generates outputs in each state of the machine. (In contrast to FA, outputs rather than final states are considered and emphasized for FSMs.) The outputs are determined from the current

state and the inputs of the machine [5]. When the output values depend only on the state of the FSM, we get a Moore machine (Definition 2.1).

FSMs can model synchronous circuits. Suppose a machine M implements a property p under the environment assumptions e. This is denoted by [4]

$$\langle e \rangle M \langle p \rangle \tag{2.1}$$

The environment assumptions e can be supplied as a set of linear temporal logic formulas, or equivalently by an FSM E that models these temporal formulas. (However, to model eventuality formulas, fairness assumptions sould be added to these FSMs.) In [6] a practical method called tableau construction is proposed to build a maximal model for a given temporal logic formula. The tableau or the maximal model is the one that can simulate all the models that satisfy the formula<sup>9</sup>. We denote TBL(p), the tableau for a formula p. Assertion (2.1) can then be implemented using model checking algorithms. For instance, one can verify that

$$\mathbf{E} \parallel \mathbf{M} \models p \tag{2.2}$$

Equivalently, it can be verified that the composed machine E||M| can be simulated by the machine TBL(p) [6]

$$E||M \le TBL(p) \tag{2.3}$$

Assertion (2.1) can also be implemented using deduction-based algorithms, i.e, theorem prover systems. The formulas are expressed with first order or higher order logics and they get an explicit time parameter t. For instance, (2.1) is implemented as:

$$\forall t. \ e(t) \Rightarrow (M(t) \Rightarrow p(t)) \tag{2.4}$$

<sup>&</sup>lt;sup>9</sup> The simulation relation is defined in Appendix 2.

Having defined computational models, we proceed to study compositional verifications methods.

### 2.1 Assume guarantee reasoning (A/G)

Abadi and Lamport [22] presented an assume guarantee formalism for the specification of open systems, i.e., the systems that interact with their environment. Suppose that the specification of a component M is represented with an assume guarantee (A/G) specification  $e^{-} \rightarrow p$ , where p specifies the component commitments and e describes its environment assumptions. This A/G specification asserts that M maintains its commitments p if the environment satisfies the specification e. (More precisely, formula  $e^{-} \rightarrow p$  asserts that (for all i,) p is true up to point i of the computation if e holds up to point j < i. This means that p holds at least one step more than e does. The formula  $e \Rightarrow p$  is weaker than  $e^{-} \rightarrow p$  in that it only asserts that p holds as long as e holds.)

Lamport [23] states the principles of the composition as follow. Suppose a system M is composed of components  $M_1, ..., M_n$ . Each component guarantees its specification under a specific environment assumption. If the following conditions are met, then the principles of the composition infer that the global system M guarantees the global specification p under the global environment assumption e. These conditions are:

- 1- Every component  $M_j$  guarantees its specification  $p_j$  under the environment assumption  $e_j$ . ( $e_j \xrightarrow{+} p_j$ , for  $0 \le j \le n$ )

- 2- The environment assumption  $e_j$  of each component is satisfied under the global assumption e and the inout properties of all components. That is  $(e \wedge p_1 \wedge ... \wedge p_n \Rightarrow e_j)$ , for  $0 \leq j \leq n$ .

- 3- M guarantees p if each component  $M_j$  guarantees  $p_j$ . This means that the global system specification p is implied by the component properties  $p_j$ , i.e.,

$$(e \wedge p_1 \wedge \ldots \wedge p_n \Rightarrow p).$$

A composition rule based on the composition principles has been implemented in a special linear temporal logic, called TLA [21]. TLA uses a theorem proving approach. Conditions (1) to (3) of the composition are manually verified using a proof assistant. However, Lamport and Kurshan [33] presented a hybrid approach to compute Steps (2) and (3) of the rule by a theorem prover, and Step (1) by a model checker.

The composition rule, as expressed in TLA can be applied only to safety properties [15]. A safety property holds in all states of a model. Safety properties assert that bad things "never" happen. A liveness property on the other hand talks about eventual occurrences of events. For example, a liveness property in a communication protocol can be as follows: if a good message is sent by the transmitter, it is eventually received by the receiver.

In the next section, we review the compositional methods which use model checking algorithms (rather than deduction-based reasoning) to implement compositional verification. We also discuss whether each method can prove liveness properties in addition to the safety ones.

### 2.2 Compositional verification

The recent developments in the compositional verification (CV) originated from the assume guarantee (A/G) reasoning<sup>10</sup>. Although very similar, the major difference is in the way they treat the environment model. In A/G approaches, the environment assumptions are stated explicitly, from the beginning, with the component specifications. (That is what we wish to require for the specifications of reusable components.) In compositional verification methods, the environment assumptions do

<sup>&</sup>lt;sup>10</sup> These compositional approaches attempted to implement structural induction by using model checking algorithms [31][14]. A more complete survey of compositional methods, e.g., the methods that generally infer system properties from component properties can be found in COMPOS97 proceedings [49]

not explicitly exist. They are subsequently obtained by the abstract models of the components of the system, surrounding a given module. These so obtained environment assumptions create an abstract context for the verification of the component(s). It is thus verified that the component satisfies its properties in the abstract environment.

#### 2.2.1 Non circular compositional verification

Pnueli [4] presented an assume guarantee rule for the temporal logic model checking. The rule states that if a module M1 satisfies a property  $p_1$  and then assuming this formula, a module M2 satisfies a property  $p_2$ , then the system  $M1 \parallel M2$  satisfies the property  $p_2$ .

$$<> M1 < p_1> (2.5_1)$$

$< p_1> M2 < p_2> (2.5_2)$

$<> M1 // M2 < p_2>$

In the rule,  $(2.5\_1)$  discharges property  $p_1$  which is assumed in  $(2.5\_2)$ . This kind of reasoning has been implemented in model checkers such as SMV [16]. When the properties  $p_1$  and  $p_2$  are known, this rule provides the benefit that direct reasoning about the composed system M1 // M2 is avoided. In practice, nevertheless, determining such properties may be highly non-trivial [20].

### 2.2.2 Circular compositional verification

The inference rule (2.5) presented in Section 2.3.1 is not circular. The first subgoal of the rule states that M1 satisfies  $p_1$  without any further assumption. Generally, this is not the case and M1 may make certain assumption  $p_2$  about M2 in order to maintain  $p_1$ . The rule thus becomes circular. M1 satisfies  $p_1$  if M2 satisfies  $p_2$  and vice-versa, M2 satisfies  $p_2$  if M1 satisfies  $p_1$ . From propositional logic point of view, this circular reasoning may conclude wrong results. One cannot deduce  $p_1 \wedge p_2$  from  $p_1 \Rightarrow p_2$  and  $p_2 \Rightarrow p_1$ . For instance, both predicates  $p_1$  and  $p_2$  may be false and yet  $p_1 \Rightarrow p_2$  and

$p_2 \Rightarrow p_1$  are true. We illustrate this by an example.

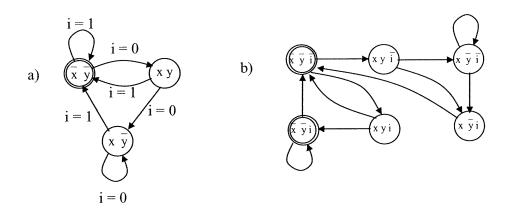

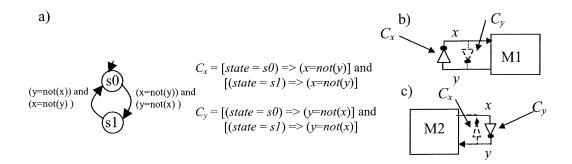

**Example 2.1** (*cycle-of-gates*) Consider a cycle of NOT gates NI and N2 in Figure 2.2a. Let  $p_1 := (i = 0)$  and  $p_2 := (o = 1)$ . Under the assumption G  $p_1$ , i.e., G (i = 0), NI satisfies G  $p_2$ , i.e., G (o = 1). Similarly, assuming G (o = 1), N2 satisfies G (i = 0). However, the conclusion  $G(i = 0) \wedge G(o = 1)$  in  $NI \parallel N2$  is wrong, since we may have G  $(i = 1) \wedge G(o = 0)$ .

$$<> N1 < G [(i = 0) \Rightarrow (o = 1)] > (2.6_1)$$

$<> N2 < G [(o = 1) \Rightarrow (i = 0)] > (2.6_2)$

$<> N1 || N2 < G (i = 0) \land G (o = 1) >$  {wrong conclusion}

If there is at least one unit time delay<sup>11</sup> in the cycle, the conclusion is valid, however, based on induction in time [14]. Let X represent the next state operator of linear temporal logic. We have added a register in Figure 2.2b and the following reasoning is then sound.

Figure 2.2: a) Cycle-of-gates. (b) The cycle is broken by a register

$$<> NI < G [(i = 0) \Rightarrow (o = 1)] > (2.7_1)$$

$<> R2 < G [(o = 1) \Rightarrow X (i = 0)] > (2.7_2)$

$<> R2 < (i = 0) > (2.7_3)$

$<> NI \parallel R2 < G (i = 0) \land G (o = 1) >$

Subgoal (2.7\_3) in (2.7) asserts that R2 satisfies (i=0) in the initial state. Let  $p_I(\tau)$  denote that  $p_I := (i = 0)$  holds true at time  $\tau$ . Let  $p_2 := (o = 1)$ .  $p_I(0)$  holds true by (2.7\_3).  $p_2(0)$  holds true by (2.7\_1) at the output of NI which is the input to R2. If  $p_2$  holds true at the input of (register) R2 at the current time, then  $p_I$  holds true at its output at the next time, by definition of register R2. Hence, by  $p_2(0)$ ,  $p_I(1)$  holds true at R2 output (which is the input to NI). Continuing this way,  $p_I$  and  $p_2$  hold at all times, i.e., G  $p_I \wedge$  G  $p_2$ . We represent this inductive reasoning by the following general rule:

$$\forall t. \ p_{1}(t) \Rightarrow p_{2}(t) \qquad (2.8\_1) \qquad \Leftrightarrow MI < G \ [p_{1} \Rightarrow p_{2}] >$$

$$\forall t. \ p_{2}(t) \Rightarrow p_{1}(t+1) \quad (2.8\_2) \qquad \Leftrightarrow M2 < G \ [p_{2} \Rightarrow X \ p_{1}] >$$

$$p_{1}(0) \qquad (2.8\_3) \qquad \Leftrightarrow M2 < p_{1} >$$

$$\cdots \qquad (2.8a) \qquad (2.8b)$$

$$\forall t. \ p_{1}(t) \land p_{2}(t) \qquad \Leftrightarrow M1 \ || \ M2 < G \ (p_{1} \land p_{2}) >$$

Rule (2.8b) implements (2.8a) using temporal logic operators.

McMillan [14] proposed the following rule to implement compositional model checking. Let  $p|^{\tau}$  denote that p holds up to (including) time  $t = \tau$ .

$$p_{1}|^{\tau} \Rightarrow p_{2}(\tau) \qquad (2.9\_1)$$

$$p_{2}|^{(\tau - I)} \Rightarrow p_{I}(\tau) \qquad (2.9\_2)$$

$$\cdots \qquad (2.9)$$

$$\forall t. \ p_{I}(t) \land p_{2}(t)$$

This rule is also sound based on induction on  $\tau$ . When evaluated at time [14], (2.9\_2) asserts that  $p_I(0)$  holds true. Let  $p_1|^0 = p_I(0)$ . Then,  $p_2(0)$  holds by (2.10\_1),  $p_I(1)$  holds by (2.10\_2) and so on.

<sup>&</sup>lt;sup>11</sup> In this thesis, we have considered synchronous haradware systems. Gates have no delay and

Rule (2.9) replaces subgoals (2.8\_2) and (2.8\_3) with one subgoal (2.9\_2). Moreover, (2.9\_1) and (2.9\_2) can be verified using linear temporal logic formulas [15]. For instance, we (reproduce a proof to) show that  $p_2|^{(\tau - l)} \Rightarrow p_1(\tau)$  can be computed by  $\neg (p_2 \cup \neg p_1)$ . By definition, a module M satisfies  $(p_2 \cup p_1)$ , if  $p_1$  holds true at the initial state or if there exists a state  $s_j$  in which M satisfies  $p_1$  and in all states  $s_k$  before  $s_j$ , M satisfies  $p_2$ .

$$p_1(0) \vee [(\exists j > 0). \ (\forall (0 \le k \le j). \ s_k \models p_2) \wedge s_j \models p_1]$$

(2.10)

For  $(p_2 \cup \neg p_1)$ , this definition becomes:

$$\neg p_1(0) \lor [(\exists j > 0). \ (\forall (0 \le k < j). \ s_k \models p_2) \land s_j \models \neg p_I]$$

(2.11)

By negating (2.11), i.e.,  $\neg (p_1 \cup \neg p_2)$ , we obtain the following expression. ( Note that  $\neg [(\exists j>0). Q(j)] \equiv [(\forall j>0). \neg Q(j)].$ )

$$p_1(0) \wedge [(\forall j > 0). \quad \neg(\forall (0 \le k < j). \ s_k \models p_2) \vee s_j \models p_1]$$

or (2.12)

$$p_1(0) \wedge [(\forall j > 0). \ (\forall (0 \le k < j). \ s_k \models p_2) => s_j \models p_1]$$

(2.13)

A module satisfies  $p_2|^{(\tau-1)} => p_1(\tau)$  if it satisfies  $p_1$  in the initial state and (for all j) when module satisfies  $p_2$  up to (and including) state  $s_{j-1}$ , then it satisfies  $p_1$  at state  $s_j$ .

$$p_1(0) \wedge [(\forall j > 0). \ (\forall (0 \le k < j). \ s_k | = p_2) \Rightarrow s_j | = p_1]$$

(2.14)

That is,

$$[p_2|^{(\tau - I)} \Rightarrow p_1(\tau)] \equiv [\neg (p_2 \cup \neg p_I)]$$

(2.15)

Now, we show that  $p_1|^{\tau} \Rightarrow p_2(\tau)$  can be computed by  $\neg (p_1 \cup (\neg p_2 \land p_1))$ . By definition, we have that

$$[p_I]^{\tau} \Rightarrow p_2(\tau) \equiv [(p_I|^{(\tau I)} \land p_1(\tau)) \Rightarrow p_2(\tau)] \tag{2.16}$$

Using the relation  $[(p \land q) \Rightarrow r] \equiv [p \Rightarrow (q \Rightarrow r)]$ , we get

$$[p_{I}|^{\tau} \Rightarrow p_{2}(\tau)] \equiv [(p_{I}|^{(\tau - I)} \land p_{1}(\tau)) \Rightarrow p_{2}(\tau)]$$

$$\equiv [p_{I}|^{(\tau - I)} \Rightarrow (p_{1}(\tau) \Rightarrow p_{2}(\tau))]$$

$$\equiv [p_{I}|^{(\tau - I)} \Rightarrow (\neg p_{1}(\tau) \lor p_{2}(\tau))]$$

(2.17)

Rewriting (2.17) using (2.15) gives the following result:

$$[p_{I}|^{\tau} \Rightarrow p_{2}(\tau)] \equiv [\neg (p_{I} \cup \neg (\neg p_{I} \vee p_{2}))]$$

$$\equiv [\neg (p_{I} \cup (p_{I} \wedge \neg p_{2}))] \qquad (2.18)$$

Using (2.15) and (2.18), the circular model checking rule (2.9) is computed by checking the following two temporal logic formulas on M1 and on M2.

In summary, we conclude that if there is no cycle-of-gates in the system, i.e., every cycle is cut by at least one unit delay, the circular reasoning is sound, based on the induction over time introduced by the delay element.

Note that  $p_1$  and  $p_2$  can represent safety and liveness properties. Rule (2.19) (unlike other approaches) can then be used to prove liveness properties. We will use (2.8b)

(which is our approximation of (2.19)) to prove a liveness property of an ATM switch in Chapter 5. In Appendix 2, we prove that  $(2.8b) \Rightarrow (2.19)$ , i.e., (2.8a) is a conservative approach to (2.19).

Next, we review the assume guarantee reasoning in reactive modules [35]. With reactive modules, the specifications of components are not described using temporal logic formulas. Instead, the specification is a higher-level design of the component, thus another reactive module. This framework uses trace-containment relation to show that a component implements a specification.

#### 2.2.3 Reactive modules [35]

A reactive module M (or module M, for short) has a finite set of variables, denoted  $V_M$ . A "state" of M is a valuation for  $V_M$ . The module represents a system that interacts with an environment.  $V_M$  is partitioned into three sets; input variables I, output variables O, and privates variables P. While O and P are updated by M, I is updated by the environment. M contains two predicates to assign values to the variables in  $O \cup P$ ; an initial action that assigns initial values to  $O \cup P$ , and an update action that assigns updated values to them. For every state  $O \cup P$ , and for every valuation of I, there exists a finite number of next states for  $O \cup P$ , and an update predicate is always executable, and the system is prepared to respond to all possible environment moves. M does not constrain the behavior of I variables and thus interacts with the environment in a nonblocking way.

A module M consists of one or more atoms that control  $(O \cup P)$  variables of the module. Each atom controls one or more variable, however, every variable is controlled by one and only one atom. Let  $X_a$  be a finite set of variables of an atom a.  $X_a$  contains three sets of variables; a set of controlled variables  $ctrX_a \subseteq X_a$ , a set of read variables  $readX_a \subseteq X_a$ , and a set of awaited variables  $waitX_a \subseteq \{X_a \setminus ctrX_a\}$ . A controlled variable of an atom may depend sequentially on a read variable of the atom, much like a register output that depends on register input. A controlled variable

y of an atom may depend combinationally on an awaited variable x of the atom. This is denoted  $x <_a y$  to indicate that atom a can update y only after x has been updated.

A module M consists of its atoms which have the following properties. (1) Controlled variables of atoms are disjoint, i.e., for every atom a and b of M,  $ctrX_a \cap ctrX_b = \emptyset$ . (2) The set  $(O\ U\ P)$  of M equals the set  $(U_{a \in atoms}\ ctrX_a)$  of the atoms. (3) The transitive closure of  $<_{\rm M} = (U_{a \in atoms}\ <_a)^+$  is asymmetric. The third condition ensures that the await dependencies among the variables of M are acyclic, and consequently, there exists a consistent ordering for updating all atoms of M [35].

The execution of a module results in a trace of observation. For two states s and t of M, the state t is a successor of s if t can be obtained from s, by executing updating actions of M. A trajectory of M is a finite sequence  $s_0...s_n$  of states such that (1)  $s_0$  is an initial state and (2) for all  $0 \le i < n$ , the state  $s_{i+1}$  is a successor of  $s_i$ . If s is a valuation to variables  $V_M$  of M and  $W \subseteq V_M$ , then  $[s]_W$  denotes the valuation restricted to W. Let IO denote the variables in  $(I_M \cup O_M)$ . If  $s = s_0...s_n$  is a trajectory of M, then its projection sequence  $[s]_{IO} = [s_0]_{IO}...[s_n]_{IO}$  is a trace of M. The trace language  $L_M$  of M is the set of traces of M.

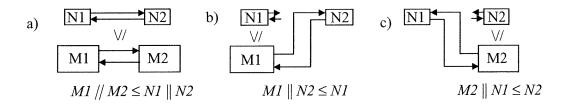

A module M implements a module N, written  $M \le N$ , if the following conditions are met: (1)  $O_N \subseteq O_M$ ;(2) $I_N \subseteq (I_M \cup O_M)$ ; (3) for  $\forall x \in (I_N \cup O_N)$  and  $\forall y \in (O_N)$  such that we have  $x <_N y$ , then  $x <_M y$ ; and (4) if s is trace of M, then the projection  $[s]_{IO}$  is a trace of N, where  $IO = (I_N \cup O_N)$ .

Two modules M1 and M2 are "compatible" if (1)  $O_{M1} \cap O_{M2} = \emptyset$ , and (2) the transitive closure ( $<_{M1} \cup <_{M2}$ )+ is asymmetric, i.e., the await dependencies among IO variables of M1 and M2 are acyclic.

If M1 and M2 are two compatible modules, then the composition M1 // M2 is the module with  $P_{(M1 \parallel M2)} = P_{M1} \cup P_{M2}$ ,  $O_{(M1 \parallel M2)} = O_{M1} \cup O_{M2}$ ,  $I_{(M1 \parallel M2)} = I_{M1} \cup I_{M2} \setminus O_{(M1 \parallel M2)}$ , and  $Atoms_{(M1 \parallel M2)} = Atoms_{M1} \cup Atoms_{M2}$ .

**Assume guarantee** [35]: Let M1 and M2 be two compatible modules, and let N1 and N2 be two compatible modules such that  $I_{(NI \parallel N2)} \subseteq IO_{(M1 \parallel M2)}$ . If  $M1 \parallel N2 \le N1$  and  $M2 \parallel N1 \le N2$ , then  $M1 \parallel M2 \le N1 \parallel N2$ .

The steps of the assume guarantee rule are illustrated in Figure 2.3. The proof of the rule, based on induction on the trace length is given in Appendix 1.

Figure 2.3: The assume guarantee rule. Steps b) and c) prove a)

## 2.3 Summary

We have presented recent works in assume guarantee (A/G) reasoning and its descendant, compositional model checking (CMC). In the original A/G reasoning [22], the environment assumptions of the modules are explicitly stated, a priori along the component specification. In this way, a closed system, (i.e., the component and its environment assumptions) is specified, as the specification of each component. In CMC approaches, the environment assumptions do not explicitly exist. However, an abstract environment is obtained by the properties or abstract models of the components of the system, surrounding a given module. These so obtained assumptions create an abstract context for the verification of components. If we want to apply compositional verification methods to designs constructed using reusable

components (e.g., intellectual property (IP) blocks), the environment assumptions of these components must be supplied with the component specification so that the components could be safely used in any application.

The following classification represents the works reviewed in this chapter.

- 1. (Non-circular compositional model checking) Long [31] presented a composition rule that non-circularly verifies a composed system using model checking algorithms. For instance, it is first verified that a component satisfies its properties under certain assumptions. It is then verified that the other components of the system satisfy those assumptions, without any assumption about the first component. Long showed how to transform a temporal logic formula to a Kripke structure so that to compose components with formulas. This composition allowed the assumtion/guarantee be implemented using model checking systems. This framework supports both safety and liveness property verifications.

- 2. (Assume guarantee reasoning) Abadi and Lamport [22] assuming an interleaving model of concurrency, proposed a circular compositional rule to verify safety properties of the composed systems. The rule is originally implemented by theorem provers and supports only safety properties.

- 3. (Assume guarantee with synchronous communications) Alur and Henzinger [35] extended the interleaving unit-delay model of the components in [22] to synchronous Mealy machines. These machines may contain zero-delay communication from machine inputs to machine outputs. This framework imposes a well-foundedness condition that there must be no-cycle-of-gates in the composed Mealy machines. This method supports only safety properties.

- 4. (Cicular compositional model checking) McMillan [14][15][17][19] contributed in two ways to the compositional model checking literature. First, he relaxed the condition that only one component (or one atom) constrain any output of the system.

To resolve the conflicts, he introduced a refinement relation among those modules that constrain one output [14]. Second, he introduced an inductive rule and verified liveness properties of composed systems, in addition to the safety properties.

Compositional methods use abstract models of the components, either in the form of temporal properties or in the form of higher-level designs to compute subgoals of the composition rule efficiently. A rule is efficient if the abstract models are logically sufficient to carry out the proof obligations. However, when either of them is not strong enough, the rule cannot yield the desired results. The abstractions constitute both the strength and the weakness of the methods. They make the computation efficient. But in practice the problem remains how to obtain the appropriate abstract models.

In the next chapter, we propose a compositional rule based on the interactions observed at the interfaces of components. This method uses interface interactions as the formalism of the specification and abstraction. We present interface recognizers/suppliers (IRS) which enable us to symmetrically verify a property or supply an assumption on components inputs. IRS can be used to organize an end-to-end verification of modular systems.

# Chapter 3

# Constraints in model checking

In chapter 2, we mentioned that during model checking, environment assumptions of components could be provided as temporal logic formulas. Industrial model checkers, e.g., Formal Check [3] or Verdict [25] have mechanisms to specify these as verification constraints. In this chapter, we study the requirements that the constraints and the components must satisfy so that the reasoning about them is valid. We then present a methodology based on interface recognizers/suppliers (IRS) to implement constrained model checking. We propose a composition rule and discuss its well-foundedness.

## 3.1 Constrained model checking

Developing environment models during formal verification of components in modular systems is a time-consuming and error-prone activity. Kaufmann et al. [25] suggest using "constraints" as a simple way to model the environment. A constraint is a Boolean formula involving any signals in the design. Constraints appear at three levels of granularity: (1) At the first level, they involve only input signals of the component. Suppose A and B are inputs of a module M. Then, \$constraint[ $\neg(A \land B)$ ] specifies a constraint in Verdict [25] that restricts the inputs of M so as to always satisfy  $\neg(A \land B)$ . (2) At the second level, constraints may also depend on the internal state of the design. For instance, \$constraint[(state =  $s_1$ ) =>  $(A \lor B)$ ] defines a constraint that depends on state  $s_1$  of M. Implicitly, it is assumed that the design by itself contains the information necessary to determine what its (next) input should be. Consequently, the inputs of the design are combinationally computed from the state

information of the design. (3) At the third level, the inputs may depend not only on the current state of the design but also on the history of reactions of the design to its inputs. In this case, a finite state machine called "monitor" is defined to watch and record the information needed to determine the next inputs to the design. With the addition of the monitors, constraints become as expressive as environment models [25].

Constrained model checking performs reachability analysis over those computations that globally satisfy the constraints. (A computation path is an infinite sequence of states [37].) It has to be ensured that (1) this state space is not empty, i.e., the design has at least one initial state that satisfies the constraints. It also has to be ensured that (2) the constrained model does not contain any "dead-end" state, i.e., every reachable state of the constrained model should have at least one successor state that satisfies the constraint (a dead-end state is a reachable state that does not have a next state that satisfies the constraints [25]). Although traditional hardware modules satisfy these conditions, no-dead-end condition may fail in the presence of constraints. These conditions can be verified using temporal logic model checking. Suppose  $(M, s_{\theta})$ AG p indicates that a property p holds true in all states of all computation paths starting from  $s_0$ . Similarly,  $(M, s_0) \models EG p$  asserts that there exists a computation path on which all states satisfy p. Let C denote a constraint, e.g., a Boolean formula. Suppose that M satisfies C in some initial state  $s\theta$ , i.e.,  $(M, s\theta) \models C$ . Suppose that assuming M satisfies C in the current state, we can prove that there exists some next state that satisfies C, i.e.,  $(M, s\theta) \models AG(C \Rightarrow EXC)$ . Then, M composed with C does not have any dead-end state. It is also said that the constrained model  $M_C$  of M is "model checkable" [25].

The semantics of the constrained model checking is defined as follows [25]. Let S be a set, and R be a binary relation. Let Img(S, R) denote the image of S by R, i.e.,  $\{s' \mid \exists s \in S. \ R(s, s')\}$ . Consider a Kripke structure M with states S, transition relation T, and initial states Init. Let C be a Boolean constraint over S and the signals of the design. Let  $CInit \neq \emptyset$  be the initial states of M that satisfy C. States CS of  $M_C$  are

obtained from S by restricting the reachable states of M to the states that respect C. In terms of the fix point computations, CS is the least fix point of the following monotone functional F [25].

$$F(Y) = CInit \cup C(Img(Y, T))$$

,

where C(Z) represents the set of states in Z that satisfy C. CS is the least set Y of states containing Cinit such that for every  $(s, s') \in T$ , for which  $s \in Y$  and s' satisfies  $C, s' \in Y$ .

## 3.2 Assume guarantee in constrained model checking

Let a constraint C be a simple propositional logic formula, i.e., free of temporal logic operators (G, F, X, U). Suppose that a model M satisfies a property p under constraint C. This is denoted

$$\langle GC \rangle M \langle p \rangle$$

,

where G represents the "global" operator of temporal logic. M preserves p whenever it works in an environment E that satisfies GC. Therefore, there is an obligation to prove that the environment E satisfies GC. However, the verification that E satisfies GC may fail, since E may in turn make some assumption about its inputs from M. Kuafmann et al. [25] suggested to verify that  $E \parallel M$  satisfies GC (Figure 3.1b). However, when the state space of  $E \parallel M$  becomes larger than the capacity of the model checker, this subgoal is informally verified by a simulation. For instance, it is verified that the constraint is not violated in  $E \parallel M$  during simulation. In Section 3.4, we show that by abstracting the component it is possible to formally discharge the environment assumptions using a less complex subsystem.

Figure 3.1: Assume guarantee reasoning in constrained model checking.

- a) Module M under constraint GC satisfies property p.

- b)  $E \parallel M$  discharges assumption GC.

Monitors can be added to the design to provide history variables for constraint definition. This type of verification is reviewed in the next section.

## 3.3 Constrained model checking with monitors

The inputs of a design may depend on the current state of the design as well as on the history of interactions that occurred between the module and its environment. In this case, a finite state machine called monitor is defined to record such information. A monitor has multiple inputs and one output [25]. It watches the inputs to ensure that they are behaving as expected. It could monitor, for instance, that the interactions follow a given protocol.

Monitors like auxiliary variables [19] may provide extra signals for constraint definitions. The output of a monitor can be used in a constraint to form a "sequential" constraint (Figure 3.2a). Similarly, the same monitor can be used when discharging the constraint (Figure 3.2b). However, the system  $E \parallel M$  may become very complex. Then, M should be abstracted away from this verification. We study this kind of verification in the next section in the context of constrained model checking using interface recognizers/suppliers.

**Figure 3.2**: Constrained model checking using monitors. a)  $< GC > M \parallel Monitor$ . b)  $<> E \parallel M \parallel Monitor < GC >$ .

## 3.4. Interface recognizer/suppliers

We extend assume guarantee reasoning in constrained model checking in two ways. First, we propose an interface-based verification methodology, assuming that the internal states of the components are not accessible (or visible) to the environment. This is the case, for instance, when the state information of the design is not provided. In that case, whenever a sequential property (of the interface) is concerned, the use of monitors becomes inevitable. We provide a tighter connection between monitors and the constraints by using recognizers. Moreover, we make an abstraction of the component when discharging the environment assumptions. This second abstraction makes the methodology symmetric, i.e., the environment is abstracted (using the constraints) to model check the component and the component is abstracted (using the constraints) to model check the environment. This circular reasoning is not sound in general. We must avoid propositional circularity, by implementing an appropriate framework within the compositional model checking methodologies presented in Chapter 2.

Before presenting the formal foundation of the methodology, we give an example to introduce interface recognizers/suppliers (IRS).

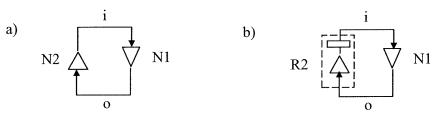

**Example 3.1** (Interface recognizers/suppliers) Suppose we want to design a generator to produce pulses of unit length on signal f such that they are at least 5 clock cycles apart (Figure 3.3a). A recognizer can be developed for the generator (Figure 3.5b). The recognition is encoded by a set of constraints in each state of the recognizer. For instance, consider the automaton in Figure 3.3b that recognizes the sequences that could be produced by the pulse generator. The signal f can be zero or one in state s1. After becoming 1 in s1, f becomes zero in s2. In s3, the recognizer uses a counter that counts modulo 5. f should remain zero in s3 until state s1 is reached. Note that if f gets a value other than the ones specified in the specification (in Figure 3.3a), the recognizer will not change its state.

Figure 3.3: A recognizer for the pulse generator f. a) Specification. b) The recognizer. The "variable" count is zero in state s1, one in state s2, and is incremented in state s3 until reaching 5.

We define a Boolean signal  $C_f$  to monitor f:

$$C_f := [((state = s2) \text{ or } (state = s3)) \Rightarrow (f = 0)]$$

$$(3.1)$$

$C_f = true$  asserts that f is zero in states s2 and s3 of the recognizer. (Note that it does not assert that s2 and s3 are ever reached. In fact, if s2 and s3 are not reached, then  $C_f$  = true will still hold.)  $C_f = false$  asserts that f is not zero in either of those states.  $C_f$  acts like an acceptance condition of the recognizer R such that, when always true, it verifies that the generator F respects the unit cycle as well as the 5 clock-cycle period constraints on f. Figure 3.4a shows the generator F and the recognizer R. Suppose we verify the recognizer (without using the generator) with a model checker like Formal Check [3] and we set a constraint that  $C_f$  be always true (Figure 3.4b).  $C_f = true$  is a constraint of the recognizer which observes the primary input signal f. By forcing

$C_f = true$ , the model checker must supply only those combinations of f which respect the constraint  $C_f = true$ . The net result is that f can be 1 (or 0) at state s1 and 0 at states s2 and s3, thus generating exactly the pulses required by the specification. In this way, R supplies constraints on its primary input f. This input-shaping feature of the recognizer enables us to produce almost any signal characterized by the constraints of the recognizer using any model checker. In this configuration, the recognizer forms a supplier, i.e., it supplies constraints or assumptions on the (otherwise free) inputs. This type of a recognizers that is augmented by Boolean constraints is called an "interface recognizer/supplier" (IRS).

Figure 3.4: Interface recognizer/supplier.

a) Recognizer R for pulse generator F. b) When  $C_f = true$ , R shapes f for a module M.

**Definition 3.1** An IRS machine  $R = \langle S, Init, I, C, T, O \rangle$  is a tuple of the following form:

- 1. S is a finite set of states.

- 2.  $Init \subseteq S$  is a nonempty set of initial states.

- 3.  $I = \{i_1, i_2, ..., i_n\}$  is a finite set of inputs.

- 4.  $C = \{c_1, c_2, ..., c_m\}$  is a finite set of constraints, where each constraint  $C_i : S \times 2^I \rightarrow \{\text{false, true}\}\$ is a function that determines the constraints value (either false or true) from the current state and the inputs.

- 5.  $T: S \times I \rightarrow S$  is a transition relation.

- 6.  $O: S \times I \rightarrow C$  is a function that determines the constraint value (either *FALSE* or *TRUE*) from the current state and the inputs.

We require that for every state  $s \in S$  and input  $i \in I$ , there exists some  $t \in S$  such that t = T(s, i). By this definition, IRS accepts any inputs at any state, i.e., it is receptive to all inputs. As in the automaton in Chapter 2, accepting states F can be added to the IRS definition. We shall address the use of accepting states when we verify liveness properties of a switch fabric in Chapter 5, otherwise, all states may be considered as accepting.

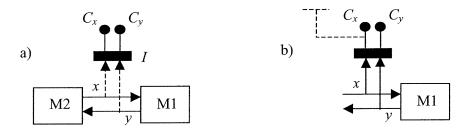

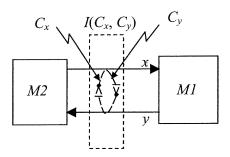

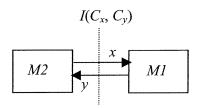

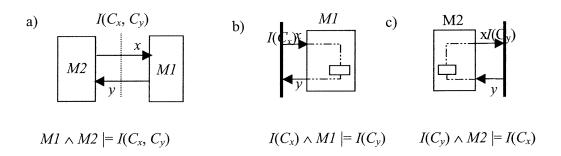

IRS can be used in compositional model checking. Consider a system  $M1 \parallel M2$  in Figure 3.5. We want to verify a property or a specification *spec* about the interactions that occurr at the interface of M1 and M2. An IRS I is first developed to represent a model for *spec*. Then, two constraints  $C_x$  and  $C_y$  are defined to recognize *spec*, i.e., to determine what values may happen on interface signals x and y at each state of x. Now, x and x and x and x are follows.

**Convention**: (Activating a constraint) IRS I and its constraints  $C_x$  and  $C_y$  are denoted as  $I(C_x, C_y)$ . We use the expression "activate a constraint" to indicate that the constraint is set always true during model checking. The formula  $\langle GC_x \rangle$  M  $\parallel$  I  $\langle GC_y \rangle$  asserts that module M composed with I where  $C_x$  is activated satisfies the property that  $C_y$  is always true on I (Figure 3.5b). We represent  $\langle GC_x \rangle$  M  $\parallel$  I  $\langle GC_y \rangle$  by an IRS model checking assertion  $I(C_x) \wedge M \models I(C_y)$ . As in TLA [21], the

We activate  $C_x$  to verify M1 against  $C_y$  (Figure 3.5b), and we activate  $C_y$  to verify M2 against  $C_x$ . We study the problem whether it is sound to conclude M1 // M2 |=  $I(C_x) \land I(C_y)$  from the subgoals  $I(C_x) \land M1$  |=  $I(C_y)$  and  $I(C_y) \land M2$  |=  $I(C_x)$ . The following example demonstrates that such circular reasoning may not be sound.

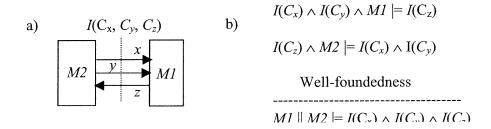

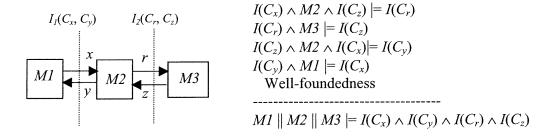

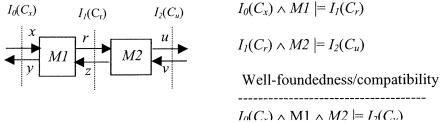

conjunction  $M1 \wedge M2$  represents the composition  $M1 \parallel M2$ .