## Université de Montréal

# Understanding Retargeting Compilation Techniques For Network Processors

par

Jun Li

Département d'Informatique et de Recherche Opérationnelle

Faculté des Arts et des Sciences

Mémoire présenté à la Faculté des Études Supérieures

en vue de l'obtention du grade de

Maître ès Sciences (M.Sc.)

en Informatique

Octobre, 2003

© Jun Li, 2003

QA 76 U54 2004 V. 046

#### Direction des bibliothèques

#### **AVIS**

L'auteur a autorisé l'Université de Montréal à reproduire et diffuser, en totalité ou en partie, par quelque moyen que ce soit et sur quelque support que ce soit, et exclusivement à des fins non lucratives d'enseignement et de recherche, des copies de ce mémoire ou de cette thèse.

L'auteur et les coauteurs le cas échéant conservent la propriété du droit d'auteur et des droits moraux qui protègent ce document. Ni la thèse ou le mémoire, ni des extraits substantiels de ce document, ne doivent être imprimés ou autrement reproduits sans l'autorisation de l'auteur.

Afin de se conformer à la Loi canadienne sur la protection des renseignements personnels, quelques formulaires secondaires, coordonnées ou signatures intégrées au texte ont pu être enlevés de ce document. Bien que cela ait pu affecter la pagination, il n'y a aucun contenu manquant.

#### NOTICE

The author of this thesis or dissertation has granted a nonexclusive license allowing Université de Montréal to reproduce and publish the document, in part or in whole, and in any format, solely for noncommercial educational and research purposes.

The author and co-authors if applicable retain copyright ownership and moral rights in this document. Neither the whole thesis or dissertation, nor substantial extracts from it, may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms, contact information or signatures may have been removed from the document. While this may affect the document page count, it does not represent any loss of content from the document.

### Université de Montréal

## Faculté des études supérieures

### Ce mémoire intitulé:

# Understanding Retargeting Compilation Techniques

For Network Processors

présenté par :

Jun Li

a été évalué par un jury composé des personnes suivantes :

Michel Boyer Président rapporteur

El Mostapha Aboulhamid Directeur de recherche

Francois-Raymond Boyer Codirecteur de recherche

> Marc Feeley Membre du jury

Mémoire accepté le : 26 - 10 - 04

### Résumé

La croissance rapide du marché des télécommunications entraîne une augmentation de la demande concernant des équipements à bande passante plus large.

Les ASIPs (Application Specific Instruction-Set Processors – Processeurs à Ensemble d'Instructions Spécifiques à une Application) présentent des caractéristiques spécifiques qui mettent spécialement l'emphase sur une haute efficacité avec un coût de développement relativement bas. Ceux-ci deviennent, par conséquent, une solution parmi les plus préférées pour le traitement en réseau.

Après avoir étudié un grand nombre de NPs (Network Processors - Processeurs Réseau), nous avons remarqué que ceux-ci possèdent des fonctions spéciales (telles que : PDU à passage rapide, classification, modification, file d'attente, etc.). Ceci résulte en des fonctionnalités d'architectures particulières différentes des autres processeurs embarqués tel que les PE (Processing Element - Element de Traitement) multiples. Ceci est particulièrement vrai en ce qui concerne le parallélisme ou le pipelinage, et certaines instructions spécialisées.

Pour les raisons ci-dessus, nous faisons face à tous les défis des systèmes embarqués ASIPs et des architectures parallèles lorsque nous explorons la technologie de compilation pour NPs. Le compilateur idéal pour NPs doit avoir une excellente capacité de reciblage, une haute performance de parallélisme, et une haute qualité dans la sélection des instructions spéciales, etc. C'est la raison pour laquelle beaucoup de NPs n'ont pas de compilateurs appropriés.

Afin d'explorer la technologie de compilation pour NPs, nous avons travaillé sur une plate-forme de SoC (System on Chip - Système sur Puce) qui comprend des processeurs multiples DLX et un dispositif simple d'interconnexion. Pour notre étude, nous avons utilisé le processeur DLX comme nœud dans le NP. Nous avons réalisé un compilateur C-DLX qui est une extension du compilateur

reciblable lcc. Nous avons ajouté un nouveau *dorsal* afin de générer du code spécifique au DLX. Ce compilateur fonctionne aussi bien sur un processeur simple que sur des processeurs multiples, et certaines parallélisations manuelles simples pour la plate-forme de SoC ont été examinées avec succès. Mais, la qualité du code produit par le compilateur n'est pas aussi bonne que celle du code assembleur DLX écrit manuellement, et la parallélisation automatique n'a pas été implémentée. Beaucoup d'autres tâches ont été effectuées comprenant l'implémentation d'opérations relatives aux octets, la modification du modèle de transfert de données en anneau à jetons pour convenir au transport de données ou le traitement de paquet de bits.

Dans un proche avenir, nous ajouterons des instructions orientées paquet-de-bits au DLX, afin d'accélérer les applications du processeur réseau, qui impliquent beaucoup d'extraction et de manipulation de bits. Cependant, nous rencontrerons une difficulté dans le développement de compilateur pour produire des instructions orientées paquet-de-bits à partir d'un langage de haut niveau. Plusieurs approches ont été explorées, par exemple les CKFs (Compiler-Known Functions - Fonctions de Compilateur Connues). Nous projetons également d'explorer d'autres compilateurs tels que CoSy, SUIF et autres en vue de résoudre le problème des processeus multiples dans les processeurs réseau. Ceci est dans le but de réaliser une méthodologie générale de développement de compilateurs parallèles reciblables pour des NPs.

Mots-clés : processeur réseau, compilateurs parallèles, ASIP, génération de code, compilateurs reciblables, paquet-de-bits.

#### **Abstract**

The rapid growth of the telecommunications market increases the demand for wider bandwidth equipment. As a result, high performance NPs (Network Processors), which can meet the demanded requirements are needed.

ASIPs (Application Specific Instruction-set Processors) have special characteristics which emphasize high efficiency with a relatively low development cost. Consequently, ASIPs are becoming one of the most preferred solutions for network processing.

After studying a large number of NPs, we noticed that certain special functions (e.g. fast passing PDU, classification, modification, and queuing, etc.) resulted in particular architectural features different from other embedded processors such as multiple PEs (Processing Elements). This is particularly true of parallelization or pipeline, distributed memories, and certain specialized instructions.

Due to these reasons, we experienced challenges in regards to ASIPs embedded systems and to parallel architectures when we explored NP compilation technology. The ideal compiler for NPs must have excellent retargetability, high performance in parallelization and high quality in special instruction mapping, etc., which explain why many NPs do not have suitable compilers.

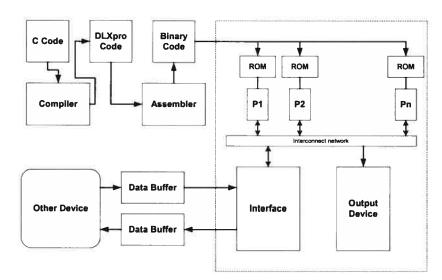

To explore NP compilation technology, we worked on a SoC (System on Chip) platform which includes multiple processors and simple interconnected devices. We implemented a C-DLX compiler based on the lcc retargetable compiler, and added a new back-end to lcc. This compiler worked well when tested using our platform on a single processor and multiple processors, and simple manual parallelization for the SoC platform was successfully tested. However, the quality of the compiler-generated code is not as optimized as the hand-written DLX assembly code; automatic parallelization has not been implemented. Many other tasks were accomplished including the implementation of byte related operations

as well as modification of the data transfer model as a token-ring to suit data transportation or bit packet processing. An output device was also added in order to print information to the screen.

Bit-packet-oriented instructions will be added to DLX, in order to accelerate network processor applications, which perform much of the bit extraction and manipulation. However, difficulties in the network compiler development to generate bit-packet-oriented instructions from a high-level language will be encountered. Several approaches have already been explored, such as CKFs (Compiler-Known Functions). We also plan to investigate other compilers such as CoSy, SUIF, etc. with the purpose of exploring the multi-thread approach in network processors. Eventually, a general methodology for developing NP parallel retargetable compilers will be planned out and achieved.

Keywords: network processor, parallel compiler, ASIP, code generation, retargetable compiler, bit-packet.

# Understanding Retargeting Compilation Techniques for

# **Network Processors**

# Table of Contents

| Abstract                                                             | V   |

|----------------------------------------------------------------------|-----|

| Acknowledgements                                                     | XIV |

| Chapter 1 Intruduction                                               | 1   |

| 1.1 Motivations                                                      | 1   |

| 1.2 Achievements                                                     | 4   |

| 1.3 Thesis Outline                                                   | 5   |

| Chapter 2 Introduction to Network Processors                         | 6   |

| 2.2 Network Applications Profile                                     | 8   |

| 2.3 Network Processor Basic Architectural Features                   | 14  |

| Chapter 3 Compilation Technology                                     | 30  |

| 3.1 Fundamental Conceptions of Compilation Technology                | 30  |

| 3.2 Basic Components of a Compiler                                   | 32  |

| 3.3 Parallel Architectures and Compilation Technology                | 37  |

| 3.4 Lcc Retargetable Compiler Basic Components Introduction          | 41  |

| Chapter 4 Main Challenges in NPs Compilation and Related Work        | 444 |

| 4.1 Network Processors Essential Functions                           | 455 |

| 4.2 NPs' Working Mechanism and Challenges for Compilation Technology | 466 |

| Chapter 5 Implementation                     | 555 |

|----------------------------------------------|-----|

| 5.1 DLX Instruction Set Architecture         | 555 |

| 5.2 SoC Multiple Processors Working Platform | 59  |

| 5.3 Add DLX as New Target to lcc             | 64  |

| 5.4 Test and Result                          | 69  |

| Chapter 6 Conclusion and Future Work         | 755 |

| References                                   | 800 |

| Appendix A: DLX instructions                 | 855 |

| Annendix R. IRM PowerNP Instructions         | 900 |

# Table of Figures

| Figure 1 OSI 7 layer reference model         | 10 |

|----------------------------------------------|----|

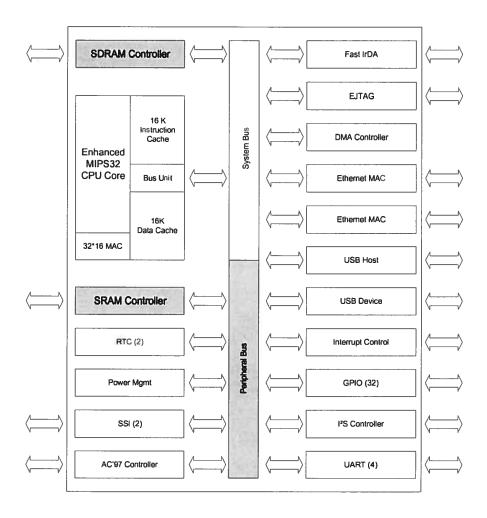

| Figure 2 Alchemy architecture [12]           | 16 |

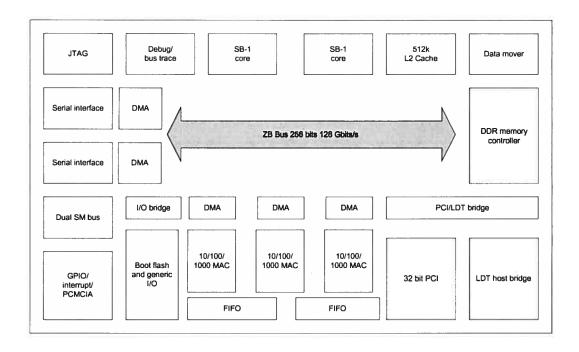

| Figure 3 Broadcom architecture [14]          | 17 |

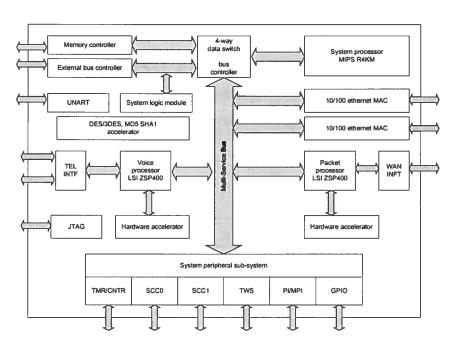

| Figure 4 MSP5000 architecture [20]           | 20 |

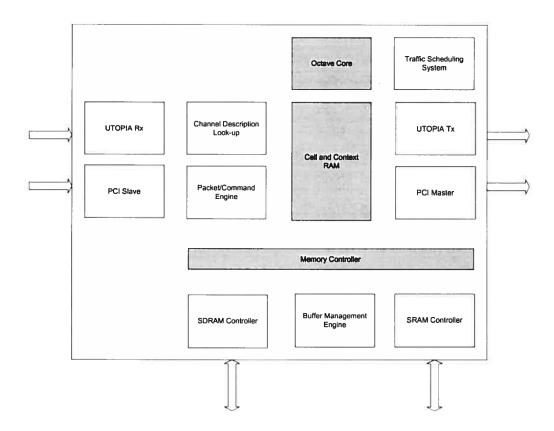

| Figure 5 MXT4400 architecture [22]           | 22 |

| Figure 6 NetVortex architecture [23]         | 23 |

| Figure 7 IBM network processor [25]          | 24 |

| Figure 8 Intel IXP1200 architecture [26]     | 25 |

| Figure 9 Motorola C-5 DCP [27]               | 26 |

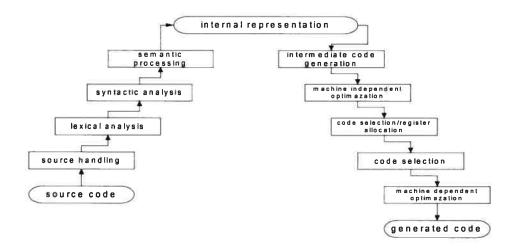

| Figure 10 Compiler components                | 33 |

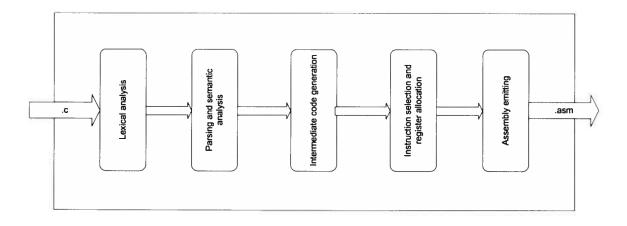

| Figure 11 Lcc C compilation flow [38]        | 42 |

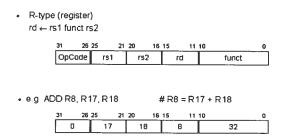

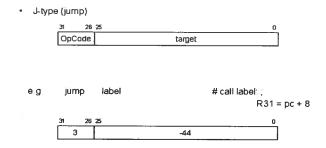

| Figure 12 R-instruction format [48]          | 58 |

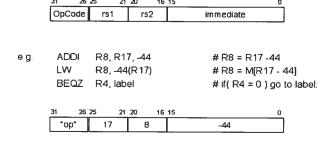

| Figure 13 I-instruction format [48]          | 58 |

| Figure 14 J-instruction format [48]          | 58 |

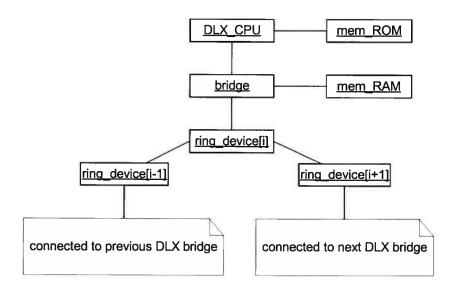

| Figure 15 The architecture of DLX nodes [52] | 61 |

| Figure 16 Overview of entire platform        | 69 |

# Acronyms

AH: Authentication Header

ALU: Arithmetic Logical Unit

ARP: Address Resolution Protocol

ASICs: Application Specific Integrated Circuits

ASIPs: Application Specific Instruction-Set Processors

ATM: Asynchronous Transfer Mode

CAM: Content-Addressable Memory

CPI: Communications Programming Interfaces

CRC: Cyclic Redundant Check

DAG: Direct Acyclic Graphs

DMA: Direct Memory Access

DRAM: Dynamic Random Access Memory

DSPs: Digital Signal Processors

EPC: Embedded Processor Complex

ESP: Encapsulated Security Payload

ESR: Edge Service Router

FIFO: First In First Out

FPGAs: Field Programmable Gate Arrays

FPSR: Floating-Point Status Register

GPPs: General Purpose Processors

HPF: High Performance Fortran

IAR: Interrupt Address Register

IDE: Integrated Development Environment

ILP: Instruction Level Parallelism

IP: Internet Protocol

IPSec: IP Security

IPv4: Internet Protocol Version 4

IPv6: Internet Protocol Version 6

IR: Intermediate Representation

LAN: Local Area Network

LER: Label Edge Router

LEs: Lookup Engines

LSR: Label Switch Router

MAC: Media Access Control

MAC: Multiply-Accumulate

MIMD: Multiple instructions, multiple data

MISD: Multiple instructions, single data

MPI: Message Passing Interface

MPL: Message Passing Library

MPLS: Multi-Protocol Label Switching

MTAPs: Multi-Threaded Array Processors

NPs: Network Processors

NPUs: Network Processor Units

OS: Operating System

OSCI: Open SystemC Initiative

P2P: Peer-to-Peer

POS: Packet over SONET

PVM: Parallel Virtual Machine

RISC: Reduced Instruction Set Computers

RTL: Register Transfer Level

SDPs: Serial Data Processors

SIMD: Single instruction, multiple data

SISD: Single instruction, single data

SLAs: Service-Level Agreements

SoC: System on Chip

TCP: Transport Control Protocol

TLE: Table Lookup Engine

TOPs: Task Optimized Processors

TSP: Traffic Stream Processor

UDP: User Datagram Protocol

USB: Universal Serial Bus

VC: Virtual Circuit

VCI: Virtual Circuit Identifier

VLAN: Virtual Local Area Network

VLIW: Very Large Instruction Word

VoIP: Voice over IP

VPI: Virtual Path Identifier

VPNs: Virtual Private Networks

VPs: Virtual Paths

## Acknowledgements

I would like to express my utmost gratitude to my director, Professor El Mostapha Aboulhamid, for all his support since I began my research in the LASSO Lab. I greatly appreciate the opportunity to work on such an interesting project under his valuable guidance. I would further like to thank him for his efforts in directing me in the way of relevant research, generating interesting ideas as well as for his kind encouragements. It would not have been possible to finish this project without his directions or reviews.

I would like to extend my thanks to my co-director, Professor Francois-Raymond Boyer of École Polytechnique de Montréal. He also provided me with significant research direction and reviewed all topics in this thesis. Without his keen guidance, this thesis would also be impossible to finish.

Special thanks go to Professor Michel Boyer and Professor Marc Feeley for their time, patience and evaluation.

Finally, I would like to thank my colleagues Luc Charest and Alena Tsikhanovich as they have built the SoC platform which is my work environment. Michel Reid and Bruno Girodias maintained all computers in working condition as well as solved all technical problems promptly. Quan Xin and Hongmei Sun, for all their fascinating discussions on the topics of this research and helping me broaden my horizons.

# **Chapter 1 Introduction**

# 1.1 Motivations

In recent years, the telecommunications industry has rapidly expanded. Bandwidth needs are increasingly expanding because new media such as high quality radios, TVs, etc. over IP (Internet Protocol) are required. As a result, the market will not only require wider bandwidth links but also faster and higher level analyses of packets in routers and front-ends of server arrays. Therefore, high performance network processors may fill these needs.

An ASIP (Application Specific Instruction-Set Processor), a processor with a specific instruction set for a particular application domain is becoming the most popular solution for network processing because of its special characteristics. ASIPs lie between ASICs (Application Specific Integrated Circuits) which have the highest efficiency and GPPs (General Purpose Processors) which have the lowest development cost. As a result, ASIPs provide good balance of hardware and software to meet all requirements such as performance, flexibility, fast time response to market, power consumption, etc. Consequently, a networking application may be specified as a software programmable device with architectural features and/or special circuitry for packet processing. A network processor can be regarded as an ASIP for networking application domain [1].

As a network traffic manager, NPs (Network Processors) usually engage several processors working together. Most of NPs own the special instruction set that is designed for data forwarding and other packet oriented operations, in order to complete many diverse functions such as QoS (Quality of Service), compression, security-authentication, encryption/decryption, etc. It should be noted that NPs only run on partially protocol stacks but not all 7 layers, Since NPs are designed to handle PDU (Protocol Data Units) processing by access data stream.

Varieties of special functions of network processors are catalogued as follows and will generate different challenges which will be encountered during the development of NP compilers.

• PDUs passing swiftly: The network processor should be able to deliver the arriving data packets on time. As a PDU is coming and being sent out, the time gap is extremely short, therefore leaving the network processor little time to

accomplish the necessary tasks to be applied to an incoming PDU before resending it.

- PDUs classifications: When a PDU arrives, its contents should first be examined to determine the required processing followed by its retransmission. This process is used in firewalling, routing, policy enforcement, and QoS (quality of service) implementation.

- PDUs modification: A PDU may be modified by the network processor. For example, the time-to-live counter of an IP packet will be reduced, or an outgoing label will replace an incoming label in label-switched traffic. Modification is often necessary to recalculate a CRC (Cyclic Redundant Check) or checksum and headers may be removed or added.

- To queue: When the processing speed of the network processor is slower than the data arriving speed, it is then necessary to queue the PDUs. The order of retransmission may not be the same as the order of transmission. For instance, some PDUs will be dropped, and some PDUs may be prioritized over other PDUs. [2]

A network processor has to classify, modify, and queue the PDUs in order to ensure efficiency of the network. Other functions include: compression, policing, traffic metrics, security-authentication, encryption and decryption. Network processors are different from the majority of other embedded processors due to special features, namely the presence of multiple processor elements (PEs), running parallel or organized in a pipeline, distributed memories and bit packet passing. Some of the NPs, such as Agere Routing Switch Processor and Cisco's PXF, use VLIW (Very Large Instruction Word) architectures; VLIW lets these NPs taking benefit from intra-thread ILP (instruction-level parallelism) at compiling time. It may increase utilization of a hardware unit by sharing most of them but also creates more difficulties for compiler developers [1]. On the other

hand, NPs have multiple processors, particularly different kinds of processors working in a SoC (system on chip) that require compilers to have good retargetability.

The market requires a fast response time to create desired and high reliability network equipments. In order to meet this need, embedded software require appropriate compilers to stay away from slow and error prone assembly language development. However, classical compilation technology is insufficient for a particular architecture of network processors and consequently compilation technology for network processors is extremely important and in high demand. Because network processors have special features, we are faced with challenges related to ASIPs embedded systems and those related to parallel architectures when we explore compilation technology. In chapter 4, we will give an overview of related work in this area.

### 1.2 Achievements

We worked with a cycle-accurate SoC platform, created by our colleagues Luc Charest and Alena Tsikhanovich, which included multiple processors. It was developed using SystemC on Linux PCs. The modeled processors are DLX or ARM architectures (still in development), and both of them can work together. Each processor is an addressable device with a local memory, and processors are connected via a device called ring\_device, where every pair of adjacent nodes can send and receive messages concurrently. We will provide a detailed description of the platform in chapter 4. Our colleagues worked on the platform using handwritten assembler codes but this became time-consuming when writing and debugging assembler codes.

A C-DLX compiler was implemented based upon the lcc retargetable compiler. In fact, we added a new back-end that is a DLX code generator. The compiler derived from lcc with its fast, small and convenient features will significantly improve the development and debugging time. This compiler worked well when we tested it using our platform on single processor or multiple processors and successfully tested simple parallel applications on the SoC platform with manual parallelization. We implemented byte related operations, such as LB, LBU, SB, SBU, etc., as well as modified the data transfer model to suit parallel processing. An output device was also added in order to print needed screen information. These modules and functions enable us to simplify and decrease time spent testing and debugging. However, the quality of the compiler-generated code is not as good as the hand-written DLX assembly code.

### 1.3 Thesis Outline

The remainder of this thesis is organized as follows: Chapter 2 briefly describes network processors (NPs) and its basic features. Chapter 3 presents an overview of compilation technology and discusses typical compiler components. Parallel compilation is then explored and the lcc retargetable compiler is introduced. Chapter 4 presents the main challenges of compilation technology in the domain of NPs and studies related works. We will explain how the DLX back-end can be implemented on lcc, and what kinds of changes have been made on our SoC platform. We also describe the benefits/weaknesses of our compiler and platform in chapter 5. Chapter 6 concludes this thesis; outlines future works as well as reviews and identifies challenges relating to NPs' compilers.

# **Chapter 2 Introduction to Network Processors**

The speed of telecommunications is being changed rapidly. Changes on society and work habits impose on more and more people the requirement to be practically an "infinite" bandwidth. For examples, they consist of Voice over IP, Streaming audio, interactive video, Peer-to-Peer (P2P) applications, Virtual Private Networks (VPNs). New technologies offer more capacity and flexibility for faster and cheaper implementation of new features. All these factors support a booming IT industry, which is growing at a rate of exponential scale. These changes also have a profound effect on the way network processors are developed. A need has arisen for a new generation of network processor architecture that makes use of the technological advances, at the same time

allowing for flexibility of implementation. As for the future network architecture, both revolutionary and evolutionary development has been foreseen. The new network processor architecture must be an evolution of today's network processor. Networks are required to support new protocols, and include diverse services, security, and various network management functions, which effectively handle new applications. The increasing power of processors and continuous development of software technology creates the possibility to develop more powerful and productive applications. The new network should have the capacity, common interfaces, and protocols to support the mutual interaction in a seamless manner.

#### 2.1 A Brief Introduction to Network Processors

"A network processor is a software programmable device with architectural features and/or special circuitry for packet processing; it is an ASIP for the networking application domain" [1]. However, network processors do not provide all solutions to network applications and this definition is reflecting the wide range of programmable architectures proposed for network processing. Therefore, network processors have similar characteristics with many different implementation choices such as network co-processors, communication processors used for networking applications, programmable devices for routing, reconfigurable fabrics and general-purpose processors for routing. Form tasks point of view, network processing responsibilities could be divided into several planes which include forwarding plane to control data packet flow, protocol conversion and a control plane to perform flow management, stacks management, routing protocols, etc.

# 2.2 Network Applications Profile

By decompounding network applications, we are able to study and to analyze the general network applications in detail. In is section, we are going to discus network applications performed particular operations and network processors' special architectural characteristic.

## 2.2.1 Network Applications

In order to study network application, the protocol standards must be fully understood. For a clear description of the NPs working mechanism, OSI stack model becomes fundamental knowledge that can be used to map NP's operation into OSI stack layers; the following is a brief description related to the 7 layers in the OSI stack model [3].

Layer 1: The physical layer is responsible for moving bits across a shared media, which is defined by the layer, over which point-to-point links are established.

Layer 2: The data link layer provides a link between two points and can create reliability on top of an unreliable physical link. The data link layer operations have been performed historically in hardware, the network processors are attacking this task. The data link layer provides error detection and correction in low levels. If a packet is corrupted, the data link layer is responsible for retransmitting this packet.

Layer 3: The network layer is using the point-to-point communication facility, provided by the data link layer, which enables communication between any two computers. This layer is the most complex one among all the layers, because it must address the data packets. It is responsible for the routing of data to a remote

location across the network, and each packet is addressed and delivered in this layer.

Examples of layer 3 processing: IP filtering, Local Network Emulation (LANE), IP fragment re-assembly, multi-protocol over ATM, multicast forwarding and Virtual Private Networks.

Layer 4: The transport layer determines a point of access for higher applications to communicate with the other end-station. The port number and the IP address define a point of access, i.e. a socket. Both UDP and TCP provide a port number to higher layers in order to identify an individual socket. We describe parts of the protocol, which are relevant to network processors only, because much of the transport layer functionality is only executed on an end-station.

Examples of layer 4 processing: TCP stream following, Proxying, stream reassembly, Rate Shaping, content-based routing, Port Mapping (NAT), Load balancing (LB) and QoS/CoS.

Layer 5-7: session, presentation, and application layers. The application layer may include file transfers and display formatting. An example of application layer protocol is HTTP. Protocols, which are commonly known and considered to be part of the 7 layer, actually may occupy the 5-7 layers. Most of the Session, Presentation, and Application layers tasks are executed on an end-station while network equipment in the fabric may access those layers.

Examples of layer 5 to layer 7 processing: virus detection, traffic engineering, accounting and interruption detection.

Figure 1 shows the data path to describe how network process data over OSI 7 layer model. The gray path represents a physical wire or media connecting devices, and paths in white demonstrate the virtual paths for peer level.

| 7 | Application  |                    |                              |           |          |     |             |   |          | Application | 7            |   |

|---|--------------|--------------------|------------------------------|-----------|----------|-----|-------------|---|----------|-------------|--------------|---|

| 6 | Presentation | <=End to End>      |                              |           |          |     |             |   |          |             | Presentation | 6 |

| 5 | Session      |                    | Sile to Bile                 |           |          |     |             |   |          | Session     | 5            |   |

| 4 | Transport    |                    |                              |           |          |     |             |   |          |             | Transport    | 4 |

| 3 | Network      | Network 🗢 <===>    | Network <> <====> <=> <=>=== | <= m m m> |          |     | <b>&gt;</b> |   | Network  | 3           |              |   |

| 2 | Data Link    | <b>\rightarrow</b> | <b>◊</b>                     | 0         | <b>◊</b> | <=> | ٥           | 0 | <b>◊</b> | 0           | Data Link    | 2 |

| 1 | Physical     | 0                  | 0                            | 0         | ٥        | 0   | 0           | < | 0        | 0           | Physical     | 1 |

Figure 1 OSI 7 layer reference model

Here a request is made by a user who wants to go out of the network. The request comes in the Application Layer from the upward position of the Application Layer. The Application Layer encodes the request in the form, which might be understood by its peer layer protocol on the right stack. Then it is passed down by the Application Layer to the Presentation Layer, which suits with the data handed from the above layer. Next it packages it in a form, which can be understood by the peer layer protocol on the right stack and which also knows what to do with it.

The higher level data's re-encapsulation process goes on in Figure 1 down the left stack until it reaches the physical layer, which layer the data is passed by a wire, or by a wireless medium to another device, like a router. It accepts the data, brings it up to the Data Link Layer, verifying the bits being received are the transmitted bits from the left by examining the checksum. The payload is passed up by the Data Link Layer to the Network Layer, which examines the header information of the packet and decides what to do with the destination address and other header information. Then it passes to another router to its right. The packet now must travel back down this router's stack to the physical layer so that the next router may take the same process. The packet goes down and across the physical layer wire to the other router, up its layers, and back down again to the right stack. The destination host is ready to process it, taking the coming bits, and packeting them

into a frame, a cell, or a packet. If it is fine, then it is passed up to the Network Layer, which examines the header, added by the original left stack, and the header decides if the packet is good to be passed up. This process repeats with each layer. The header information is examined and is known by the respective layer in terms of how to deal with its payload. The user's original request above the Application Layer of the left stack goes the way to the top Application Layer of the remote machine finally. Either a remote user or a remote program acts on the incoming data and responds. If a response is delivered, the procedure happens again. The response goes from the right side to the Application Layer of the left stack and its user, in the end [4].

#### 2.2.2 Protocol Standards

The following protocol descriptions highlight applications related to protocol standards across different layers but not the detail of each protocol.

### • IP Security

IP Security (IPSec) includes two protocols: Authentication Header (AH) and Encapsulated Security Payload (ESP) [5]. IPSec currently supports IP version 4 packets. IPv6 and multicast support is coming later. IPSec is a layer 3 protocol that offers a platform for higher layer protocols. Higher layer protocols can define their own specific security measures. AH or ESP can be implemented in a transport mode that only protects higher layer protocols or it can be implemented in tunnel mode which protects the IP layer and higher layer protocols by summarizing the original IP packet into another packet [1].

## Asynchronous Transfer Mode

Asynchronous Transfer Mode (ATM) is a dedicated connection switching protocol. It is a hybrid form using fixed-size blocks over virtual circuit is chosen as a compromise that gives reasonably good performance for bandwidth traffic. The end stations determine a virtual circuit (VC) or throughout ATM network. As a matter of fact, it is a connection-oriented standard. There are different virtual paths (VPs) or paths between switches in the virtual circuit. To set up a virtual circuit by the control-plane functions, an ATM switch just switches ATM cells from input ports to output ports. The switching is based on referencing a table which is indexed by two fields in the ATM cells: The Virtual circuit identifier (VCI) is an 8-bit VC identifier and the Virtual path identifier (VPI) is a 16-bit VP identifier. Subsequently, a switch may update the new link and then, by changing the VPI and VCI fields, the cell can continue to travel [6].

#### Virtual Local Area Network

Virtual Local Area Network (VLAN) is a group of workstations which may be distributed in several physical LAN segments. However, they can communicate with each other like they work within a LAN. Another feature to define VLAN is to check the MAC address of each frame. The switch or router will require the MAC address and verify it, this processing is called MAC layer grouping. Network layers can also be grouped by examining the network layer address so that the VLAN membership can be determined. VLAN can also be defined as an IP multicast group and in this case the router will be a key device to support IP broadcast. In another way, for a VLAN group to be determined for a frame, a unique identifier is needed in the header in order to distinguish the VLAN membership. This identifier is added by the switch [7]. User can get several benefits by using VLAN architecture, such as increasing network performance,

increasing security options, etc. VLAN also present an easy and flexible way to modify logical groups separated in deferent physical LAN segments.

#### IPv4 and IPv6

Internet Protocol's (IP) main function is to move packet of data from node to node. Internet Protocol Version 4 (IPv4) is the most broadly used protocol for layer 3 communication. Routing, fragmentation and reassembly, and address resolution protocol (ARP) are the typical working sequential of IPv4. Fragmentation/re-assembly will be applied if an IP packet is bigger than the Maximum Transmission Unit (MTU) of the data link layer. ARP map IP address to physical network address [9].

"Internet Protocol Version 6 (IPv6) is the next generation of protocols designed by the IETF" [10] (The Internet Engineering Task Force) to replace the current Internet Protocol version, IPv4. IPv6 can be seen an increase in the address space from IPv4's 32-bit to 128-bits [11]. As a result, IPv6 has nearly unlimited numbers of available addresses compared to IPv4's. Routing and network auto configuration are two other improvements emphasized by IPv6.

### Transport Control Protocol

Because an unreliable medium such as IP may drop packets, a simple protocol could not solve this problem. Transport Control Protocol (TCP) provides layer 4 communications for higher layer applications over those undependable mediums such as IP. TCP's main function is to verify the correct delivery of data from client to server. TCP can detect errors or lost data and issue retransmission request to ensure that data is correctly and completely received.

A TCP header have information such as the Destination port number, the Header Length, the Source Port number, the Sequence Number and Acknowledgement Number. TCP also contains flags that serve essential functions. For example, the ACK acts as an acknowledgement validation flag, the SYN flag establishes connection, the PSH flag can ensure the receiver passes data to application without delay, the RST flag resets the connection, and the FIN flag indicates that the sender has finished sending data. Aside from this information, TCP also contains valuable information such as window size and acceptable data and information of TCP Checksum [9].

#### 2.3 Network Processor Basic Architectural Features

There are many network processors available on the market and this section includes some of them. From usage point of view, network processors can be separated into three equipment areas that are called as core equipments, edge equipments and access equipments. These areas work for different applications and performance requirements.

Core devices are located at the center of the network. Gigabit and terabit routers are typical core devices. Core devices take important tasks in network traffic management. As a result, the performance will be a critical measurement for the core devices. Core devices have less flexibility compared to others.

Access equipments support different kinds of devices connecting the network. The majority usage of access devices is to combine big amount of traffic streams and to forward them throughout network. Modem, network card as well as computer wireless connector are examples of access devices.

Edge device is not responsible for collecting network routing information, just simply uses the routing information that comes from the up level routers. The

performance and flexibility requirement for edge devices sit between the core device and access devices. Load balancers, edge routers and firewalls are topical edge devices.

From a functionality point of view, network processors can be divided into two categories which are data plane and control plane. Data-plane network processor main task is to forward packets from the source end to the destination end. Data plane algorithms are usually implemented by parallel processors, which need to be performance optimized as they need to decode and move around large amounts of data to satisfy QoS requirements. That is why network processors optimization is focused on data-plane. Control plane network processor has lower performance requirements; they are used to control packet traffic flow. [2]

We studied different network processors' architectures and summarized them in following sections.

### 2.3.1 Alchemy (Au1000)

The Au1000 is a SoC design for the Internet edge device market. It is a complete SOC based on the MIPS32 instruction set. The Au1000 runs up to 500 MHz. and its' power consumption is less than 0.5 watt for the 400 MHz version. "MIPS-compatible core provides lower system cost, smaller form factor, lower system power requirement, simpler designs at multiple performance points and shorter design cycles" [12]. In addition, there are special instructions for conditional moves, counting leading and memory prefetch. The Alchemy Au1000 can be programmed in C and support for MS Windows CE, Embedded Linux, and VxWorks operating systems. Development tools include complete MIPS32-compatible toolkit and some third party compilers, assemblers and debuggers

[12]. Manufacturer highlights the Au1000 performance in the spec sheet [12] as follow:

"Highly-integrated system peripherals include two 10/100 Ethernet controllers, USB device and host, four UARTs, AC'97 controller, two SPI/SSI interface. High-bandwidth memory buses offer 100/125 MHz SDRAM Controller and SRAM/Flash EPROM controller." [12]

Figure 2 Alchemy architecture [12]

#### 2.3.2 Broadcom BCM-1250

BCM-1250 is the first network processor of Broadcom. BCM-1250 is focused on layers 3-7 processing [1]. The SB-1 can execute two instructions for load or store and two instructions for ALU operations at each clock cycle. Each processor has a 32kb L1 cache and the two cores share a 4-way associative 512kb L-2 cache. Two 64-bit MIPS CPUs (SB-1) of SB-1250 can run at up to 1 GHz and do not use any special instructions for packet processing [13]. The SB-1250 also includes three on-chip Ethernet MACs and two packet FIFOs. A 256-bit bus that runs at half of the processor speed called ZBbus connects the major components of the chip. The Broadcom SB-1250 support operating system for NetBSD, Linux, and VxWorks [14].

Figure 3 Broadcom architecture [14]

#### 2.3.3 Cisco PXF

Parallel eXpress Forwarding (PXF) use a pair of ICs which are build by Cisco parallel processing technology, The Cisco PXF is an inner product for Cisco edge routers and only be used calculate layer3 data path [15]. The pair of ICs has 32 processors; each processor is a 2-issue VLIW instruction set and brings its own local memory. Particular instructions are used for packet processing. There are 8 stages in the pipeline.

The PXF is benefited from certain features of distributed architectures such as parallel processors. A processor using a parallel array could accelerate a switching path. Another architectural feature, which has been used to improve performance, is distributed memory access and assigns memory to each column of processors as well as allocates independent memory to each processor. Distributed memory access also uses multiple memory banks within a per-column array to optimize the memory access. Modularization of functionality was also used to improve performance. PXF distributes data structures across multiprocessor arrays and by doing so, the distributed task-oriented memory resources have been used to allow parallel processing to fulfill complex tasks [15]. It should be noticed that VPN Acceleration Module (VAM) is not compatible with the PXF processor. The PXF supports Cisco's internal operating system, IOS.

### 2.3.4 EZchip NP-1

The NP-1 is a single-chip solution developed by Ezchip Technologies Inc., it based platforms can be developed to implement switching, routing, and QoS functions as well as flow based traffic policing, URL switching, and security application. NP-1 is a 10-Gigabit 7-Layer Network Processors.

The NP-1 use EZchip own Task Optimized Processors (TOPcore), TOPcore using customized instruction set and data path for each packet-processing task in order to achieve best performance. TOPs are arranged in a pipelined way and are composed of TOPparse, TOPsearch, TOPresolve, and TOPmodify.

Ezchip has their own development toolkit-Ezdesign, which allows NP-1 application developer to write, test and debug programs when implementing customized applications. EZdesign includes Assembler/Compiler, Cycle accurate Simulator, Traffic and Structure Generators, Applications Library and a Debugger [17].

#### 2.3.5 Xelerated Packet Devices X40 and T40

Xelerated's network processor is based on a fully programmable pipeline. The core block is the PISC (Packet Instruction Set Computing). By using PISC technology, Xelerated provides two network processor chips. The first one is Packet Processor that is called X40, and the second one is Traffic Manager that is called T40.

"The X40 Packet Processor includes 10 pipeline stages and also includes 384k counters and 128k meters for traffic metering and conditioning decisions making. The Xelerator T40 enables advanced traffic management at 40 Gbps wire speed. The forwarding plane of the T40 includes Rx ports, a programmable input pipeline, a queue Engine, a programmable output pipeline, and Tx ports. PISCs can also take tasks such as protocol encapsulation, statistics counting and classification" [19].

Xelerated full production line includes X40 packet processor, T40 traffic manager, Xelerator control plane software, Xelerator forwarding plane applications and development tools. A user needs to program X40 and T40 separately since each pipeline stage executes a different program.

## 2.3.6 BRECIS MSP 5000

BRECIS provides a network processor that is called MSP5000, which includes a MIPS CPU, two 10/100 Ethernet MACs, a Security Engine, a Voice Engine, and a Packet Engine [20].

MSP5000 offers voice and packet processing software that is supported by multiservice platform applications. BRECIS' development toolkit is called FastStart, which includes a development board and support for Linux, and VxWorks operating systems.

Figure 4 MSP5000 architecture [20]

#### 2.3.7 Mindspeed MXT4400

The MXT4400 Traffic Stream Processor (TSP) platform is offered by Mindspeed Technologies. It can serve wide applications rang from OC-3 to OC-48. To save system developing time, Mindspeed Technologies provides PortMaker software for the MXT4400. PortMaker is an application collection for AAL5 SARing (PortMaker-SAR) and ATM traffic shaping, policing and OAM cell processing (PortMaker Cell Traffic Manager). The source code is opened to customers who want to do further development.

"TSP Board Development Kit provides a chip model, test bench and diagnostic code for hardware design verifications. The TSP Design Toolkit is a powerful development environment for customers modifying PortMaker source code or developing custom applications." [22].

Figure 5 MXT4400 architecture [22]

#### 2.3.8 Lexra NetVortex PowerPlant

Lexra's NetVortex PowerPlant [23] processor integrates sixteen LX8380 32-bit RISC processors on a chip that speed up to 420-MHz clock frequency. Each processor runs a modified instruction set that is based on the MIPS-I instruction set. The instruction set has been extended by Lexra to provide specific support for many functions required from routers. "The new instructions have been added to the MIPS-I instruction set in the LV8380 are optimized for operations such as bit field manipulation, packet checksum, and support for multithreading." [24].

Figure 6 NetVortex architecture [23]

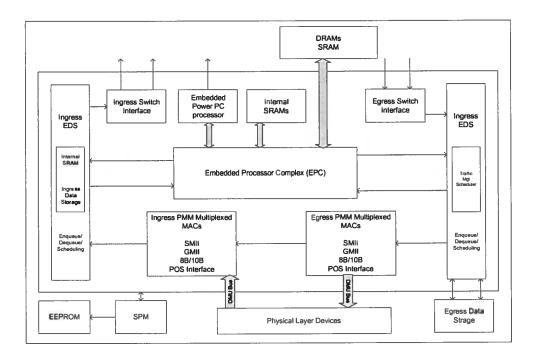

#### 2.3.9 IBM PowerNP

IBM PowerNP provides a multiprocessor solution including an Embedded Processor Complex (EPC) which has a PowerPC core, 7 dedicated co-processors and up to 16 protocol processors. PowerNP supports Packet over SONET (POS) and gigabit Ethernet at 2.5 Gbps. [25]. The 7 co-processors have special functions such as data store, Checksum, Enqueue, Interface, String Copy, Counter and Policy. The IBM Code Development Suite includes an assembler, a debugger and a system simulator.

PowerNP's Functional blocks includes Physical MAC multiplexer that is responsible for moves data between physical layer devices and the PowerNP, and Switch interface which "supports two high-speed data-aligned synchronous link"

(DASL) interfaces, standalone operation (wrap), dual-mode operation (two PowerNPs interconnected), or connection to an external switch fabric." [25].

Figure 7 IBM network processor [25]

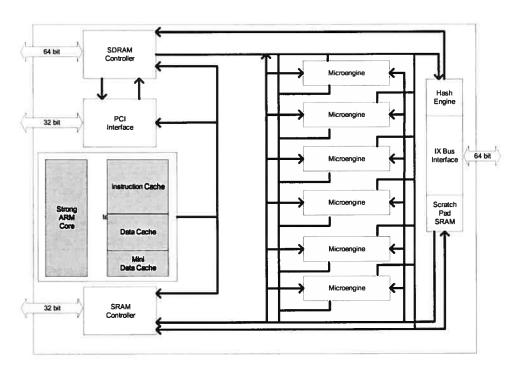

#### 2.3.10 Intel IXP1200

The Intel IXP1200 can support packet rate up to 2.5 Mpackets/s. The IXP includes a StrongARM controller and 6 micro-engines. Each micro-engine has up to 4 threads hardware support; therefore, there are total 24 threads running on the chip to perform packet processing. IXP 1200 uses IX 64-bit bus that provides high bandwidth connection in the middle of StrongARM controller, memory, micro engines and other devices.

The development tool is called IXDP1200 Advanced Development Platform, which includes available evaluation software, example designs, utilities and libraries, ATM/OC-3 to fast Ethernet IP router example design, WAN/LAN access switch example design, and Windows NT integrated development environment for embedded Linux. Unfortunately, before releasing the C compiler, all programming must be completed by macro-assembly, which is a very difficult task since there are 6 micro-engines working in parallel. However, Intel offers the Integrated Development Environment (IDE) which can provide an assistant to program the device making debugging easier because of "its configurable simulation environment and its visualization" [26].

Figure 8 Intel IXP1200 architecture [26]

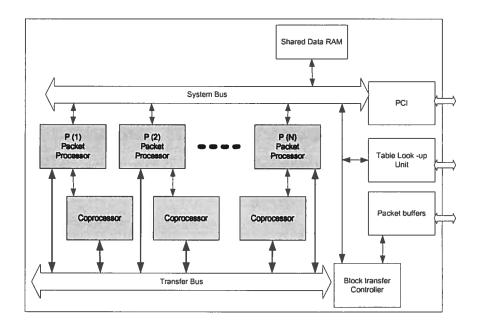

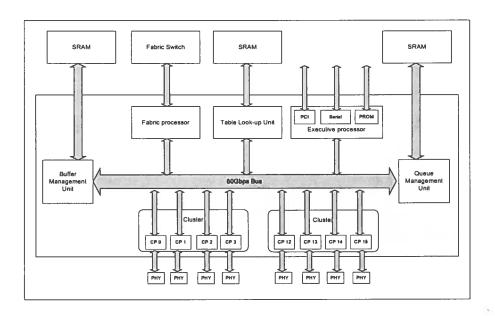

#### 2.3.11 Motorola C-5 DCP

"The Motorola C-5 DCP is a SoC NP including multiprocessor, it is designed for layers 2-7 processing speed rate up to 2.5 Gbps. 16 channel processors and 5 coprocessors for system management. Five co-processors are executive processor, table lookup unit, fabric processor, queue management processor and buffer management processor.

Each channel processor includes a RISC core and two parallel serial data processors which perform communication function. The RISC cores are responsible for classification, policy enforcement, and traffic scheduling" [27].

The C-5 DCP development tools include a C/C++ compiler and users' C-Ware Communications Programming Interfaces (CPI) which abstracts common network task building blocks. [28].

Figure 9 Motorola C-5 DCP [27]

Through the previous NP overview, we can conclude that the network processors are multiple parallel ASIPs which work as an embedded system. The network processors have special features such as multiple processing elements (PEs) which work in parallel by using distributed/shared memory and special instructions.

Most network processors use parallel processing through multiple Processing Engines (PEs) and their architecture can be divided into two types: one is parallel architecture, and the other one is pipeline stage architecture. Parallel NP architecture usually contains bit manipulation circuits to increase packet processing ability; many of these PEs are put into one SoC chip to increase physical space efficiency. In parallel mode, the task scheduler is responsible for transferring packets to different PEs. It keeps track of which PE is available and then sends it a task. Parallel NPs can produce higher bandwidth networking appliances because of their architecture features.

In pipelined architecture, each processor is responsible for a specific packet processing assignment; communication between processors utilizes pipelined way and is very similar to data flow processing: a PE sends a packet to the next PE as soon as a PE finishes the packet processing. Motorola's C-5 DCP is an example of this kind of architecture.

Although NPs have basic features such as special function units, on-chip interconnect methods and the variation in memory architectures. NPs also have other features, One of these common features is a number of distributed processing elements which process packets in a parallel fashion in order to exploit

the parallel nature networking applications. Most companies provide their own programming model which exposes various elements of the hardware. This allows users to be able to map a domain specific language and then automatically map down to machine codes to be implemented in the hardware.

Special instruction is the interface to operate specialized hardware. IBM PowerPC is an example; it defines special instructions such as cache block touch instructions for loading data before the data is needed. This special instruction reduces the memory latency.

In most network-transfer formats, bit-fields are packed together to save bandwidth, however, normal GPP instructions cannot handle these fields efficiently. As a result, Bit-packet-oriented instructions [29] are needed to accelerate network packets processing. Unfortunately, after using this kind of instructions, a big challenge to compilation technology will appear since it is very hard to find which sequence of instructions can map to a bit-packet instruction.

Table 1 is a summary of the basic features of NPs. We can summarize them as follows: NPs are multiple processors working in parallel or in pipeline. Normally they have special instructions and shared (or distributed) memory. These features bring more challenges to compilation technology that will be discussed in chapter 4.

Table 1. Typical NPs comparison

| NPs          | Intel<br>IXP1200 | Lexra             | Ezchip<br>NP-1 | IBM<br>PowerNP | Motorola C-5 |

|--------------|------------------|-------------------|----------------|----------------|--------------|

|              |                  | NetVortex         |                | PowerNP        | DCP          |

| Compilers    | C compiler       | С                 | C/assembl      | Assembler      | C/C++        |

|              | Assembler        |                   | er             | only           |              |

| Capacity     | 2.6 Gbps         | >10 Gbps          | 10Gbps         | 8Gbps          | 5 Gbps       |

| OSI layers   | 2-7              | *                 | 2-7            | 2-5            | *            |

| Multi-PE     | 6                | RISC with special | 64 task        | 16             | 16 channel   |

|              | programmable     | instructions      | oriented       | processors     | processors   |

|              | processors       |                   | processor      | -              | _            |

|              |                  |                   | s              |                |              |

| PE           | FBI Fast Bus     | 64 bit            | *              | *              | 60           |

| Interconnect | Interface        | Vortex bus        | -              |                | Gbps         |

|              |                  | 427 MHz           |                |                | bus          |

| No. of PEs   | 6                | 2                 | 64             | 16             | 16           |

| Threads/PE   | 4                | 2                 | 64             | 16             | 16           |

| Memory       | Shared 4 kb      | 1-8               | *              | 2              | 4            |

|              | SRAM FIFOs       |                   |                |                |              |

<sup>\*</sup> Means no specification

# **Chapter 3 Compilation Technology**

#### 3.1 Fundamental Conceptions of Compilation Technology

In the early stages of the computer age, many software systems were developed by using assembly language to achieve efficient execution. However, it brought much more workload in coding, debugging and maintenance stages. Presently, most modern computer systems (both of OS and application) are developed by using high-level languages in order to obtain better coding efficiency, higher algorithms abstraction and easier maintenance.

High-level language programs are more human friendly, but they cannot run directly on hardware processors and must therefore be translated into a

corresponding machine code before it is executed. As a result, translators are required in this situation. Here we provide an overview of the internal structure of translators and classify them into several categories.

The development of a translator involves at least three languages, which are source language, target language and host languages. The host language is used to implement the translator, the source language is the resource code to be translated, and the target or object language is the one to be generated. The host and object languages remain hidden usually from a user of the source language. A translator may be defined as a formal function. Its domain is a source language and its range is contained in an object or target language. [30]

One well-established class of translators is the assembler, which maps low-level language instructions into machine language code that can later be executed on a specific processor. The machine-level instructions are mapped 'one-for-one' by individual source language statements. Another is the macro-assembler, which is a variation of the assembler as it also maps low-level language instructions into machine code. Some macro statements may map into a sequence of machine-level instructions effectively providing a text replacement facility to suit the users.

The compiler is another well-established class of translators which maps highlevel language instructions into machine code and subsequently machine code can be executed. An individual source language statement usually maps into many machine-level instructions.

The pre-processor maps a superset of a high-level language into the original high-level language or performs simple text substitutions. The high-level translators are useful as components of a two-stage compiling system. Those translators map one high-level language into another high-level language.

The decompiler is a translator which takes a low level language as the object code and then regenerates the source code at a high-level language, but it is difficult to recreate the original written source code although this can be done successfully for the production of assembler level code.

Microcomputers and embedded systems often use cross-compilers, which generate code for computers and systems other than the host machine since they are too small to allow the translators to generate code on themselves. Self-resident translators are those translators that generate a code for their host machines. The cross-translators may bring additional problems during the transfer of the object code from the donor machine to the object machine that is set to execute the translated program.

The machine code, which is the output of some translators, is loaded in a machine at fixed locations for execution. The other load-and-go translators initiate execution of this machine code but many translators do not produce the fixed address machine code and produce a semi-compiled, binary symbolic or relocatable form which are closely related to it. Starting from a mixture of source languages it is possible to develop a composite library of special purpose routines as a frequent use for this. The linkers are designed to link together the routines compiled code in this way. It could be regarded as the final stage for a multi-stage translator [31].

#### 3.2 Basic Components of a Compiler

A typical compiler can be divided into two parts that are front-end and back-end. As shown in Figure 10, the front-end is an analyzer that generates an internal representation, which gives correct meanings of the source code. The back-end continually transforms internal representation to the target code. The most important requirement to a compiler is to work correctly which means generated codes must expressing the same effects as specified by the source code.

Figure 10 Compiler components

Before it begins analyzing, the front-end normally tokenizes the source codes program and also identifies program constructs. Moreover, the front-end will verify the input code related semantics to ensure they are correct.

The back-end will generate target instructions. In order to perform this activity, the synthesizer component needs to choose a wide range of available instructions and data addressing formats. One way to optimize execution on the target machine is to perform register allocation. By using this method, variables may frequently be accessed from registers rather than accessed from the slower memory to accelerate program-running time. In order to improve the performance of generated code many other optimization techniques may be used to complete this task. These techniques include constant folding, strength reduction, algebraic simplification, tail recursion elimination, copy/constant propagation, common sub expression elimination, dead code elimination; loop unrolling, leaf procedure optimization, invariant code motion, hardware loop optimization, register coloring, resource-based scheduling and peephole optimizations [30].

#### 3.2.1 Source Handling

One of the most important issues for a compiler is to detect as many program errors as possible in running. Thus, source handling becomes very important and its function is to process source code and to supply the lexical analyzer with an input stream of characters from the source code. As a very important feature, a source handler normally includes a suitable interface to report syntax errors. Since the incorrect program fragments have been reported on a regular basis, the source handling would ensure that a diagnostic message reporting correctly. As a matter of fact, most of the errors could be detected in a single compiler run [32].

#### 3.2.2 Lexical Analysis

The lexical scanner plays a very important role in lexical analysis. In order to identify the words, the lexical scanner takes the sequence of characters and it must obey the common rule that a user is not allowed to use system-reserved words as user defined identifiers. For example, a C lexical scanner will identify the string void which is a reserved word as a keyword, as a result, we cannot use void as a user identifier. However, the string Number\_of\_CPU is not a language-reserved word so it would be identified as a user declared identifier such as variable, constant, type name, etc.

Tokens may finally be represented by an integer sub-range. Lexical scanners usually attempt to determine the longest symbol to match a token. For instance, string "==" could have been interpreted as two "=". However, because the lexical scanner will use it's rule to determine the longest string, it is matched as "==". Therefore, the string "int\_number" will be interpreted as a user declared identifier but not be interpreted as two identifiers. One of the identifier is the reserved word int, and the other identifier is a user declared identifier\_number.

From a language design point of view, certain scanners are not only performing above-mentioned functions but also requiring to providing context sensitive

information. As in C or C++, the scanner must verify the symbol table in order to distinguish user defined type names with variable names. However, this function cannot be fulfilled correctly by checking the spelling or consequences. More importantly, the symbol table constructed has to be accessed during the semantic analysis stage [32].

#### 3.2.3 Parsing

The parser's functions include recognizing a token or word sequence as a valid sentence in the language. In the mean time, these words are organized in a tree to perform representation of the phrase. There may be two ways for the parser to interface with semantic analysis and code generation routines. As a result of a parser, an explicit parser-tree records the structure of the recognized program. Consequently, semantic analysis and code generation will proceed through this tree.

Another situation is that the parser may at appropriate intervals call semantic analysis and code generation routines directly. In this case, a simple one-pass analysis is sufficient and therefore, an explicit parse tree representation is unnecessary. Calling semantic analysis and code generation routines have the overall effect of traversing a virtual tree from time to time but without the overheads of constructing one [32].

#### 3.2.4 Semantic Processing

Semantic analysis verifies the language components recognized during parsing. It should be emphasized that the language components must have well-defined meanings and do not break any language restrictions. As a matter of fact, most languages impose a declaration before the use of a rule [32].

Many languages also include the ideas of scope rule and declaration blocks. In such block-structured languages, the scope of a symbol is limited to the block within which it is declared. The attributes for an identifier declaration are recorded and each event is subsequently examined. The name analysis via an appropriate symbol table organization to reflect program structure and scope rule as adopted in the language. Type compatibility checks may then be performed. When completing the analysis of a scope, the associated identifier entries may be deleted if they are no longer accessible. For each identifier occurrence, semantic processing would determine if an identifier was declared. If so, locating its declaration will disclose its class, type, and the validity of the current usage. At the end of the semantic analysis phase, the meanings of the program have been determined and code generation may thus proceed.

#### 3.2.5 Code Generation

Code generation is the process of implementing an evaluation procedure for the original source program; for example, a particular target computer or environment. The difficulty of the code generation is relative to the difference between the mechanism and structures in the source language and corresponding availability in the target machine. The first important aspect of code generation is the design of a suitable run-time environment. As a result, the source language features and mechanisms are easily supported and eventually implemented in the target environment. These target environments all have their own special machine architectures, register organizations or addressing formats [33]. Execution of the resultant code must produce the same effects as that specified in the original program. This task engages three steps which are memory mapping, register allocation and instruction selection.

#### 3.3 Parallel Architectures and Compilation Technology

A computational problem may be solved by a set of co-operating processors, workstation networks and other embedded systems. The computational resources, processors, memory, input and output bandwidth are collected together. The parallel approach splits the task into smaller subtasks and works simultaneously by coordinated and efficient workers. The granularity of subtasks should be optimized to find a balance between the number of subtasks and the communication frequency.

The computer architectures can be classified as serial and parallel architectures according to the Flynn's taxonomy [34], [35]. The concepts, instruction stream and data stream are the basis of this classification. A computer is operated by a series of instruction sequence and date stream. A data stream is a sequence of data which is manipulated by the instruction stream. There are four categories of combination of instruction stream and data stream but there are no practical examples of the MISD (Multiple Instruction and Single Data) case. SISD (Single Instruction, Single Data): Most of the serial computers belong to this class. Computers of this class can decode only a single instruction in unit time although instructions can be pipelined. Under the direction of a single control unit, a SISD computer may have multiple functional units. SIMD (Single Instruction, Multiple Data): Vector processors and processor arrays belong to this class. A processor array contains many arithmetic-processing units and each one is able to fetch and manipulate its own data as well as execute a single stream of instructions. Multiple processing units manipulate different data and a single operation is in the same state of execution in any time unit. MIMD (Multiple Instruction, Multiple Data): Most multi-computers belong to this group. Every processor executes its own instruction stream with its data stream.

Memory architectures determine the way of processors' communication, so that they can affect writing parallel programs. There are three primary memory architectures that are shared memory, distributed memory and hierarchy of memory. Shared memory is shared between multiple processors although they work independently, but only one processor at a time accesses the shared memory which is synchronized. The bandwidth of memory is limited by the access speed; if the number of processors is small, it will be fast. The increasing number of processors is dependent on the increasing of bandwidth. Distributed memory: Each of the multiprocessors operates with its own memory independently and data is shared through a communication network and synchronized through message passing. Hierarchy of memory is a combination of shared and distributed memory architecture that contains several shared nodes interconnected by a network. The inter-processor communication is required to transmit data and information between processors and synchronizes node activities.

To program parallel computers, the common approaches are message passing and data passing. Message passing means that each processor has its private local memory, and cooperation is obtained by exchanging messages. A 'receive' operation matches a 'sent' operation. The message passing programming is conducted by linking and making calls to libraries which manage data exchange between processors. The three message passing parallel libraries will be discussed later, they are message passing interface, parallel virtual machine, and message passing library. Data parallel means that data is distributed across processors. Each processor works on a different part of the same data structure. All passing messages are generated by a compiler and they are invisible to the programmer; they are commonly on the top of the message passing libraries. A program is written by using data parallel constructions and compiled by a data parallel compiler, the program is compiled into a standard code with a message passing library call. The High Performance Fortran (HPF) and Connection Machine Fortran (CMF) are two examples of data parallel languages and will later be discussed.

The Parallel programming necessitates a different approach for solving problems; this approach is distinguished from sequential algorithms. There are four distinct stages: Partitioning, Communication, Agglomeration and Mapping (PCAM) in the process of designing a parallel application. I. Foster described them in [34] as follows:

- Partitioning: It decomposes the computation and the data operation into small tasks. We can use domain or functional decomposition in the partition step.

The number of processors in the target computer is ignored. Attention is focused on recognizing potentials for parallel execution.

- Communication: This determines the communication, which is required to coordinate the task execution. It chooses the algorithm and the appropriate communication structure.

- Agglomeration: These are the structures of communication and task, determined in the first and second design stages. They are estimated and evaluated according to the performance requirements and implementation costs to decide whether the tasks must be necessary combined.

- Mapping: The full processor utilization and less communication costs are the goals to be obtained for each task design.

#### Message Passing Programming

The parallel programming model generously used today perhaps is message passing. It creates multiple tasks; a unique name and local data encapsulated identify every task. Send to and receive the messages from the named tasks make the tasks interacting. The programs in the message passing model are written in common high-level languages like C or Fortran.

Several message-passing libraries are widely used today. Programs call library routines to send and receive messages.

#### Parallel Virtual Machine (PVM)

The feature of PVM is that this library can be used in a heterogeneous hardware environment but communication is slower than the other two following libraries. Some modern features such as dynamic task creation and groups have been implemented. Today, there is a public domain message passing library and nearly all hardware platforms are implemented. Originally, it was developed at the Oak Ridge National Laboratory for clusters of workstations [35].

#### Message Passing Interface (MPI)

This is a standardized library and is widely used. MPI is available for many hardware platforms and is promising since the number of tasks is fixed while a program is executing unlike PVM.

#### Message Passing Library (MPL)

Message Passing Library was developed by IBM for the SP-2 supercomputer as a native library and is highly optimized for it. MPL has a similar function to the MPI. In the new version of its operating system and parallel environment of SP-2 it resembles the MPI. It seems as though the IBM supporting MPI and the MPL will be replaced by it [35].

#### **Data Parallel Programming**

Data parallelization is another commonly used parallel programming model. It is derived from the application to multiple elements of a data structure. An example is to add the same number to all elements of an array. A sequence of such operations is contained in a data parallel program. Each operation of the data element is an independent task. The natural units of a data parallel program are small. The programmer should provide explanation for how tasks are partitioned, and how data are distributed over processors. Then a normal programming language C or Fortran are translated from the data parallel program with calls to a message passing library or communication through shared memory.

The following two data-parallel languages, based on Fortran, are widely used:

High Performance Fortran (HPF)

HPF is a well-standardized language [36]. Many commercial High Performance Fortran compilers are available. A public one is called Adaptor. The Fortran 90 syntax plus High Performance Fortran data distributing directives and some new language constructs are included.

Connection Machine (CM) Fortran

Connection Machine Fortran was developed for the Connection Machine originally and now spread away and its architecture is independent [37].

#### 3.4 Lcc Retargetable Compiler Basic Components Introduction

Lcc is an open-source ANSI-C compiler developed by C.W. Fraser and D.R. Hanson [38]. Lcc has been ported to several machine platforms such as Alpha/OSF, x86/Win32, x86/Linux, Sparc/Solaris, and MIPS/IRIX. In this project, we use lcc as the base for our DLX compiler since lcc has been widely used and it is simple.

The compilation flow of lcc can be summarized in Figure 11.

Figure 11 Lcc C compilation flow [38]

Lcc is developed under traditional compiler techniques. The front-end is responsible for lexical, syntactic, and semantic analysis as well as performs some machine independent optimizations. As a matter of fact, both the lexical analyzer and the recursive-descent parser are hand-written programs [38].

The front-end is target-independent but the back-end is target-dependent. An efficient interface packages the front-end and the back-end to be a single program. This interface includes several shared data structures, functions and a DAG language. Examples of interface functions are: emit function prologue, define global, emit data, etc. The DAG language encodes the executable code from a source program by using a smaller language than typical intermediate language which is similar to what is used in other compilers. The authors wrote the lexical scanner and parser programs by hand. These programs are smaller and more efficient than a lex and yacc based on implementation which are tools used to generate lexical analyzers and parsers [30]. First, a C program is translated into syntax trees by the scanner and the parser. Second, from DAG, the syntax trees will be translated into lcc's intermediate representation (IR). In order to simplify

the code generation, the DAGs will be decomposed into trees. Finally, code generation and register allocation will be performed on the trees.

Lcc's code-generator generator is called *lburg* and is based on a dynamic programming algorithm. With the fragment patterns of individual instructions, *lburg* maps the program's IR trees and chooses the most suitable matches consistent with the overall tiling cost of the tree. Furthermore, the algorithm can generate an optimal matching for the IR trees in linear time. One of the features worth mentioning is that the lcc's register allocator uses a simple labeling method that does not utilize graph coloring.

Lcc's back-end is its most interesting part since it shows the results of the design choices that were made to enhance retargetability. Lcc is smaller than the other open source compilers such as gcc [39], and is quicker than gcc. However, the quality of lcc's generated code is lower since lcc does not make extensive back-end code optimization. The code size and execution speed of the lcc-generated code is lower than gcc generated code by an average of 10% [40].

In this project, we selected porting lcc to DLX generally because it's small and easy to implement. It would be much more difficult to port other compilers such as gcc. Our research group needed the C-DLX compiler to test our multiprocessor SoC platform when we began this project. In other words, we are not compilation technology specialists; porting lcc is a first start before we explore more compilers.

# Chapter 4 Main Challenges in NPs Compilation and Related Work

The most popular usage of network processors is employed as a traffic manager in switches, routers and other network equipments to manage the data packet stream. The traffic manager checks, adds and modifies header of PDUs and puts PDUs in a queue according to PDUs priority weight if necessary. The routing and time schedule are also made by the traffic manager [2].