## Université de Montréal

# ESys.Net A New .Net Based System-Level Design Environment

par

James Lapalme

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

Maîtrise présentée à la Faculté des études supérieures en vue de l'obtention du grade de Maître ès sciences (M.Sc.) en Informatique

> Décembre, 2003 © James Lapalme, 2003

QA 76 U54 2004 V.008

#### Direction des bibliothèques

#### **AVIS**

L'auteur a autorisé l'Université de Montréal à reproduire et diffuser, en totalité ou en partie, par quelque moyen que ce soit et sur quelque support que ce soit, et exclusivement à des fins non lucratives d'enseignement et de recherche, des copies de ce mémoire ou de cette thèse.

L'auteur et les coauteurs le cas échéant conservent la propriété du droit d'auteur et des droits moraux qui protègent ce document. Ni la thèse ou le mémoire, ni des extraits substantiels de ce document, ne doivent être imprimés ou autrement reproduits sans l'autorisation de l'auteur.

Afin de se conformer à la Loi canadienne sur la protection des renseignements personnels, quelques formulaires secondaires, coordonnées ou signatures intégrées au texte ont pu être enlevés de ce document. Bien que cela ait pu affecter la pagination, il n'y a aucun contenu manquant.

#### NOTICE

The author of this thesis or dissertation has granted a nonexclusive license allowing Université de Montréal to reproduce and publish the document, in part or in whole, and in any format, solely for noncommercial educational and research purposes.

The author and co-authors if applicable retain copyright ownership and moral rights in this document. Neither the whole thesis or dissertation, nor substantial extracts from it, may be printed or otherwise reproduced without the author's permission.

In compliance with the Canadian Privacy Act some supporting forms, contact information or signatures may have been removed from the document. While this may affect the document page count, it does not represent any loss of content from the document.

## Université de Montréal Faculté des études supérieures Ce mémoire intitulé :

# ESys.Net A New .Net based System-Level Design Environment

présenté par :

James Lapalme

a été évalué par un jury composé des personnes suivantes :

Dr. Houari Sahraoui président-rapporteur

Dr. Jean-Pierre David directeur de recherche

Dr. El Mostapha Aboulhamid codirecteur

Dr. Gabriela Nicolescu membre du jury

Mémoire accepté le 23 mars 2004

#### Sommaire

Avec l'arrivée des systèmes embarqués qui incorporent un nombre croissant de composantes logicielles, il devient plus critique que jamais de rétrécir l'écart qui existe entre la modélisation de niveau système et l'implantation.

Dans ce travail nous illustrons, par le développement d'un nouvel environnement de modélisation et simulation basé sur le langage de programmation C#, le potentiel insoupçonné de modélisation matérielle/logicielle du .Net Framework, potentiel qui a permis de pousser SystemC au-delà de ses limites.

Notre environnement, appelé ESys.Net, utilise les concepts de programmation avancés de .Net et C# tels que la réflectivité, la programmation par attribut et la création dynamique de délégués, afin de créer un environnement plus polyvalent que SystemC.

ESys.Net a pu bénéficier de plusieurs constructions puissantes du génie logiciel en raison de l'utilisation de .Net comme base. Les résultats expérimentaux que nous avons recueillis démontrent que ces constructions n'entraînent pas de pénalités d'exécution significatives.

Mots clés: modélisation, .Net, C#, simulation, système-sur-puce, langages de description, SystemC

# **Abstract**

The need to bridge the gap between system level and implementation level modeling is becoming critical as embedded systems incorporate more software components. Through this work we illustrate, by developing a new modeling and simulation environment, how we can use the .Net Framework through the use of the C# programming language to model hardware/software systems and alleviate the different shortcomings of C++ that are hindering the evolution of SystemC.

Our environment, called ESys.Net, uses the advance programming features of .Net and C# such as reflection, attribute programming and dynamic delegate creation to produce a flexible solution that is meant to be an evolution of SystemC.

By using .Net as a basis for ESys.Net, we have inherited many powerful software engineering constructs. The experimental results that we have gathered demonstrate that these constructs do not incur a significant performance penalty.

Keywords: modelling, simulation, .Net, C#, description languages, system-on-chip, SystemC

# **Table of Contents**

| Sommaire     | *************************************** | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|--------------|-----------------------------------------|----------------------------------------|

| Abstract     | *************************************** | ii                                     |

| Table of Co  | ntentsntents                            | ii                                     |

| Figure List  | *************************************** | vii                                    |

| Table List   | *************************************** | viii                                   |

| Code Exam    | ple Listple                             | ix                                     |

| Abbreviatio  | n List                                  | xi                                     |

| Acknowledg   | gements                                 | xiii                                   |

| Preface      | *************************************** | xiv                                    |

| Introduction | n                                       | 1                                      |

| 1.1 HL       | OLs and SDLs                            | <i>1</i>                               |

| 1.2 Spe      | ecific Goals                            | 4                                      |

| 1.3 Ou       | utline of this Document                 | 5                                      |

| Chapter 2    | State of the Art                        | 6                                      |

| 2.1 Sta      | andalone Languages                      | 6                                      |

| 2.1.1        | VHDL[31]                                | 7                                      |

| 2.1.2        | Verilog                                 | 8                                      |

| 2.1.3     | SystemVerilog [54]                                 | 8  |

|-----------|----------------------------------------------------|----|

| 2.2 P     | rogramming Language-based HDLs                     | 9  |

| 2.2.1     | Handel-C and OCAPI [7]                             | 9  |

| 2.2.2     | JHDL [5] [28]                                      | 9  |

| 2.2.3     | SpecC [59]                                         | 10 |

| 2.2.4     | SystemC [65]                                       | 10 |

| 2.3 N     | lew Challenges in Modeling and Design              | 11 |

| 2.4 R     | ecent Software Frameworks                          | 12 |

| Chapter 3 | Advanced Programming Features with C# and the .Net |    |

| Framewor  | k 15                                               |    |

| 3.1 T     | he .NET Framework                                  | 15 |

| 3.1.1     | General Presentation of .NET Framework [49]        | 16 |

| 3.2 T     | he C# Language                                     | 17 |

| 3.3 A     | dvanced Programming Features                       | 18 |

| 3.3.1     | Introspection and Reflectivity[22] [41]            | 18 |

| 3.3.2     | Attribute Programming[50] [41]                     | 21 |

| 3.3.3     | Delegates                                          | 23 |

| 3.3.4     | Delegates and Reflectivity                         | 25 |

| Chapter 4 | ESys.Net                                           | 27 |

| 4.1 A     | Simple Example                                     | 27 |

| 4.2 N     | Modules and Module Hierarchies                     | 32 |

| 4.2.1     | Module Declaration                                 | 33 |

| 4.2.2     | Module Instancing                                  | 34 |

| 4.2.3     | Module Hierarchies                                 | 34 |

| 4.2.4     | Module Interfaces                                  | 35 |

| 4.2.5     | Modules Inner-Workings                             | 36 |

| 43 P      | Processes                                          | 38 |

| 4.3.1     | Process Declaration and Registration                | 38 |

|-----------|-----------------------------------------------------|----|

| 4.3.2     | Static and Dynamic Process-Event Association        | 39 |

| 4.3.3     | Process Static Sensitivity                          | 40 |

| 4.3.4     | Parallel Method Process                             | 41 |

| 4.3.5     | Process Method                                      | 42 |

| 4.4 Sign  | nals                                                | 45 |

| 4.4.1     | Signals and Simulation                              | 46 |

| 4.4.2     | Instancing                                          | 46 |

| 4.4.3     | Inner and Outer Signals                             | 47 |

| 4.4.4     | A Signal's Logical Scope                            | 47 |

| 4.4.5     | Special Binding Cases                               | 49 |

| 4.5 Por   | ts and Interfaces                                   | 51 |

| 4.5.1     | The Elimination of Ports                            | 52 |

| 4.5.2     | Predefined Interfaces                               | 53 |

| 4.6 Eve   | nts                                                 | 55 |

| 4.6.1     | Event Occurrence.                                   | 55 |

| 4.6.2     | Event Notification [63]                             | 56 |

| 4.6.3     | Multiple Simultaneous Event Notifications [63] [24] | 57 |

| 4.6.4     | Cancelling Event Notifications                      | 58 |

| 4.6.5     | Events, Signals and Clocks                          | 58 |

| 4.7 Cha   | innels                                              | 58 |

| 4.7.1     | Channel Declaration and Instancing                  | 59 |

| 4.7.2     | Channels and Software Interfaces                    | 60 |

| 4.7.3     | Sensitivity                                         | 61 |

| 4.7.4     | Channel hierarchies and inner-workings              | 61 |

| 4.7.5     | The IDeltaUpdatable Interface                       | 61 |

| 4.7.6     | Unification of the Channel Concept [63] [24]        | 62 |

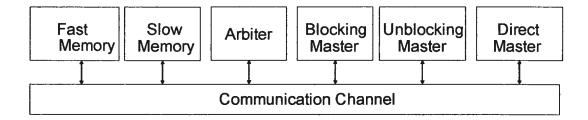

| 4.7.7     | Example [65] [24]                                   | 62 |

| Chapter 5 | Simulation Kernel                                   | 64 |

| 5.1     | Modeling Directives                     | 65  |

|---------|-----------------------------------------|-----|

| 5.2     | Simulation Semantics                    | 66  |

| 5.2     | 2.1 SystemC [64] [63]                   | 66  |

| 5.2     | 2.2 ESys.Net                            | 68  |

| Chapte  | r 6 Comparison and Experimental Results | 77  |

| 6.1     | Advantages of the Environment           | 77  |

| 6.1     | .1 Semantic Simplification              | 77  |

| 6.1     | .2 Programming Simplification           | 79  |

| 6.1     | .3 A Simpler Better Framework           | 80  |

| 6.2     | Disadvantages of the Environment        | 85  |

| 6.3     | Experimental Results                    | 85  |

| 6.4     | Summary                                 | 89  |

| Chapter | r 7 Summary and Future Work             | 92  |

| 7.1     | Summary                                 | 93  |

| 7.2     | Where Do You Go From Here?              | 94  |

| Referen | ıces                                    | 95  |

| Annex A | A Fifo Channel Example                  | i   |

| Annex 1 | B Simple Bus Example                    | ii  |

| Annex ( | C My First System Example               | iii |

# Figure List

| Figure 1:   | Simple circuit                      |    |

|-------------|-------------------------------------|----|

| Figure 2:   | My First System                     | 28 |

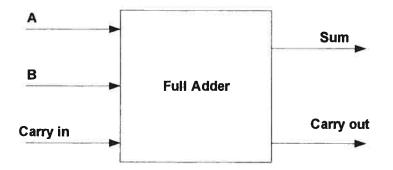

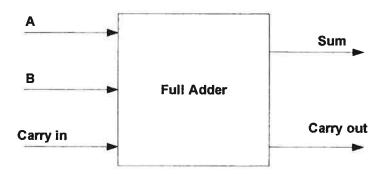

| Figure 3:   | Full Adder Module Interface Example | 36 |

| Figure 4:   | One Bit Adder Example               | 37 |

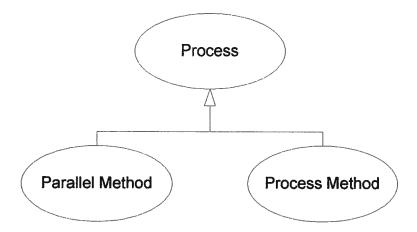

| Figure 5 :  | Process Sub-Types                   |    |

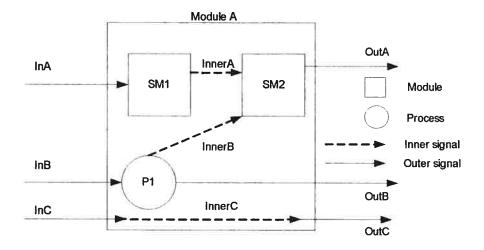

| Figure 6 :  | Inner/Outer Signals                 | 48 |

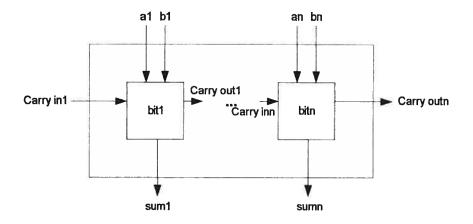

| Figure 7 :  | A N bit Adder                       | 54 |

| Figure 8 :  | Event Occurrence                    | 56 |

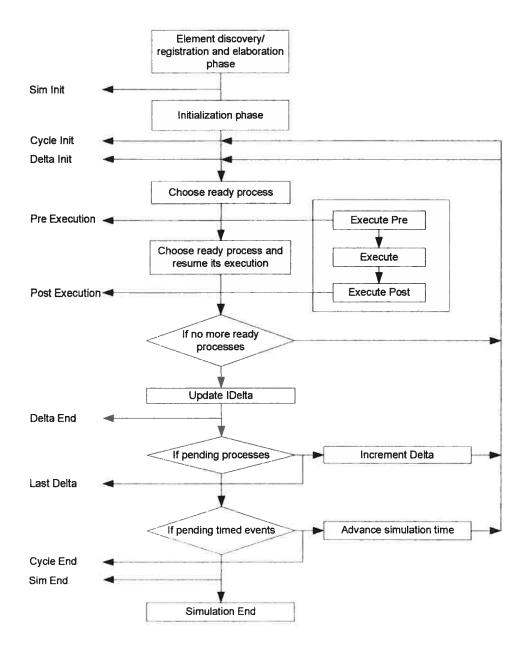

| Figure 9 :  | SystemC's scheduler structure       | 68 |

| Figure 10 : | ESys.Net Scheduler Steps            | 75 |

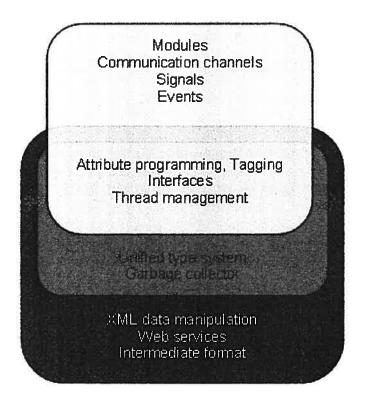

| Figure 11 : | Leveraging of existing features     | 81 |

| Figure 12 : | General view of the application     | 87 |

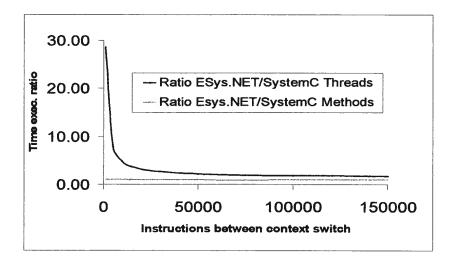

| Figure 13:  | ESys.Net versus SystemC performance | 88 |

# Table List

| Table I :   | Metadata Classes                                         | 19 |

|-------------|----------------------------------------------------------|----|

| Table II :  | Interfaces                                               | 54 |

| Table III : | Event non-determinism                                    | 57 |

| Table IV :  | Attributes and their role in ESys.Net                    | 65 |

| Table V:    | Summary of the Advantages and Disadvantages over SystemC | 89 |

# Code Example List

| Code example 1:  | Type Introspection                             | 20 |

|------------------|------------------------------------------------|----|

| Code example 2:  | Value Modification with reflection             | 21 |

| Code example 3:  | Attribute programming example                  | 22 |

| Code example 4:  | Simple delegate example                        | 24 |

| Code example 5:  | Delegate example                               | 24 |

| Code example 6:  | Event keyword example                          | 25 |

| Code example 7:  | Delegates and reflection                       | 26 |

| Code example 8:  | ModuleA blueprint                              | 29 |

| Code example 9:  | ModuleB blueprint                              | 29 |

| Code example 10: | MyModule blueprint                             | 30 |

| Code example 11: | MyFirstSystem                                  | 31 |

| Code example 12: | MyApp                                          | 32 |

| Code example 13: | General module declaration                     | 34 |

| Code example 14: | Module instantiation                           | 34 |

| Code example 15: | Module hierarchy                               | 35 |

| Code example 16: | FIFO declaration                               | 36 |

| Code example 17: | Adder implementation                           | 37 |

| Code example 18: | Process method and Parallel method declaration | 39 |

| Code example 19: | Static Sensitivity                             | 40 |

| Code example 20: | Static Sensitivity with multiple events names  | 41 |

| Code example 21: | PMethod Dynamic Sensitivity                    | 42 |

| Code example 22: | Process Method dynamic sensitivity             | 43 |

| Code example 23: | Triggering on a single event                   | 44 |

| Code example 24: | Triggering after a specific amount of time     | 44 |

| Code example 25: | Triggering with zero time                                 | 44 |

|------------------|-----------------------------------------------------------|----|

| Code example 26: | Triggering on one event in a list of events               | 44 |

| Code example 27: | Triggering on all events in a list of events              | 45 |

| Code example 28: | Triggering on an event in a list of events with timeout   | 45 |

| Code example 29: | Triggering on all Events in a list of events with timeout | 45 |

| Code example 30: | Signal Instancing                                         | 47 |

| Code example 31: | Inner/Outer signals                                       | 49 |

| Code example 32: | Special signal binding cases                              | 51 |

| Code example 33: | Boolean software interfaces                               | 53 |

| Code example 34: | Event instantiation                                       | 55 |

| Code example 35: | Event notifications                                       | 57 |

| Code example 36: | Channel declaration                                       | 59 |

| Code example 37: | Channel instantiation                                     | 60 |

| Code example 38: | IDeltaUpdatable interface                                 | 61 |

| Code example 39: | RequestUpdate method                                      | 62 |

| Code example 40: | Model Discovery and Registration                          | 70 |

| Code example 41: | Process dicovery and verification                         | 70 |

| Code example 42: | Algorithm part for process methods                        | 71 |

| Code example 43: | Algorithm part for parallel methods                       | 72 |

| Code example 44: | Algorithm part for callback hooking                       | 73 |

| Code example 45: | Tool hooking                                              | 76 |

| Code example 46: | Metadata (priority)                                       | 79 |

| Code example 47: | Signal Discovery method                                   | 83 |

| Code example 48: | Printing method                                           | 84 |

| Code example 49: | Tool hooking                                              | 84 |

| Code example 50: | Context switch verification                               | 87 |

0

# **Abbreviation List**

| Computer Assisted Design                                          |

|-------------------------------------------------------------------|

| Common Intermediate Language                                      |

| Common Language Infrastructure                                    |

| Common Language Specification                                     |

| Common Type System                                                |

| European Computer Manufacturers Association                       |

| Electronic Design Automation                                      |

| Electronic Design Interchange Format                              |

| First In, First Out                                               |

| Field-Programmable Gate Arrays                                    |

| Hardware Description Language                                     |

| Integrated Circuit                                                |

| Institute of Electrical and Electronics Engineers                 |

| Intellectual Property                                             |

| International Organization for Standardization                    |

| Java Virtual Machine                                              |

| Network On Chip                                                   |

| Object-Oriented Programming                                       |

| Open SystemC Initiative                                           |

| Printed Circuit Board                                             |

| Register Transfer Level                                           |

| SystemC Verification Library                                      |

| System Description Language                                       |

| SpecC Technology Open Consortium                                  |

| University of California Irvin                                    |

| Virtual Execution system                                          |

| Very High Speed Integration circuit Hardware Description Language |

| Extensible Markup Language                                        |

|                                                                   |

I would like to dedicate this to my mother and father who have always pushed me to better myself, and to Zachary and Marie-Josée, the two loves of my life, without whom this would have no meaning

# Acknowledgements

Above all, I would like to thank El Mostapha Aboulhamid, the initiator of the ESys.Net project, without whom there would be no ESys.Net. Thank you for believing in me and being very patient, your wisdom was invaluable.

I would like to thank Jean-Pierre David for his help and support.

I wish to express my gratitude to Luc for helping me with the design and for putting up with my endless babbling.

Also, I would like to thank my Mom, Bruce, Irene, Dan, Marie-Josée, Steven and Gabriela for their important contributions.

I especially would like to thank Marie-Josée, my soul mate, for her constant support and patience. I would not have made it without you.

James Lapalme

# **Preface**

The need to bridge the gap between system level modeling and implementation modeling is becoming pressing as embedded systems incorporate more software components. Maybe a change of paradigm is needed for hardware and system modeling?

Most current hardware description languages have two significant advantages over generic programming language: syntactic brevity for hardware semantics and better constructs for model verification. However even these advantages are melting away with the emergence of languages like Asml. Even SystemC, a C++ based solution, has been able to incorporate fairly simple syntactic constructs -through the use of macro- to provide hardware semantics. Assertion based verification capabilities have usually only been supported by hardware description languages and specialized verification languages but generic programming languages are beginning to incorporate those capabilities such as Eiffel and Asml.

The major limiting factor of using generic programming languages for hardware modeling is that hardware semantics are not directly present. But what if we could add the missing metadata? What could we do if we had the power of certain high level programming languages: the reflective capabilities of Java, the polymorphism of Ruby, the elegance of ML, or the simple power of Perl? Would all of this change the way we think of system modeling and hardware modeling? The .Net Framework currently makes interoperability between languages almost seamless. It also permits the integration of custom metadata.

This thesis presents a new environment called Esys.Net that we have created for system-level modeling and simulation. We developed this solution in response to our

frustrations with SystemC, frustrations caused by (i) the complexities of SystemC's underlying implementation language (C++) (ii) its overly complex library (iii) its complex design that makes custom modifications verify difficult (iv) and especially its lake of third-party tool integration capabilities. When we first started developing ESys.Net, our main objective was simply to port SystemC to the .Net Framework in order to eliminate certain of SystemC's downfalls. However, as the project advanced, we rapidly discovered the full potential of the .Net Framework and the C# programming and decided to re-engineer SystemC in order to take full advantage of the underlying technologies. We added many new features to the overall design of the new environment in order to create a solution meant to be an evolution of SystemC.

#### Introduction

For many years now, the ever growing gap between the available computing power offered by hardware platforms and that used by the software applications running on these platforms has been tolerated because of the need for platform independent software, independence required because of the difference in life expectancy between hardware and software products. Today, with the emergence of embedded systems, it is imperative that these new systems take full advantage of the computing power available on the underlying hardware platform and that a perfect balance may be reached between software and hardware.

A major hurdle limiting the production of better systems, especially embedded ones, is the existence of an annual 30% gap between the growth of chip complexity and human design productivity [27]. To overcome this design crisis, it is clear that sophisticated CAD tools and new design methodologies are necessary to help designers model, simulate, partition and verify complex hardware/software systems. Over the past several years, many researchers have looked towards the creation of better design environments integrating powerful tools for system modeling, simulation, partitioning and verification [44].

#### 1.1 HDLs and SDLs

Before Moore's law [48] pushed the elaboration of hardware systems by a single individual out of the realm of reality, systems were developed in an almost artistic way by electronic engineers. When systems became overly complex, tools were created to help teams communicate various aspects of a hardware design [47]. The first tools available were called Hardware Description Languages (HDLs) and were a spin-off of programming languages. A good overview of an HDL is [67]:

"In electronics, a hardware description language or HDL is a standard text-based format for describing either the behaviour or the structure, or both, of an electronic circuit. Most HDLs are restricted to describing digital circuits, but there are exceptions. HDLs have two purposes. First, they are used to write a model for the expected behaviour of a circuit before that circuit is designed and built. The model is fed into a computer program, called a simulator, that allows the designer to verify that his solution behaves correctly. Second, they are used to write a detailed description of a circuit that is fed into another computer program called a logic compiler. The output of the compiler is used to configure a programmable logic device that has the desired function. Often, the HDL code that has been simulated in the first step is re-used and compiled in the second step."

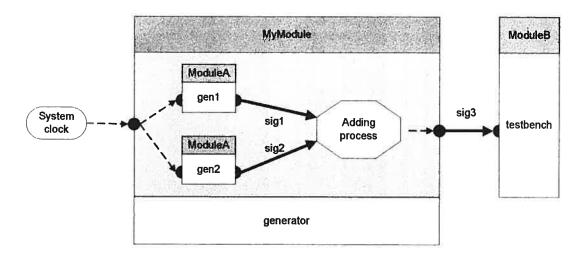

The basic difference between an HDL and a traditional imperative programming language is the presence of a certain number of modeling semantics:

- Parallel processing elements (e.g. process)

- Timing constraint elements (e.g. clock, time)

- Structural decomposition elements (e.g. modules)

- Interconnection elements (e.g. signals)

- Ports

There exists no formal document that describes the modeling semantics of an HDL but current examples support the above modeling elements even though there syntax or name may differ. Figure 1 illustrates some of the above concepts on a circuit schematic.

Figure 1: Simple circuit

Because of the advances in electronic component interconnections, the concept of HDLs has been extended in recent years with the semantics of communication channels that permit the modeling and abstraction of complex communication mediums. These new tools are called System-Level Description Languages (SDLs) [59].

The industry and academics have for several years tried to create better HDLs and SDLs to aid with the never ending design crisis. One method that has been explored for the creation of these tools (HDLs and SDLs) is a library-based approach which consists of taking an existing programming language and adding to it the missing constructs and semantics for hardware and system design [7]. A second approach is a standalone one consisting of the simple creation of a new language.

Despite all these efforts, system designers still need new modeling and simulation solutions. This is mainly due to a mandatory set of requirements for an efficient modeling and simulation framework which are still not provided by a single existing environment:

- Easier software components specification and their integration into an overall

Hardware/software system specification [66];

- Clean programming features to enable less error-prone models, easier specification for complex systems and reuse of such specification for further designs [62];

- Introspection features for easier debugging and analysis of complex systems

[36] [22].

- Possibility of annotating models for different purposes, e.g. directing synthesis

or hooking to verification tools, creating user friendly HDL syntax [50];

- Translation to a standard intermediate format to enable the design of CAD tools independently of the used description languages [40];

- Integration to distributed web-based design environment and easy system documentation to facilitate cooperation between different design groups and to allow remote processing [14];

- Multi-platform and multi-language features for describing and designing the overall embedded systems composed of heterogeneous components [34];

- Easier memory management to accelerate the specification process and to eliminate an important source of errors [54].

# 1.2 Specific Goals

The SystemC [65] modeling environment has been gaining momentum for the past several years and has become a de facto standard for systems-level modeling. However, because its underlying implementation is based on C++, its evolution is rapidly slowing down. We believe that SystemC will have grave difficulties in keeping up with new environments, which will incorporate many advance system-level modeling features for operating system and hardware/software system modeling [44] [3]. The existence of an environment such as SystemC is very important because it is one of the few good modeling and simulation environments that is "free" and "open source". Most current environments are products developed and sold by big corporation that are demanding high licensing fees.

The objective of this thesis is to propose an environment for system-level design that (1) provides most of the concepts present in high-level modeling and simulation solutions, (2) respects all the requirements enumerated above and (3) preserves comparative performances with existing environments, by using C# and the .Net Framework.

The mission of our environment is to use the proven environment of SystemC as a basis for a new solution that will also be "free" and "open source". Our environment brings to the hardware/software modeling community a new solution that has all the benefits of SystemC without having most of its drawbacks. We hope that our solution will offer designers a good alternative to expensive proprietary solutions.

#### 1.3 Outline of this Document

Chapter 2 gives an overview of the different environments available for the modeling and simulation of hardware/software systems. It presents a brief introduction of the new challenges facing system designers today and in the future. It also presents current software frameworks that might help in solving these new problems.

Chapter 3 presents the .Net Framework and the C# programming languages. It then goes on to explain the advanced programming features that these two technologies support which have permitted us to create a new system-level design environment called ESys.Net.

Chapter 4 highlights the various elements that make up the ESys.Net framework. They are presented individually, their semantics explained and their uses illustrated. Many code examples are given to help the reader understand the subtleties of the environment.

Chapter 5 is entirely dedicated to our simulation kernel, since the major design differences between SystemC and ESys.Net are in the simulation kernel. This chapter gives descriptions and compares the design of both environments.

Chapter 6 discusses the advantages and disadvantages of the ESys.Net environment; some experimental results are presented also.

Finally, chapter 7 summarizes the project and suggests directions for further research.

# Chapter 2 State of the Art

The complexity of reality surpasses greatly our capability of synthesis and analysis. To cope with this inadequacy, we simplify things in order to create models that we can manipulate and understand. Hardware system design and the new area of hardware/software system codesign are domains that we definitely cannot cope with without simplification and abstraction. These domains are plagued by an ever growing complexity fed by technological advancements and new consumer needs.

To simplify and model these complex systems, hardware description languages have been used for about 40 years now [12] [6]. They became widely used with the adoption of VHDL as an IEEE standard in 1987. There are two classes of HDLs. Standalone HDLs have their own syntax, compilers and analyzers, whereas HDLs that are in fact libraries are based on existing programming languages such as C++, C or Java. Each approach has pros and cons as we will illustrate in the following sections. We will show how recent developments in the software domain, by the introduction of new frameworks, can help in the domain of hardware/software codesign. These languages permit the description of systems in a clear and standard way, permitting the easy exchange of information between people.

# 2.1 Standalone Languages

This first class of HDLs is composed of languages that were developed from scratch for the sole purpose of hardware and hardware/software systems modeling. The vast majority of these were developed by the industry for the industry.

# 2.1.1 VHDL[31]

The development of VHDL was initiated in 1981 by the United States Department of Defence to address the hardware life cycle crisis [16]. VHDL was meant (i) to provide a unified notation for describing electronic systems at various levels of abstraction, (ii) to be both machine and human readable, (iii) to support the communication of design data, (iv) to aid the maintenance, modification and procurement of hardware, and finally (v) to support the development, verification, synthesis and testing of hardware designs through a tool agnostic description. VHDL was a purely hardware description language. Early on designers noticed the absence of software and system primitives such as FIFOs, and system synchronization mechanisms such as semaphores, locks and shared variables, as well as object oriented paradigms which would help with design reuse, Also, VHDL was verbose and not well adapted to describe components which are lower than the gate level. Gate libraries were generally described using in-house scripts. Test benches were also generated using special scripts even though VHDL had many useful constructs to describe test benches. In fact, in some aspects, it is much richer than Verilog or more recent languages such as SystemC in developing gate level and register transfer level (RTL) test benches. Except for basic assertion based verification, VHDL did not provide any other verification capabilities. Some features were very specific to VHDL, such as the possibility of having metadata-like attributes. Metadata is very useful for tools that interpret a model either for simulation, verification, test coverage, test generation, or synthesis. It also has the notion of the separation between the interface of a component (described by an entity) and its functionality which is described by one or more architectures. This separation is unique to VHDL; the community had to wait for recent object-oriented hardware description languages to find similar capabilities. This separation between the interface and the behaviour was very useful in design space exploration and to some extent in design reuse. Another unique feature of VHDL is the concept of resolution functions which allow very well defined protocols to modify a signal by concurrent processes; this allowed the description of very high level modeling of interaction between subsystems. In total,

fifteen different IEEE standards around VHDL have been adopted such as VHDL-AMS [30] for analog design.

#### 2.1.2 Verilog

Verilog was the main competitor of VHDL until the announcement of SystemC in 1999. Even though it appeared in 1985 it became an IEEE standard only in 1995[32]. It is a less verbose language than VHDL but comes with some limitations such as a narrow data type set, a resolution function restricted to "wired or" and "wired and" and no separation between interfaces and behaviour. However, it has better performances and a well defined foreign interface to hook to other languages. Currently, VHDL and Verilog are converging more and more in capability [4].

## 2.1.3 SystemVerilog [54]

SystemVerilog, which was adopted as a standard by Accellera in June 2002, is an extension of Verilog. It can be seen as a stack of components aimed at verification, design and system modeling. For verification, it provides facilities both for test bench generation as well as assertions. For the design aspect, it provides many enhancements to Verilog, such as provision for communication interfaces and an enriched data type set similar to the C programming language. Since SystemVerilog is a new product and very few case studies have been published, simulation performance remains to be seen. Many companies donated different technologies to this environment. The white paper by S. Bailey [3] provides an excellent comparison between VHDL, Verilog and SystemVerilog. In that report we note that features available in VHDL but not in Verilog or vice-versa have been added to SystemVerilog, such as named events, partially strong typing, records and structures, hierarchy, reactive processes, interface abstraction, assertions and foreign interfaces, and system level primitives and mechanisms such as mailboxes, semaphores, dynamic process creation, etc. Some capabilities of VHDL have been omitted or only partially implemented such as operator overloading, general resolution functions, full-fledged attributes, configurations and binding.

# 2.2 Programming Language-based HDLs

The second class of HDLs is based on an existing language such as C++, C or Java. Existing programming languages are usually missing basic hardware description semantics such as concurrent behaviour, timing elements, communications elements etc.; so this second class of HDLs is usually implemented by either providing a framework which adds the necessary missing hardware semantics to the base programming languages or extends the languages with additional syntactic and semantic constructs – a superset approach. These are, with some exceptions, open source environments and commercial tools that are either less evolved or targeted to a specific niche; however, they are very useful in an academic environment. In the following sections we will describe the characteristics of some illustrative examples.

# 2.2.1 Handel-C and OCAPI [7]

Some articles have illustrated the advantages of using HDLs based on existing programming languages [8]. OCAPI is based on C++ and is very efficient at system level exploration while Handel-C is C-based and can generate efficient designs translating them to EDIF or VHDL for implementation on FPGAs. The strength of both environments and their seamless integrations can provide a very strong design flow from system level to FPGA implementation.

# 2.2.2 JHDL [5] [28]

JHDL is an object-oriented environment; it uses exclusively object-oriented constructs of Java for RTL hardware modeling, simulation and efficient implementation on FPGAs. The environment permits the description of synchronous digital logic circuit components and connections such as: static cells, Boolean gates, registers, "parameterizable" modules etc. JHDL was developed as an exploratory attempt to identify the key features and functionalities that a good FPGA tool needs. It has been also recently used for Intellectual Property blocks (IP) delivery through the internet.

## 2.2.3 SpecC [59]

SpecC was developed by the University of California, Irvine (UCI), and first appeared in 1997. In 1999, the SpecC Technology Open Consortium (STOC) was founded. As a result, the SpecC language was refined and extended, leading to its second generation, SpecC 2.0 which was approved by the STOC in December 2002. The SpecC language is a superset of the ANSI-C programming language. It is a formal notation intended for the specification and design of digital embedded systems. SpecC extends C with concepts essential for embedded systems design such behavioural and structural hierarchy, concurrency, communication, synchronization, state transitions, exception handling and timing. SpecC is one of the few existing environments that supporting explicit behavioural hierarchies. It focuses on an IP co-design methodology for modeling and design at the system level. SystemC channel and communication abstractions were inspired from the pioneer work done in SpecC.

# 2.2.4 SystemC [65]

SystemC, announced in September 1999 by OSCI (The Open SystemC Initiative), was met with much enthusiasm by both industry and academia. It was the first open source library approach environment based on C++. It is currently very popular for hardware-software system-level design. It provides all the basic concepts used by HDLs (e.g. modules, ports, signals, timing, etc.) and more abstract concepts (interfaces, communication channels, events, etc.). However, most of the features for software modeling are still missing in SystemC: dynamic process creation, process control (suspend, resume, kill, etc.), pre-emption, software specific communication primitives (monitors, semaphore, etc.). Many companies used SystemC to model in a very efficient way the system aspects of their design. As illustrated in a survey done by Doulos [17] the use of SystemC is mainly performance modeling, architecture exploration, and transaction level modeling and hardware-software co-simulation. The survey also shows that (i) standard HDLs continue to be used for hardware modeling and synthesis, (ii) a minority of users use SystemC for RTL synthesis and (iii) many companies are interested in operating systems and software scheduling

which are not currently available in SystemC 2.0. Given that SystemC 2.0 is in fact a C++ library it lends itself to the development of very sophisticated test benches and as shown in [13], SystemC surpasses largely specialized languages such as the E language or Vera which are meant for verification and test bench development. SystemC was a good catalyst for new contributions, i.e. transaction level modeling to deal with the increased complexity of models, software engineering methodologies for interoperability design reuse [10], simulation of network topologies [43], and functional verification [23]. Finally, it is the first open source HDL for which a language reference manual has been completed in order to submit it for an IEEE standard approval. In 2003 the OSCI announced the SystemC Verification Library (SCV) which added some verification and introspection capabilities to the existing environment [18].

# 2.3 New Challenges in Modeling and Design

Needs have evolved from simply describing hardware at the RTL level to including communicating subsystems, abstracting communication and buses, and dealing with low power and interconnects.

Hardware/software systems are becoming a reality and complexity is increasing at an exponential rate. This rapid growth has pushed many to use third-party IP. Using high quality third-party IPs permits the reduction of design time while improving overall quality and facilitating the design of heterogeneous systems. However, IP reuse also brings different challenges such as:

- Finding effective ways of delivering IPs to customers

- Insuring a sufficient visibility of the IP so that customers may validate custom

models and simulate the complete system containing in-house and IP

components

- Providing the above features while protecting the intellectual property of the vendor.

Another important revolution in the domain of integrated circuits is the integration of non-microelectronic elements on a chip such as micro-optical and micro-mechanical

components. These complex and heterogeneous systems also produce different problems to solve at the modeling and simulation level. We should be able to model and simulate systems expressed using different languages, paradigms, and concerns as well as components described at different levels of abstraction and protection. If we examine the recent modeling and design environments illustrated by SystemC and SystemVerilog, we notice that the concerns are: performance of simulation, ease of programming and debugging. There are also software issues such as operating systems primitives, multithreading, provision for foreign interfaces and increased levels of abstraction, as well as verification needs for the integration of components and the interaction between them. Other concerns which are increasing in importance are power dissipation and the problems related to the shrinking technology going into the nanotechnology.

Through the long history of HDLs we notice the influence of parallel and simulation languages developed in the software domain on the development of HDLs. Verilog was a simile combination of an earlier HDL and Occam parallel-processing language. VHDL was also largely influenced by ADA and Verilog by C syntax. We think we should go a step further to where the hardware modeling will become only one aspect within a general software framework environment. The large success of existing HDLs was the possibility to go from an RTL description to a gate level implementation in a very efficient way. Up until now there have been no convincing success stories accomplished at higher levels of abstraction. Behavioural synthesis is still not adopted by the industry, and commercial tools at that level of abstraction have not been very successful. One success story may be the current transaction level modeling enabled by the introduction of SystemC. The focus seems to be on the combination of modeling and verification on one hand, and development reuse, delivery and integrations of third party IPs.

## 2.4 Recent Software Frameworks

Even the most recent modeling and design environments such as SystemC and SystemVerilog have many shortcomings. These are monolingual environments with limited capabilities of accessing models written in other languages. The error prone

programming and the lack of type-safe features in C++ hamper the development of SystemC. SystemVerilog will not be an open source environment which will be a hurdle to universities in developing and experimenting with CAD/EDA frameworks.

The .NET framework was announced in 2000, one year after the introduction of SystemC. In our opinion, it contains features that would have greatly influenced the language choice for implementing SystemC. Java was not chosen due to its lack of performance compared to C++, the absence of operator overloading and generic classes, etc. If we look at the C# programming language [19] introduced with .NET, we note that all these shortcomings have been removed. An excellent comparison of C#, C++ and Java is given in [2]. It shows how C# takes advantage of the strengths of Java and C++ and blends them in a very powerful and elegant language. The performance of C# is also confirmed by different publications [42]. Many features planned for implementation in SystemC or SystemVerilog are already implemented in an efficient way in C#, such as automatic garbage collection, safe pointers, software multithreading, mailboxes, semaphores, monitors, etc.

In contrast to the JAVA environment and its virtual machine aimed only at JAVA, .NET is a multilingual environment [39] [26], a necessity in the domain of hardware/software modeling and design. It could be very beneficial to explore the capabilities of recent frameworks such as .NET in modeling, verifying and designing hardware/software systems. These frameworks bring many features to be adapted for hardware/software modeling and design such as: safe simulation of models, including models created by an unknown or semi-trusted third party, a consistent object-oriented programming environment whether the model is local or remote [39] [56], increased reuse and multilingual support, and the existence of a published intermediate format that renders lower level tools independent of higher level modeling languages. As we can see, all these features can be applied to development and delivery of IPs, the modeling and simulation of heterogeneous systems as well as the development or integration of modeling, synthesis and verification tools.

We should also benefit from the characteristics of recent software frameworks that are nonexistent in SystemC or SystemVerilog, such as the ability to document a

model using metadata [50], which can be accessed by reflection either to specify the simulation verification or synthesis semantics, the use of reflection to explore a model for verification, test coverage or refinement, and self-contained documentation using standards such as XML.

# Chapter 3 Advanced Programming Features with C# and the .Net Framework

With time HDLs are beginning to integrate many features that we have come to expect of high level programming languages making them much more similar to software programming languages than hardware modeling languages. By using new software development tools and leveraging advanced programming features, improved library-approach HDLs and SDLs can be developed. This section presents two new software development tools, the .Net Framework and the C# programming language. The advanced programming features, supported by these two technologies, which have had the greatest impact on the development of ESys.Net, are also presented.

#### 3.1 The .NET Framework

Virtual machines, intermediate languages and language independent execution platforms are not new. They were present with UNCOL in the 1950's to the JVM in the 1990's. Researchers have been fascinated with these concepts because they permit an alternative path to native compilers that have several benefits [45]:

- Portability: To implement n languages on m platforms, only n + m translators are needed instead of n \* m translators.

- Compactness: Source code is usually much more compact when translated to an intermediate format.

- Efficiency: By delaying the commitment to a specific native platform as much as possible, we can make optimal use of the knowledge of the underlying machine, or even adapt to the dynamic behaviour of the program.

- Security: High-level intermediate code is more amenable to deployment and runtime enforcement of security and typing constraints than low level binaries

- Interoperability: By sharing a common type system and high-level execution environment, interoperability between different languages becomes easier than binary interoperability. Easy interoperability is a prerequisite for multi-language library design and software component reuse.

- Flexibility: Combining high-level intermediate code with metadata enables the construction of (type safe) meta-programming concepts such as reflection, dynamic code generation etc.

The .NET core represented by the CLI (Common Language Infrastructure) is a new virtual machine execution platform which was standardized in December 2001 by ECMA and in April 2003 by ISO [20].

## 3.1.1 General Presentation of .NET Framework [49]

The .NET Framework is a new platform that simplifies component-based application development for the highly distributed Internet environment. What sets the .NET framework apart from its rivals (such as the Java platform) is that its core, the CLI, was designed from the ground up to be a multi-language environment [26] [45] . At the center of the Common Language Infrastructure (CLI) is a unified type system, the Common Type System (CTS), and a Common Intermediate Language (CIL), which supports high-level notions (e.g. classes) and which is platform and programming language independent. The CTS establishes a framework enabling cross-language integration, type safety, and high performance code execution.

The CLI has four main components:

**The Common Type System**. The Common Type System (CTS) provides a rich type system that supports the types and operations found in many programming language families. It is intended to support the complete implementation of a wide range of programming languages

**Metadata.** The CLI uses metadata to describe and reference the types defined by the Common Type System. Metadata is stored ("persisted") in a way that is independent

of any particular programming language. Thus, metadata provides a common interchange mechanism for use between tools that manipulate programs (compilers, debuggers, etc.). Metadata is also used to augment the CIL representation of a source code.

The Common Language Specification. The Common Language Specification (CLS) is an agreement between language designers and framework (class library) designers. It specifies a subset of the CTS Type System and a set of usage conventions. Languages provide their users the greatest ability to access frameworks by implementing at least those parts of the CTS that are part of the CLS. Similarly, frameworks will be most widely used if their publicly exposed aspects (classes, interfaces, methods, fields, etc.) use only types that are part of the CLS and adhere to the CLS conventions.

The Virtual Execution System. The Virtual Execution System (VES) implements and enforces the CTS model. The VES is responsible for loading and running programs written in CIL. It provides the services needed to execute managed code and data, i.e. automatic memory management (Garbage Collection), thread management, metadata management etc. The VES also manages the connection at runtime of separately generated code modules through the use of metadata (late binding).

The CLI also gives the specification number of class libraries providing important functionalities such as thread interaction and reflection. It also provides XML [21] data manipulation, text management, collection functionality, web connectivity, etc.

Alongside the CLI core, .NET Framework presents a set of classes that add supplementary features such as web services, native and web forms, transaction, scalability and remote services, etc.

# 3.2 The C# Language

The C# language is a simple, modern, general-purpose object-oriented programming language that has become an ECMA and ISO standard [19]. It was intended for

developing software components suitable for deployment in distributed environments. Although most C# implementation (Microsoft , Xixiam , DotGNU [46] [15] [55] ) used the CLI standard for its library and runtime support, other implementations of C# need not, provided they support an alternate way of getting at the minimum CLI features required by this C# standard.

In order to give the optimum blend of simplicity, expressiveness, and performance, C# supports many software engineering principles such as strong type checking, array bounds checking, detection of attempts to use uninitialized variables, and automatic garbage collection [2].

C# is intended for writing applications for both hosted and embedded systems ranging from the very large that use sophisticated operating systems, down to the very small having dedicated functions. Although C# applications are intended to be economical with regards to memory and processing power requirements, the language was not intended to compete directly on performance and size with C or assembly language.

# 3.3 Advanced Programming Features

Since the C# language relies on a runtime with the CLI's features; it inherits interesting characteristics such as a unified type system, thread and synchronization support, and automatic memory management just to name a few. It is sometimes hard to separate the C# language and the CLI because they are quite symbiotic so .Net/C# or CLI/C# will sometimes be used throughout this document.

There are three advanced programming features that .Net/C# support that have considerable impact on software design: reflectivity, attribute programming and events/delegates.

# 3.3.1 Introspection and Reflectivity[22] [41]

A program that can explicitly see, understand and modify its own structure is said to have introspective capabilities. Reflectivity is a property that a program may possess that permits its structure to be accessible to itself. The information that is accessible through introspection is called meta-information or meta-data. Meta-data permits the

creation of simple but powerful tools that help the design and development of software such as debuggers, class browsers, object inspectors and interpreters. There exist many languages such as Java and C# that are said to be reflective because they provide meta-information to programs written with them. Most reflective languages implement the reflection property by the means of a supporting run-time like the Java JVM or the .Net CLR, in this way separating the meta-information from the base program.

These concepts are illustrated in the reflection capabilities of the C# programming language where it is possible to query the CLI to know the structure of an object. To such a query, the CLI returns an object that is an instance of a metaclass named Type that fully describes the type. Table I gives a list of the basic classes that make metadata accessible to a program.

Table I: Metadata Classes

| Class           | Description                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------|

| Type            | Represents type declarations: class types, interface types, array types, value types, and enumeration types.    |

| Assembly        | Defines an Assembly, which is a reusable, versionable, and self-describing building block of a CLR application. |

| MethodInfo      | Discovers the attributes of a method and provides access to method metadata.                                    |

| ParameterInfo   | Discovers the attributes of a parameter and provides access to parameter metadata.                              |

| FieldInfo       | Discovers the attributes of a field and provides access to field metadata.                                      |

| PropertyInfo    | Discovers the attributes of a property and provides access to property metadata.                                |

| EventInfo       | Discovers the attributes of an event and provides access to event metadata.                                     |

| ConstructorInfo | Discovers the attributes of a class constructor and provides access to constructor metadata.                    |

| MemberInfo      | Discovers the attributes of a member and provides access to member metadata.                                    |

Code example 1 exemplifies the use of some basic introspection classes to query a class about its members (fields, properties, constructors, methods, etc.)

```

public class TypeIntrospection{

public static void Main() {

Type theType = Type.GetType("Assembly");

MemberInfo[] mbrInfoArray = theType.GetMembers();

foreach (MemberInfo member in mbrInfoArry)

Console.WriteLine("{0} is a {1}", member,

brInfo.MemberType);}}

```

## Code example 1: Type Introspection

### Excerpt of the ouput:

System.String s\_localFilePrefix is a Field Boolean IsDefined(System.Type) is a Method Void .ctor() is a Constructor System.String CodeBase is a Property

In line 3 we get a reference to the "Assembly" type. Line 4 retrieves all the members that are declared in the type. The rest of the code iterates through the members and prints them to the standard output.

Here is a code example that shows the true power of introspection and reflectivity. First, we dynamically discover and change the value of a private field, and then we dynamically discover and invoke an object's method.

```

1. public class MyClass{

private string myString="Old value";

public int MyStringLength(String inputString) {

4.

return inputString.Length ;}}

5.

6. public class FieldInfo SetValue{

public static void Main(){

8.

MyClass myObject = new MyClass();

9.

Type myType = Type.GetType("MyClass");

10.

FieldInfo myFieldInfo = myType.GetField("myString",

11.

BindingFlags.NonPublic | BindingFlags.Instance);

12.

Console.WriteLine("\nField value of 'myString': {0}",

13.

myFieldInfo.GetValue( myObject ));

14.

myFieldInfo.SetValue( myObject, "New value",

15.

BindingFlags.Default, null , null );

16.

Console.WriteLine( "Field value of 'mystring' : {0}",

17.

myFieldInfo.GetValue( myObject ) );

18.

Object theObj = Activator.CreateInstance(myType);

19.

Type[] paramTypes = new Type[1];

20.

paramTypes[0] = Type.GetType("System.String");

```

```

21.

MethodInfo myMethod = myType.GetMethod

22.

("MyStringLength", paramTypes);

23.

ParameterInfo[] pi = myMethod.GetParameters();

24.

Type returnType = myMethod.ReturnType;

25.

Console.WriteLine("The parameter type: {0}",

26.

pi[0].ParameterType);

27.

Object[] parameters = new Object[1];

28.

parameters[0] = "Hello";

29.

Object returnVal = myMethod.Invoke(theObj,parameters);

30.

int val = (int)returnVal;

31.

Console.WriteLine(val); } }

```

## Code example 2: Value Modification with reflection

## Excerpt of the ouput:

The parameter type: System.String The return type: System.Int32 Field value of 'myString': Old value Field value of 'myString': New value

Lines 10-11 show how to get a reference to the declaration of a private field by using the field's name. At line 13, we retrieve the value of the field for a particular object. Lines 14-15 demonstrate how to modify the value of the field for a particular object. Line 18 uses a static method of the *Activator* class to create an instance of a type. Lines 23-25 demonstrate how to discover the various aspects of a dynamically discovered class method. Lines 27-28 prepare the necessary parameters to make the dynamic call to the method and line 29 makes the call. This code fragment demonstrates the raw reflective powers that are missing in C++.

# 3.3.2 Attribute Programming[50] [41]

Both the C# and the CLI standards defined a method for adding declarative information (metadata) to runtime entities. Since the .Net Framework has at its core the CLI, it also has metadata support. The mechanism through which metadata may be added to a program is called attribute programming. Attributes can be added to all the elements of a program except the body of properties and methods. It is even possible to add declarative information to the assembly, which is a unit of deployment that is similar to an .exe or .dll file on the Windows platform.

As mentioned before, attributes in .Net may be used to add extra information about elements in a program but they also provide an elegant, consistent approach to adding declarative information to runtime entities that permit a new way of designing software. The mechanism to retrieve these attributes (metadata) at runtime has also been standardized, permitting software components developed by different teams or even companies to interact and discover each other through metadata. Metadata may even be used to control how the program interacts with different runtime entities. It is this capability that we exploit later in this thesis.

The following is an example of a possible attribute that could be used to tag a class with hardware type information. We give an example of a class tagged with some metadata and we recover the metadata using introspection.

```

1. [HardwareType("CPU")]

2. public class MyProcessor{

public string technology= "FPGA";}

3.

4.

5. public class MetadataInspecter{

6.

public static void Main() {

7.

MyProcessor obj = new MyProcessor ();

8.

Type hardwaretype = typeof(HardwareTypeAttribute)

9.

Type type = obj.GetType();

10.

Object[] attributes =

type.GetCustomAttributes(hardwaretype, false)

11.

12.

foreach(Object attribute in attributes){

13.

HardwareTypeAttribute ht = attribute

14.

as HardwareTypeAttribute;

Console.WriteLine("Hardware Type:{0}", ht.type);}}

15.

```

Code example 3: Attribute programming example

#### Excerpt of the ouput:

Hardware Type: CPU

The important lines are 10 and 11 which show how to retrieve custom metadata from a type object.

## 3.3.3 Delegates

Callbacks are an important concept in the implementation of event handling. Here is a good informal definition for the concept of a callback:

A scheme used in event-driven programs where the program registers a subroutine (a "callback handler") to handle a certain event. The program does not call the handler directly but when the event occurs, the run-time system calls the handler, usually passing it arguments to describe the event. [29]

Most modern programming languages have constructs that permit the implementation of callbacks such as function pointers in C++ and interfaces in Java [2]. The .Net Framework and C# use delegates to address event handling. The concept of delegates improves upon function pointers by being object-oriented and type-safe and improves upon interfaces by allowing the invocation of a method without the need for inner class adapters. Also, delegates are inherently multicasting – a delegate contains a list of bounded methods that are invoked in sequence when the delegate is invoked. Another interesting difference between a delegate and a function pointer is that the delegate may contain an instance method in its invocation list, not only a static method as with function pointers, because the delegate keeps the information of the object that the method should be called on.

There are three steps in defining and using delegates: declaration, instantiation, and invocation.

Delegates are declared using delegate declaration syntax.

```

delegate void MyDelegate();

```

The example declares a delegate named MyDelegate that takes no arguments and returns no result.

Delegates are instantiated like all other object-oriented constructs.

```

class Test{

static void F() {

System.Console.WriteLine("Test.F");}

```

```

5. static void Main() {

6. MyDelegate d = new MyDelegate(F);

7. d();}} // delegate invocation

```

## Code example 4: Simple delegate example

The example declares a variable of type *MyDelegate* and then instantiates it. The delegate is then invoked.

```

1. class Test{

static void F() {

System.Console.WriteLine("Test.F");}

4.

5.

static void G() {

System.Console.WriteLine("Test.G");}

7.

8.

static void Main() {

9.

MyDelegate d = new MyDelegate(F); //static binding of F

10.

d += New MyDelegate(G) //dynamic binding of G

11.

d();}}// delegate invocation

```

## Code example 5: Delegate example

In the above example, when the delegate is invoked, both the F and G methods are called in the sequence in which they were bound to the delegate.

C# has added a key to add event handling semantics to a class field that is a delegate type: event. A delegate qualified with the event keyword has no effect on the field from inside the class or class instance's scope. From outside the scope, however, the field may not be invoked, the field can only be used on the left-hand side of the += and -= operators. The += operator adds a handler for the event, and the -= operator removes a handler for the event.

```

public delegate void DataNotifyHandler(object sender,

System.EventArgs e);

public class DataProducer{

public event DataNotifyHandler notify;}

public class DataConsumer{

void DataReady(object sender, EventArgs e) {

Console.WriteLine("Data is ready!");}}

```

```

12. public class App{

13.

14. static public void Main() {

15. DataProducer prod = new DataProducer();

16. DataConsumer com = new DataComsumer();

17. prod.notify+= new DataNofityHandler(com.DataReady);

18. }

```

## Code example 6: Event keyword example

The above example shows a DataConsumer class that adds DataReady as an event handler for the **notify** event of a *DataProducer* class which is declared with the *event* keyword. This example shows how a simple and naive way of synchronizing a producer and consumer.

# 3.3.4 Delegates and Reflectivity

A powerfull combination is the use of reflection in collaboration with delegates. Compared to most language .Net/C# permits methods to be bound to a delegate at runtime. For example, in C++, the name of the method that is bound to a function pointer must be known at compile time, but in .Net/C# it is possible to create a delegate type object with a static method of the Delegate class. The method takes as parameters an object and the name of the method which should be bound to the created delegate.

With reflectivity, it is possible at runtime to discover the names of the various methods that an object supports, so it is possible to dynamically discover an object's method and bind it to a delegate.

The example below illustrates this flexibility:

```

public delegate void myMethodDelegate();

public class MyClass{

static public void Hello() {

Console.WriteLine("Hello");}

public void GoodMorning() {

Console.WriteLine("Good Morning");}

public void Bye() {

Console.WriteLine("Bye");}}

public class MainApp{

```

```

11.

static event myMethodDelegate myDelegate;

12.

static public void Main() {

13.

MyClass obj = new MyClass();

14.

Type objType = obj.GetType();

15.

Type myMethodDelegateType = typeof(myMethodDelegate);

16.

foreach (MethodInfo method in

17.

objType.GetMethods(BindingFlags.DeclaredOnly |

18.

BindingFlags.Static |

19.

BindingFlags.Instance |

20.

BindingFlags.Public)){

21.

if(method.GetParameters().Length == 0 &

22.

method.ReturnType == typeof(void))

23.

if (method.IsStatic)

24.

myDelegate+= (myMethodDelegate) Delegate.CreateDelegate

25.

(myMethodDelegateType, method);

26.

else

27.

myDelegate+=(myMethodDelegate)Delegate.CreateDelegate

28.

(myMethodDelegateType, obj, method.Name);

29.

}

30.

if (myDelegate!=null)

31.

myDelegate();}}

```

## Code example 7: Delegates and reflection

This example iterates through all the static and instance methods that are declared public of an object (obj) of type *MyClass*. Each method is verified for two conditions: no formal arguments and a void return type. If the method fulfils the two conditions it is then bound to a delegate object (myDelegate). Static and instance methods of an object are bound dynamically to a delegate in different ways. Line 23-25 show how to bind a static method. Lines 26-28 show how to bind an instance method. Line 30-31 test the delegates in order to discover if it has been initialized. If it has a value other than null it is invoked.

The core of our environment makes use of an algorithm similar to code example 7, however, we incorporate the use of attributes to selectively filter the methods. Dynamic method discovery and delegate creation are useful because they enable a simple and elegant solution for implementing entry points in a simulation kernel for third-party tools. We also use them to dynamically create the processes of our simulation model (see Chap 5).

# Chapter 4 ESys.Net

After struggling with the downfalls of SystemC, we looked for another alternative that would enable us to model systems in a simple effective manner and that would allow us to explore different types of CAD and EDA tools for partition, verification and synthesis. After looking at many environments and languages we stumbled cross the C# language and the .Net Framework. We immediately noticed that C# and .Net brought together several important features from various existing solutions i.e. Java, C++, ML, etc. and brought several new features that would probably enable the development of a new environment for system-level design based on the previous work of SystemC.

This section describes the fruit of our labor: Embedded Systems with .NET, a new system-level design environment based on SystemC. ESys.Net is meant to be an evolution of SystemC by offering the same modeling capabilities but in a more elegant package. ESys.Net also innovates on SystemC by using a better underlying programming language which permits it to inherit operating system primitives, a rich software component library for rapid tool development and powerful runtime.

The next section will present briefly with the aid of an example the core elements of ESys.Net. These elements will then be explained in depth in subsequent sections.

# 4.1 A Simple Example

The best way to present a new tool is with an example, here is a simple example called "MyFirstSystem" that we will use to present our environment.

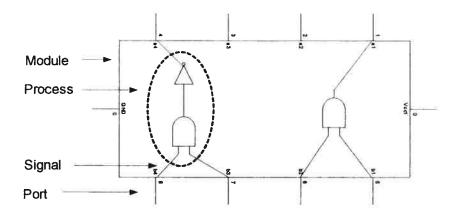

Here is a pictorial representation of MyFirstSystem.

Figure 2: My First System

"MyFirstSystem" is a model for a simple synchronous hardware component that is being tested with a testbench. The hardware component, named "generator", generates an integer on its output port on each positive edge of the main system clock. When a new value is generated by the hardware component, the testbench is notified of the new value by the "generator". The testbench then reads the new value from its input port and then prints it out.

Like most real hardware components, the "generator" is composed of subcomponents. These sub-components are responsible for generating an integer value on each positive edge of the main system clock which is then added together by a computation process in the encapsulating component.

The following code represents the blueprint for the two sub-components (gen1 and gen2):

```

1. public class ModuleA : BaseModule{

public Clock clk;

3.

public outInt porta;

4.

5.

public ModuleA(): base(){}

6.

7.

[Process]

8.

[EventList("posedge", "clk")]

9.

public void Gen() {

10.

while(true) {

```

```

11. for(int i=0;0<100;i++) {

12. porta.Value=i;

13. Wait();}}}</pre>

```

## Code example 8: ModuleA blueprint

Code example 8 declares the specification for a component that has one input port, clk and one output port, porta. The input is used to drive the component with a clock signal. The output is used to transmit an integer value that is generated by the Gen method. Hardware elements are concurrent by nature, they all compute in parallel. To indicate that the Gen method represents a computation that is concurrent, which we call a process, we tagged the method with a Process attribute. All methods tagged with the Process attribute execute concurrently. The EventList attribute indicates that the Gen method is sensitive to the positive edge (posedge) of the clk input.

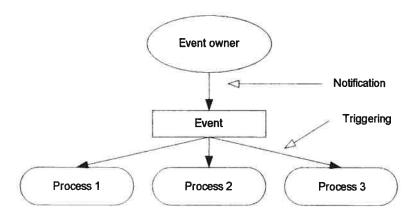

The role of the *EventList* tag is to indicate an association between a process and a triggering object which is implemented with the *Event* class that is defined in our environment. As its name implies, the *Event* class represents an event that may occur during the simulation of the model. When an event is triggered, the processes that are associated to an event are executed. In the above example, the **clk** field owns an event called **posedge** – that represents the event of a positive edge-, when the clock represented by **clk** field generates a positive edge, it triggers it **posedge** event.

The *Wait* method call in the *Gen* method indicates that the execution should stop at that point and then resume when an event on its triggers list occurs.

```

1. public class ModuleB : BaseModule {

2.

3.

public inInt porta;

4.

public Event syn_event;

5.

6.

public ModulB(): base(){}

7.

8. [Process]

9. public void Run() {

while(true) {

11.

Wait(syn event);

12.

Console.WriteLine(porta.Value);}}

```

Code example 9: ModuleB blueprint

This code fragment represents the blueprint of the testbench module. It only has an input port porta. Its Run method has been tagged with a Process attribute so it will run concurrently with the Gen methods of the gen1 and gen2 sub-components. What is distinct about this module is that the method indicated to become a process does not have an EventList attribute. This is not a problem, before the simulation starts, all methods that are processes that do not have an event list are executed once. The Wait method call with an event as an argument within the Run method indicates that the method will stop at this point and wait until the event is triggered.

```

1. public class MyModule : BaseModule {

2. public outInt porta;

3. public Clock clk;

4. public Event syn event = new Event();

5.

6. ModuleA gen1 = new ModuleA();

7. ModuleA gen2 = new ModuleA();

IntSignal sig1 = new IntSignal();

9.

IntSignal sig2 = new IntSignal();

10.

11. public MyModule(): base(){}

12.

13. [PMethod]

14. [EventList("sensitive","sig1","sig2")]

15. public void Add() {

16.

porta.Value = sig1.Value + sig2.Value;

17.