# Université de Montréal

# Waveform Narrowing: A Constraint-Based Framework for Timing Analysis

par Maroun Kassab

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

Thèse présentée à la Faculté des études supérieures en vue de l'obtention du grade de Philosophiæ Doctor (Ph. D.) en informatique

Mars, 2002

© Maroun Kassab, 2002

QA 76 US4 2002 1.025

.

# Université de Montréal

# Waveform Narrowing: A Constraint-Based Framework for Timing Analysis

by Maroun Kassab

Département d'informatique et de recherche opérationnelle Faculté des arts et des sciences

A thesis submitted to the Faculty of Graduate Studies in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

March, 2002

© Maroun Kassab, 2002

# Université de Montréal

Faculté des études supérieures

Cette thèse intitulée:

# Waveform Narrowing: A Constraint-Based Framework for Timing Analysis

présentée par

Maroun Kassab

a été évaluée par un jury composé des personnes suivantes:

# Résumé

#### Mots Clés

Faux chemins, ITGE, Vérification formelle, Circuits logiques séquentiels, Vérification des aspects temporels.

La vérification des aspects temporels des circuits logiques synchrones est NP-dur à cause du problème des faux chemins dans les circuits combinatoires. Les méthodes de vérification basées exclusivement sur les propriétés topologiques du circuit sont trop pessimistes, et les méthodes exactes ont une complexité exponentielle de temps d'exécution au pire cas. Nous présentons dans cette thèse une méthode basée sur la satisfaction des contraintes, ayant une complexité linéaire d'espace, et une complexité de temps qui peut être quasi-linéaire,  $n \times \log(n)$ , quadratique ou exponentielle, tout dépendant du niveau de précision requis. La méthode consiste à modéliser le circuit, les conditions de fonctionnement, et les contraintes temporelles par un système de contraintes qui est consistant si et seulement si les contraintes temporelles ne sont pas respectées. Le système de contraintes contient un ensemble de variables, prenant valeurs de leurs domaines respectifs, et un ensemble d'opérateurs de contraintes dont chacun opère sur un sous-ensemble des variables. Le système est résolu partiellement en appliquant répétitivement les opérateurs de contraintes, éliminant des valeurs qui ne font partie d'aucune solution, jusqu'à ce qu'il atteigne le point fixe, où ce n'est plus possible de changer les domaines des variables. Lorsque la résolution résulte en une variable ayant un domaine vide, on déduit que le système est incohérent et par conséquent les contraintes temporelles sont respectées; autrement, on ne peut rien conclure.

La méthode conduit à des résultats faux négatifs dans le cas où la résolution partielle se terminerait avec des domaines non vides, et que le système est en réalité incohérent. Nous avons développé deux méthodes polynomiales pour réduire ce pessimisme:  Le concept des *dominateurs temporels*, des nœuds clés dans le circuit, ayant des domaines qui peuvent être réduits suite à des conditions nécessaires déduites en examinant la fonction globale du circuit;

v

Une procédure de corrélation spatiale qui permet de renforcer partiellement la fonction globale du circuit sur les nœuds ayant des branchements convergents, en restreignant leurs domaines à des ondes qui se stabilisent à la valeur logique 0, puis à 1, et en combinant les résultats.

Nous avons aussi développé une procédure de décision qui permet de trouver une solution du système de contraintes (vecteur de test qui viole les contraintes temporelles) ou de prouver que le système est effectivement incohérent.

Lorsque appliquée sur les benchmarks standards ISCAS'85, la méthode a trouvé les bornes supérieures des délais des circuits correspondant aux délais exacts. En plus, à l'exception du circuit c6288, la procédure de décision a trouvé des vecteurs de test pour tous les circuits avec un nombre remarquablement restreint de retours en arrière.

On a rendu l'implantation plus complète et robuste afin de pouvoir tester la méthode sur des circuits industriels. Le vérificateur résultant fut testé sur un circuit industriel de 122 milles portes logiques, et a prouvé qu'au pire cas, la marge de sécurité de la contrainte d'établissement des bascules est en fait 17.459% du temps de cycle, comparée à 8.74% déduite par une analyse topologique.

# Abstract

## Keywords

Timing Verification, False Path Problem, VLSI, Formal Verification, Synchronous Sequential Circuits.

Verifying the timing properties of VLSI circuits is NP-Hard due to the false path problem, and considering just the topological delay of the circuit is too conservative and may result in unnecessary redesign efforts. We present in this thesis a timing verification method based on *Waveform Narrowing*. The method has linear space complexity, and has controllable time complexity that can be virtually linear,  $n \times \log(n)$ , quadratic, or exponential, depending on the required level of accuracy. The method consists of modeling the circuit, the timing constraints, and the operating conditions as a constraint system that is consistent if and only if the timing constraints are violated. The constraint system is composed of a finite set of variables that take values from their respective domains, and a set of relational constraint operators, each operating on a subset of the variables. The system is solved partially by repeatedly applying the constraints, removing from the domains values that are not part of any solution, until the greatest fixpoint is reached. If we end up with empty domains, we conclude that the timing constraints are satisfied; otherwise, no conclusion can be drawn.

The method results in false negative answers when we end up with non-empty domains, and yet the constraint system has no solution. To reduce this pessimism we developed two polynomial techniques:

The *Timing dominators* concept that determines key circuit nets for which the domains can be narrowed as a consequence of necessary conditions deduced from the global circuit function;

*Spatial correlation* procedure that enforces partially the global circuit function by restricting the domains of selected reconvergent fan-outs to waveforms stabilizing at 0 and 1, and then merging the results.

Also, we developed a case analysis procedure able to find a test vector or to prove that no violation is possible.

When tested on ISCAS'85 benchmarks, the method found tight upper bounds that correspond to exact circuit delays for all circuits. Moreover, except for c6288, the case analysis procedure found test vectors for all circuits with a remarkably low number of backtracks!

We extended the method by implementing capabilities necessary to verify industrial designs. The resulting timing verifier was tested successfully on a 122K-gate industrial circuit, and proved that its relative safe margin is 17.459% of the clock cycle instead of 8.74% reported by topological analysis.

# CONTENTS

| List of Figures xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Tables xviii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| List of Symbols, Keywords, and Abbreviations xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter I Introduction       1         1.1 Design Flow       2         1.2 Post-Fabrication Testing       3         1.3 Timing Verification       4         1.3.1 Simplified Model of a Synchronous Sequential Circuit       5         1.3.2 Constraints of Memory Elements       5         1.3.3 Verification of a Flip-Flop's Constraints       8         1.3.4 Synchronizing Clocks       9         1.3.5 Component Delays       10         1.3.5.1 Factors Affecting Component Delays       10         1.3.5.2 Delay Models and Components Correlation       12         1.3.6 Maximal Delay of a Combinational Circuit       12         1.3.7 Minimal Delay of a Combinational Circuit       15         1.3.8 The False Path Problem       16         1.4 Original Contributions of this Thesis       18 |

| Chapter II Literature Review192.1 Methods Based on Path Enumeration212.1.1 Static Sensitization232.1.2 The Brand-Iyengar Criterion242.1.3 Co-Static Sensitization252.1.4 Viable Sensitization252.1.5 Floating Mode Sensitization262.2 Reduction to a Test Generation Problem262.3 Mixed Boolean-Linear Programming282.4 Hierarchical Method292.5 Method Based on Constraint Satisfaction30                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter III Method Based on Waveform Narrowing                |  |

|---------------------------------------------------------------|--|

| 3.1 Overview of the WN Method                                 |  |

| 3.1.1 Inconsistency Property                                  |  |

| 3.2 Formalism for Timing Verification                         |  |

| 3.2.1 Abstract Waveforms                                      |  |

| 3.2.2 Abstract Signals Domain                                 |  |

| 3.2.3 Other Domains                                           |  |

| 3.2.4 Timing Verification                                     |  |

| 3.3 Combinational Circuit Example                             |  |

| 3.4 Sequential Circuit Example                                |  |

| 3.5 Relational Constraints                                    |  |

| 3.5.1 Delay Constraints                                       |  |

| 3.5.2 Delayless Gate Constraints                              |  |

| 3.5.2.1 Buffer Gate (Identity)                                |  |

| 3.5.2.2 Inverter Gate (NOT)                                   |  |

| 3.5.2.3 AND Gate                                              |  |

| 3.5.2.4 OR - NAND - NOR Gates Constraints                     |  |

| 3.5.2.5 Exclusive OR Gate (XOR)74                             |  |

| 3.6 Combinational Circuit Delay Verification / Basic Modeling |  |

| 3.7 Reduction of Pessimism                                    |  |

| 3.7.1 Static Learning                                         |  |

| 3.7.2 Spatial Correlation                                     |  |

| 3.7.3 Global Timing Implications                              |  |

| 3.7.4 Static Timing Dominators                                |  |

| 3.7.5 Dynamic Timing Dominators                               |  |

| 3.8 Case Analysis                                             |  |

| 3.8.1 Controllability Measure                                 |  |

| 3.8.2 Requirement Propagation / Back Trace Procedure          |  |

| 3.8.3 Case Analysis Procedure                                 |  |

| 3.9 Experimental Results                                      |  |

| 3.10 Conclusions                                              |  |

|                                                               |  |

| Chapter IV Advanced Modeling116                               |  |

| 4.1 Clock Definition Formalism                                |  |

| 4.2 Modeling Delays                                           |  |

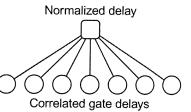

| 4.2.1 Normalized Delay                                        |  |

| 4.2.2 Delay Correlation Networks                              |  |

| 4.3 Modeling Building Blocks124                               |  |

| 4.3.1 Domains                                                 |  |

| 4.3.2 Primitive Constraints                                   |  |

| 4.4 Cell Library Modeling                                     |  |

| 4.5 Handling of Combinational Loops                           |  |

| 4.6 Timing Verifier                                           |  |

| 4.7 Experimental Results                                      |  |

| 4.8 Conclusions                                               |  |

|                                                               |  |

ix

| ginal Contributions of this Thesis       144         ure Work       146         (Algorithms)       148         uateConstraintSystem()       xxvii         OrderedReconvergentFanouts(gate)       xxix         patialCorrelation(order, s)                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| isadvantage       144         ginal Contributions of this Thesis       144         ure Work       146         (Algorithms)       148         uateConstraintSystem()       xxvii         OrderedReconvergentFanouts(gate)       xxix         patialCorrelation(order, s) |

| ginal Contributions of this Thesis       144         ure Work       146         (Algorithms)       148         uateConstraintSystem()       xxvi         OrderedReconvergentFanouts(gate)       xxix         patialCorrelation(order, s)                                |

| ure Work                                                                                                                                                                                                                                                                |

| uateConstraintSystem()xxvii<br>OrderedReconvergentFanouts(gate)xxix<br>patialCorrelation(order, s)xxx                                                                                                                                                                   |

| (Algorithms)                                                                                                                                                                                                                                                            |

| uateConstraintSystem()xxvii<br>OrderedReconvergentFanouts(gate)xxix<br>patialCorrelation(order, s)xxx                                                                                                                                                                   |

| OrderedReconvergentFanouts(gate)xxix<br>patialCorrelation(order, s)xxx                                                                                                                                                                                                  |

| patialCorrelation(order, s)xxx                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                         |

| elateReconvergentFanouts(gate_set)xxxii                                                                                                                                                                                                                                 |

| imingDominators( output ) xxxiv                                                                                                                                                                                                                                         |

| uateConstraintSystemTD( output )xxxv                                                                                                                                                                                                                                    |

| (Cell Modeling)                                                                                                                                                                                                                                                         |

| Primitives Used to Model Cell Libraries                                                                                                                                                                                                                                 |

| Input AND Gate Cell Model Examplexliv                                                                                                                                                                                                                                   |

| P-FLOP Gate Cell Model Example                                                                                                                                                                                                                                          |

| ,                                                                                                                                                                                                                                                                       |

х

# **LIST OF FIGURES**

| Figure 1                                                                                     |

|----------------------------------------------------------------------------------------------|

| Design flow of integrated circuits                                                           |

| Figure 2         Stuck-at-1 fault testing                                                    |

| Figure 3 Delay fault testing                                                                 |

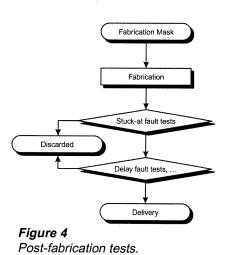

| Figure 4 Post-fabrication tests                                                              |

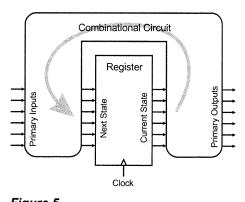

| Figure 5<br>Sequential synchronous circuit                                                   |

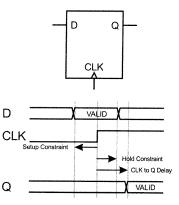

| Figure 6<br>Rising edge-triggered flip-flop                                                  |

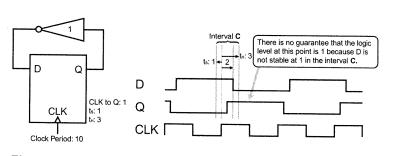

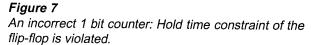

| Figure 7<br>An incorrect 1 bit counter:<br>Hold time constraint of the flip-flop is violated |

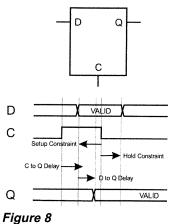

| Figure 8<br>High level sensitive latch                                                       |

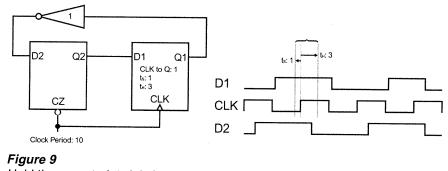

| Figure 9<br>Hold time constraint violation prevented by the use of a transparent latch7      |

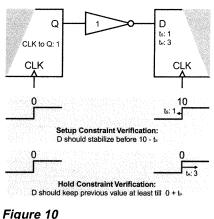

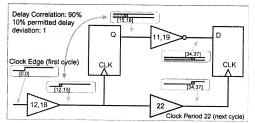

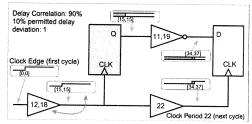

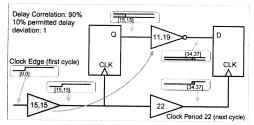

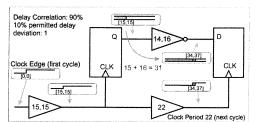

| Figure 10<br>Unfolding clock cycles                                                          |

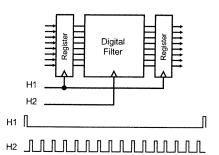

| Figure 11<br>Sequential circuit controlled by two harmonically related clocks                |

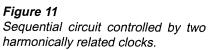

| Figure 12<br>Delay of an inverter                                                            |

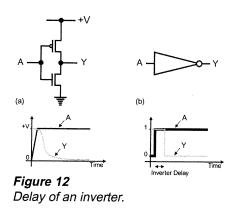

| Figure 13       P (left) and N type transistors.       11                                    |

| Figure 14<br>Silicon wafer                                                                   |

| Figure 15<br>Examples of input stimuli                                                       |

| Figure 16<br>Difference between floating and sequences of vectors maximal delays             |

| Figure 17                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

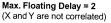

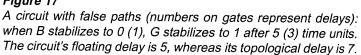

| A circuit with false paths (numbers on gates represent delays):<br>when B stabilizes to 0 (1), G stabilizes to 1 after 5 (3) time units.                                                             |

| Its floating delay is 5, whereas its topological delay is 7                                                                                                                                          |

| Figure 18       A path statically sensitized                                                                                                                                                         |

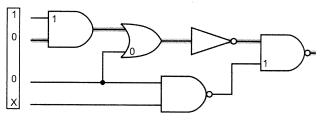

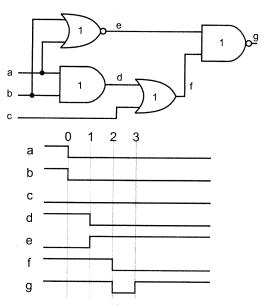

| <b>Figure 19</b><br>A true path of length 3 identified as false by static sensitization criterion24                                                                                                  |

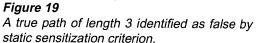

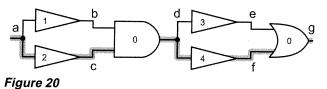

| Figure 20<br>A false path of length 6 identified as true by co-static sensitization ( $a = 0$ ) 25                                                                                                   |

| Figure 21<br>A circuit to be transformed to the equivalent normal form                                                                                                                               |

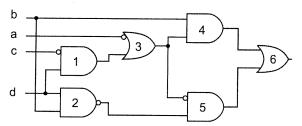

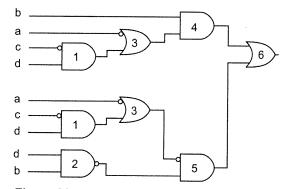

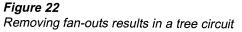

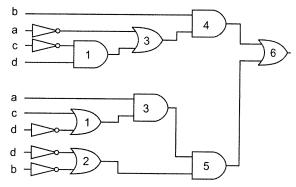

| Figure 22         Removing fan-outs results in a tree circuit                                                                                                                                        |

| Figure 23         The result of pushing back the inverters.                                                                                                                                          |

| Figure 24 Normal form representation                                                                                                                                                                 |

| Figure 25 (a): Abstract signal domain. (B): Clock edge domain                                                                                                                                        |

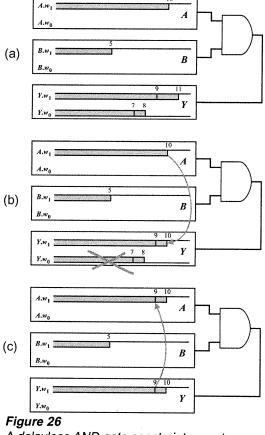

| <ul> <li>Figure 26 <ul> <li>A delayless AND gate constraint operator.</li> <li>(a) Initial domains.</li> <li>(b) Effect on the gate output Y.</li> <li>(c) Effect on the input A</li></ul></li></ul> |

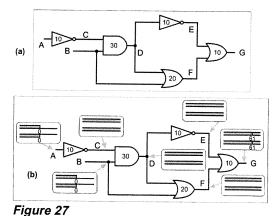

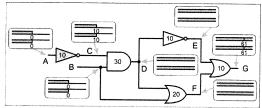

| Figure 27 <ul> <li>(a): Combinational circuit with a false path.</li> <li>(b): Combinational circuit example: step 0</li></ul>                                                                       |

| Figure 28<br>Combinational circuit example: step 140                                                                                                                                                 |

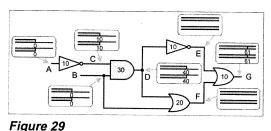

| Figure 29<br>Combinational circuit example: step 2                                                                                                                                                   |

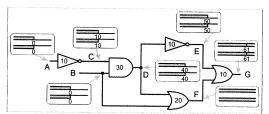

| Figure 30<br>Combinational circuit example: step 3                                                                                                                                                   |

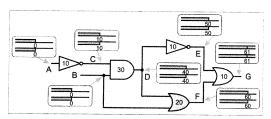

| Figure 31<br>Combinational circuit example: step 441                                                                                                                                                 |

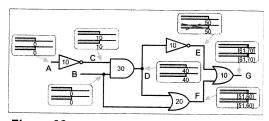

| Figure 32<br>Combinational circuit example: step 5                                                                                                                                                   |

| Figure 33         Combinational circuit example: step 6.         42 |

|---------------------------------------------------------------------|

| Figure 34         Combinational circuit example: step 7.         42 |

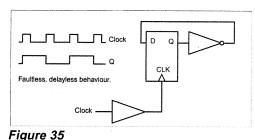

| Figure 35      Frequency divider.                                   |

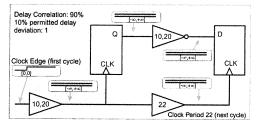

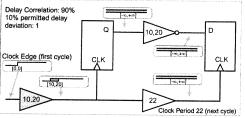

| Figure 36         Sequential circuit example: step 044              |

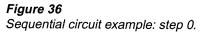

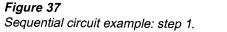

| Figure 37 Sequential circuit example: step 145                      |

| Figure 38         Sequential circuit example: step 2                |

| Figure 39         Sequential circuit example: step 3                |

| Figure 40       Sequential circuit example: step 445                |

| Figure 41         Sequential circuit example: step 5                |

| Figure 42         Sequential circuit example: step 6                |

| Figure 43         Sequential circuit example: step 746              |

| Figure 44         Sequential circuit example: step 8                |

| Figure 45         Sequential circuit example: step 9                |

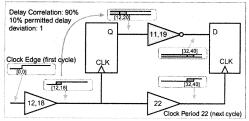

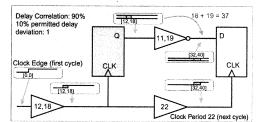

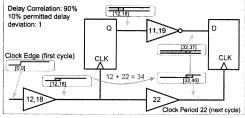

| Figure 46         Sequential circuit example: step 10               |

| Figure 47         Sequential circuit example: step 11               |

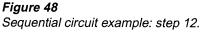

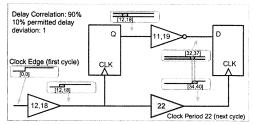

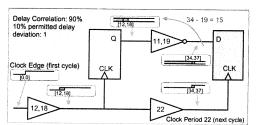

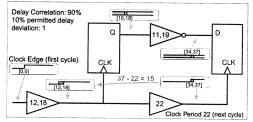

| Figure 48<br>Sequential circuit example: step 1247                  |

| Figure 49<br>Sequential circuit example: step 1347                  |

| Figure 50<br>Sequential circuit example: step 14                    |

| Figure 51<br>Sequential circuit example: step 15                    |

xiii

| Figure 52         Sequential example: step 16.                                              |

|---------------------------------------------------------------------------------------------|

| Figure 53                                                                                   |

| Sequential example: step 17                                                                 |

| Figure 54         Sequential example: step 18.                                              |

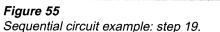

| Figure 55         Sequential example: step 19.                                              |

| Figure 56         Sequential example: step 20.                                              |

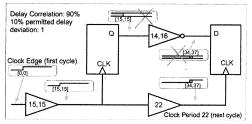

| Figure 57<br>Waveform narrowing for steps 6 through 20                                      |

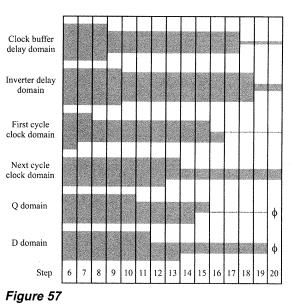

| Figure 58      An incompatible value                                                        |

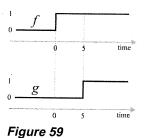

| Figure 59         A delayed binary waveform                                                 |

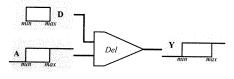

| Figure 60<br>Clock delay constraint                                                         |

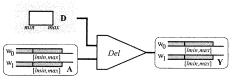

| Figure 61      Data delay constraint.                                                       |

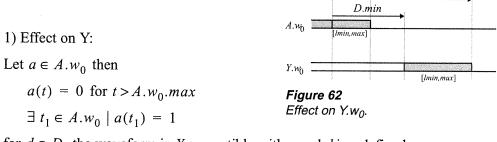

| <b>Figure 62</b><br>Effect on Y.w <sub>0</sub>                                              |

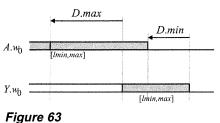

| Figure 63Effect on $A.w_0$                                                                  |

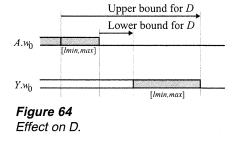

| Figure 64<br>Effect on D                                                                    |

| Figure 65 Buffer Constraint                                                                 |

| Figure 66<br>NOT Constraint                                                                 |

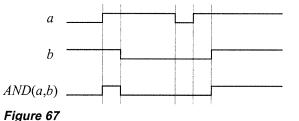

| Figure 67         ANDing two binary waveforms                                               |

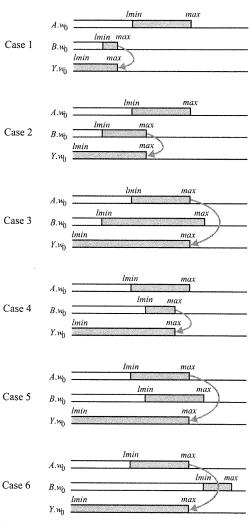

| Figure 68         AND Constraint                                                            |

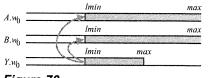

| Figure 69<br>AND Constraint ( $A.w_0, B.w_0, Y.w_0$ ) - effect on $Y.w_0$                   |

| Figure 70<br>AND Constraint ( $A.w_0$ , $B.w_0$ , $Y.w_0$ ) - effect on $A.w_0$ and $B.w_0$ |

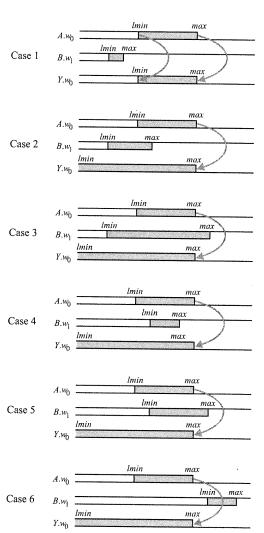

| Figure 71<br>AND Constraint (A. $w_0$ , B. $w_1$ , Y. $w_0$ ) - effect on Y. $w_0$ 64           |

|-------------------------------------------------------------------------------------------------|

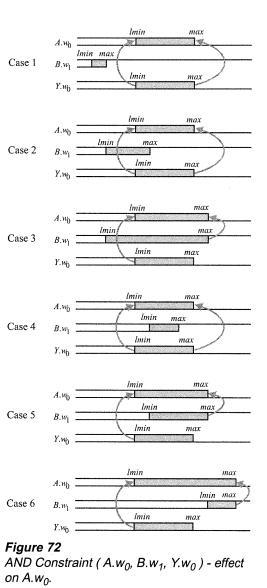

| Figure 72<br>AND Constraint (A. $w_0$ , B. $w_1$ , Y. $w_0$ ) - effect on A. $w_0$              |

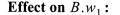

| Figure 73<br>AND Constraint (A. $w_0$ , B. $w_1$ , Y. $w_0$ ) - effect on B. $w_1$              |

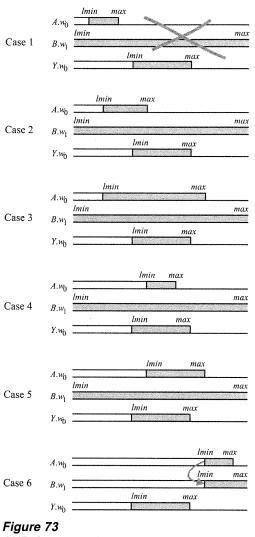

| Figure 74<br>AND Constraint (A. $w_1$ , B. $w_1$ , Y. $w_1$ ) - effect on Y. $w_1$              |

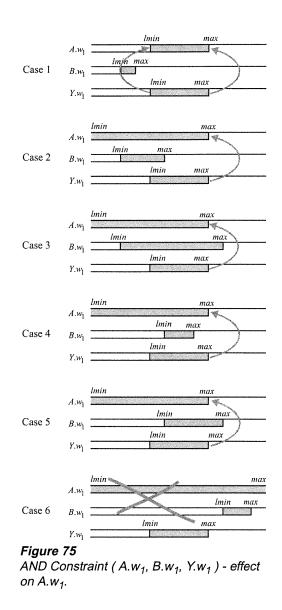

| Figure 75<br>AND Constraint (A. $w_1$ , B. $w_1$ , Y. $w_1$ ) - effect on A. $w_1$              |

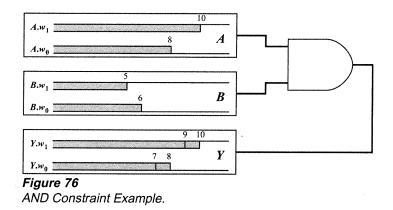

| Figure 76      AND Constraint Example.                                                          |

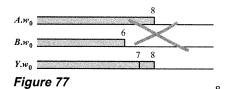

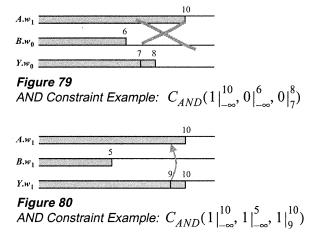

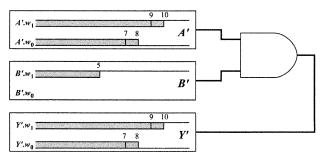

| Figure 77<br>AND Constraint Example: $C_{AND}(0 _{-\infty}^8, 0 _{-\infty}^6, 0 _7^8)$          |

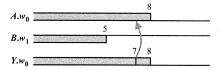

| Figure 78<br>AND Constraint Example: $C_{AND}(0 _{-\infty}^8, 1 _{-\infty}^5, 0 _7^8)$          |

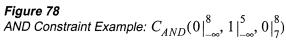

| Figure 79<br>AND Constraint Example: $C_{AND}(1 _{-\infty}^{10}, 0 _{-\infty}^{6}, 0 _{7}^{8})$ |

| Figure 80<br>AND Constraint Example: $C_{AND}(1 _{-\infty}^{10}, 1 _{-\infty}^5, 1 _9^{10})$    |

| Figure 81<br>Domains contents after the AND constraint is applied                               |

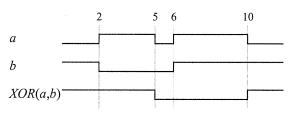

| Figure 82<br>XORing two binary waveforms74                                                      |

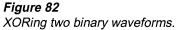

| Figure 83<br>XOR Constraint                                                                     |

| Figure 84<br>XOR Constraint (A. $w_0$ , B. $w_0$ , Y. $w_0$ ) - effect on Y. $w_0$              |

| Figure 85<br>XOR Constraint ( $A.w_0, B.w_0, Y.w_0$ ) - effect on $A.w_0$                       |

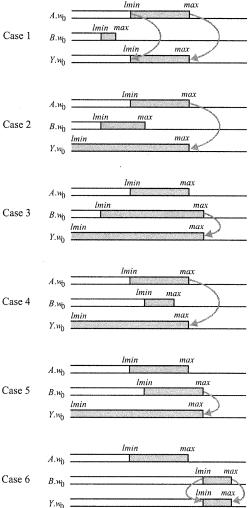

| Figure 86<br>NAND-4 constraint model                                                            |

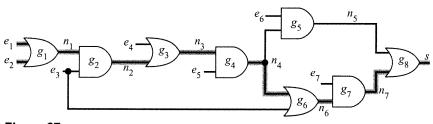

| Figure 87<br>False path circuit of Hrapcenko                                                    |

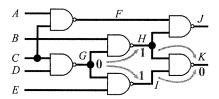

| Figure 88<br>Static Learning on the circuit c17                                                 |

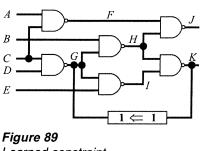

| Figure 89                                                                                       |

| Learned constraint                                                                              |

|                                                                                                 |

.

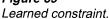

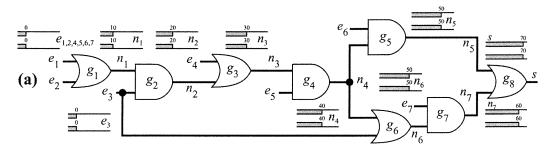

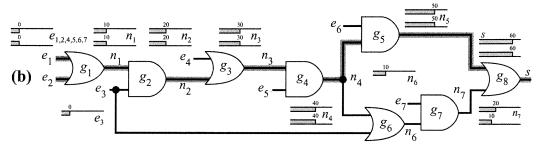

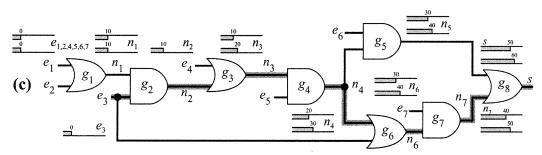

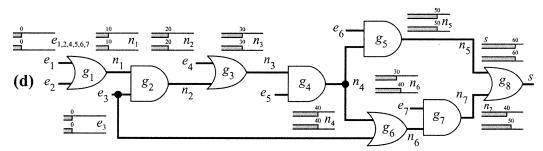

|   | Figure 90 Spatial correlation on reconvergent fan-out $e_3$ .          |

|---|------------------------------------------------------------------------|

|   | (a) Domains before spatial correlation                                 |

|   | (b) Domains when $e_3$ is restricted to waveforms stabilizing at 1     |

|   | (c) Domains when $e_3$ is restricted to waveforms stabilizing at 0     |

|   | (d) Domains after spatial correlation on $e_3$ (union of (b) and (c) ) |

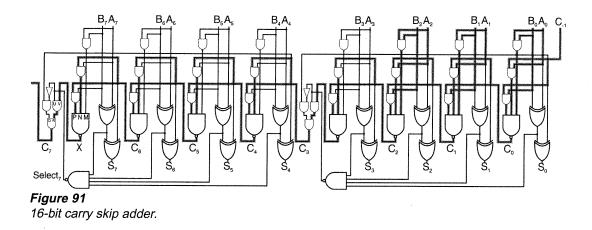

|   | Figure 91<br>16-bit carry skip adder                                   |

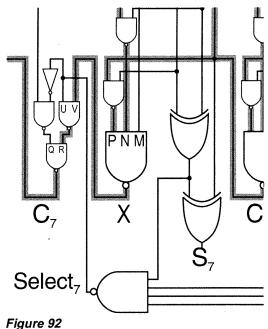

|   | Figure 92                                                              |

|   | Carry out of 16-bit carry skip adder90                                 |

|   |                                                                        |

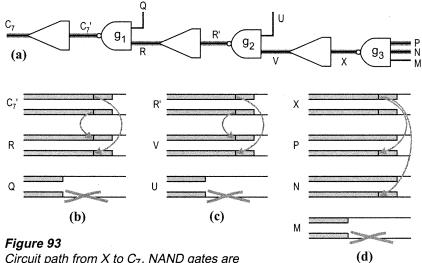

|   | Figure 93                                                              |

|   | Circuit path from X to C7.                                             |

|   | NAND gates are represented as separate delays                          |

|   | and delayless NAND constraints90                                       |

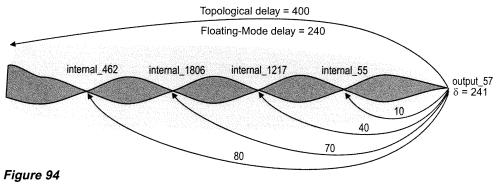

|   | Figure 94                                                              |

|   | Timing dominators of output_57 of c1908-ALL-GATES95                    |

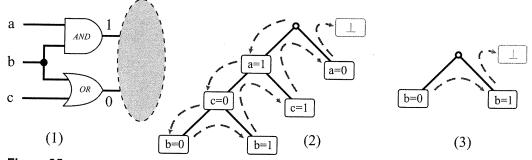

|   | Figure 95                                                              |

|   | (1) Requirements impossible to satisfy.                                |

|   | (2) Decision tree when b is chosen the last.                           |

|   | (3) Decision tree when b is chosen the first                           |

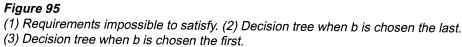

|   | Figure 96                                                              |

|   | Requirement propagation                                                |

|   |                                                                        |

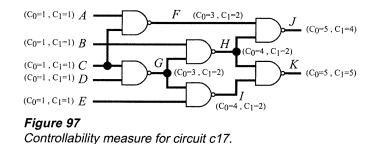

|   | Figure 97                                                              |

|   | Controllability measure for circuit c17100                             |

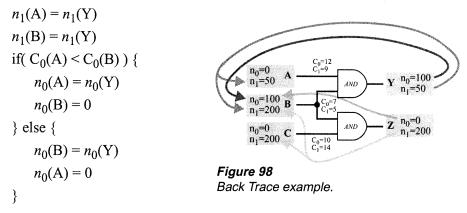

|   | Figure 98                                                              |

|   | Back Trace example                                                     |

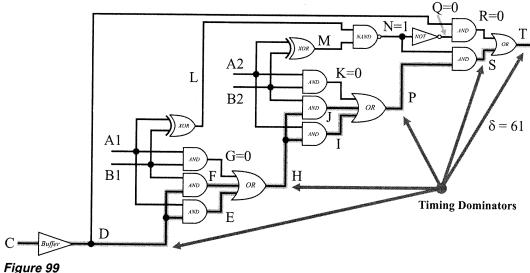

|   | Figure 99                                                              |

|   | Timing check $(\xi, T, 61)$ for a carry skip circuit                   |

|   | Figure 100                                                             |

|   | Topological partitioning for decision making                           |

|   |                                                                        |

| - | Figure 101                                                             |

|   | Topological partitioning for phase 1                                   |

| ] | Figure 102                                                             |

|   | Clocking scheme example                                                |

| ] | Figure 103                                                             |

|   | Normalized delay                                                       |

| 1 | Figure 104                                                             |

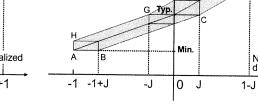

| , | Gate interval delay, function of J and N                               |

|   |                                                                        |

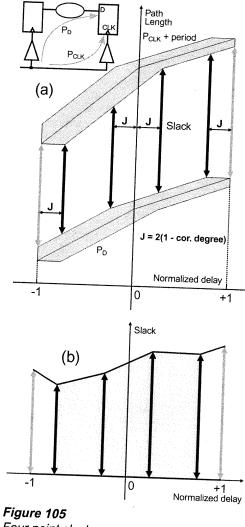

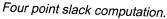

| 1 | Figure 105                                                             |

|   | Four point slack computation                                           |

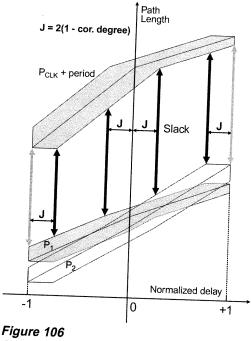

| Figure 106                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------|

| Slack for multiple data paths                                                                                               |

| Figure 107                                                                                                                  |

| Simple delay correlation network                                                                                            |

| Figure 108         One-dimensional position dependent delay correlation network.         123                                |

| Figure 109                                                                                                                  |

| Two-dimensional position dependent delay correlation network                                                                |

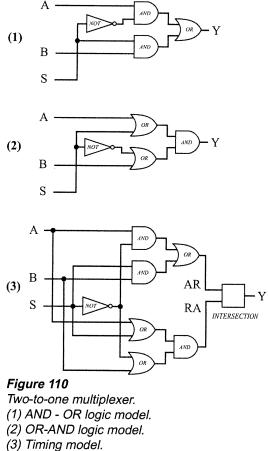

| Figure 110<br>Two-to-one multiplexer.<br>(1) AND - OR logic model.<br>(2) OR-AND logic model.<br>(3) Timing model           |

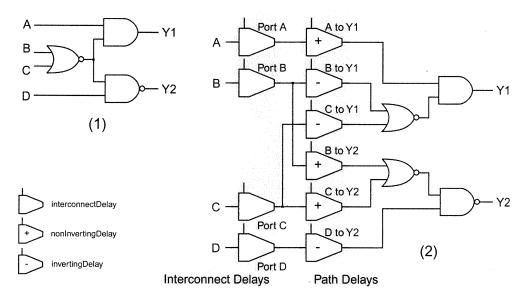

| Figure 111         Combinational cell modeling example.         (1) Cell logic function.         (2) Cell constraint model. |

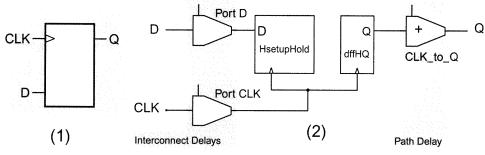

| Figure 112<br>Flip-Flop cell modeling example.<br>(1) Cell logic function.<br>(2) Cell constraint model                     |

| Figure 113                                                                                                                  |

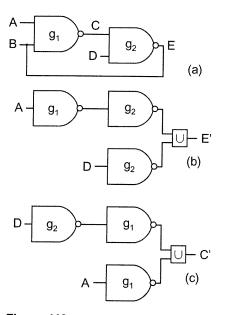

| Combinational loop example.                                                                                                 |

| (a) C and E are part of a combinational loop.                                                                               |

| <ul><li>(b) Loop aware constraint for E.</li><li>(c) Loop aware constraint for C134</li></ul>                               |

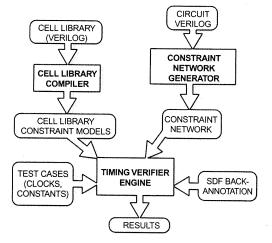

| Figure 114<br>Timing Verifier Architecture134                                                                               |

| Figure 115                                                                                                                  |

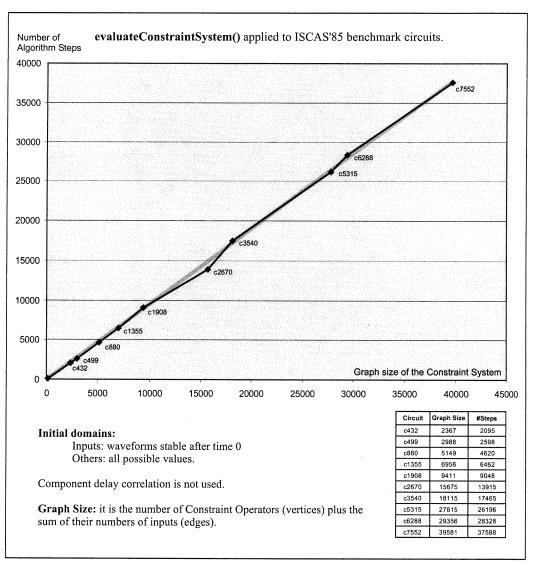

| Experimental time complexity of the basic WN method on ISCAS'85 xxviii                                                      |

| Figure 116                                                                                                                  |

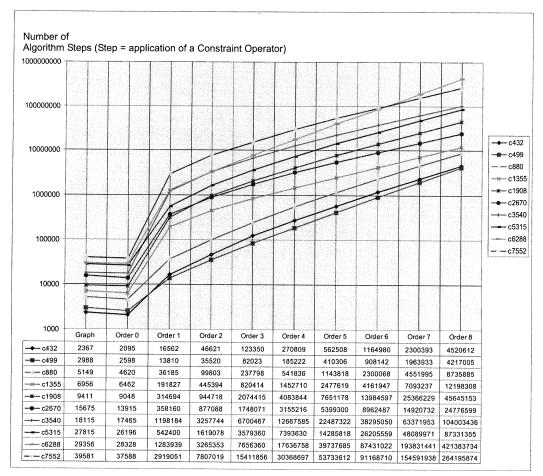

| Experimental time complexity of doSpatialCorrelation on ISCAS'85 xxxi                                                       |

| Figure 117                                                                                                                  |

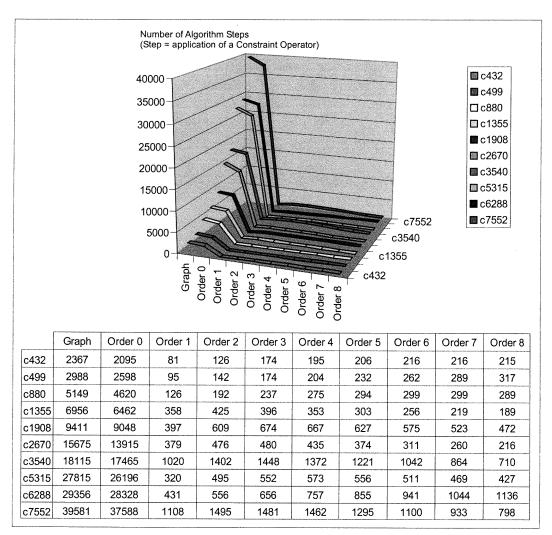

| Experimental time complexity of each system evaluation of the spatial correlation on ISCAS'85xxxiii                         |

# LIST OF TABLES

| Table I     Floating algebra                                                                          |

|-------------------------------------------------------------------------------------------------------|

| Table II         Sensitization criteria for delayless two-input AND gate                              |

| Table III         Substitution for Controlling / Non-Controlling / Controlled / Non-Controlled values |

| Table IV         Results on the ISCAS'85 benchmark suite                                              |

| Table V         Summary of the results on the ISCAS'85         NOR-GATES benchmark suite              |

| Table VI         False path elimination summary                                                       |

| Table VII           Results on an industrial benchmark for best-case delay annotation.                |

| Table VIII           Results on an industrial benchmark for worst-case delay annotation               |

# LIST OF SYMBOLS, KEYWORDS, AND ABBREVIATIONS

#### AND

The logic And gate function.

#### AS

The space of Abstract Signals.

# ATPG

Automatic test pattern generation.

# AW

The space of Abstract Waveforms.

### BDD

Binary decision diagram.

#### BW

The space of Binary Waveforms.

### C++

An object oriented programming language.

# CMOS

Complementary metal-oxide semiconductor.

# CPU

Central processing unit.

# CRYSTAL

A transistor-level timing verifier developed by Ousterhout.

#### EDA

Electronic design automation.

### FAN

An algorithm for test pattern generation developed by Fujiwara and Shimono.

# **FLIP-FLOP**

An edge-triggered memory element.

# HDL

Hardware description language.

#### IC

Integrated circuit.

# ISCAS

International Symposium on Circuits and Systems.

# ITGE

Intégration à très grande échelle.

# Kbytes

1024 bytes.

# Kgates

Thousand gates.

# Mbytes

1048576 bytes.

# MIPS

Million instructions per second.

# NAND

The Inverted logic And gate function.

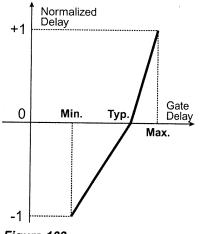

# ND

Normalized Delay.

# NMOS

N-type metal-oxide semiconductor transistor.

### NOR

The Inverted logic Or gate function.

# NOT

The logic Inverter gate function.

#### **NP-Complete**

Non deterministic polynomial complete.

# NP-hard

Non deterministic polynomial hard.

### OR

The logic Or gate function.

# PERT

A method based on graph topological ordering for analyzing critical paths.

# PLL

Phase locked loop.

## **PMOS**

P-type metal-oxide semiconductor transistor.

#### PODEM

An algorithm for test pattern generation developed by Goel.

## RAM

Random access memory.

## RealIntervals

The space of real intervals.

# SCALD

Structured Computer-Aided Logic Design, a computer program containing a gate-level timing verifier developed by McWilliams.

# SCOPE

A method for calculating the controllability measure.

## SDF

Standard Delay Format, an industry standard for component delay representation.

# SPICE

A computer program for circuit simulation.

# TV

A transistor-level timing verifier developed by Jouppi.

#### Verilog

A hardware description language.

# VHDL

A hardware description language.

#### VLSI

Very large scale integration.

#### WN

Waveform Narrowing.

#### XNOR

The Inverted logic Exclusive-Or gate function.

#### XOR

The logic Exclusive-Or gate function.

for Berthe, Alice, and Lory-Ann

# ACKNOWLEDGMENTS

This work is part of the Power and Timing Verification Research Project in LASSO laboratory at the Université de Montréal, supervised by Professor Eduard Cerny.

First, I would like to express my gratitude to my research advisor Professor Eduard Cerny, without whom this work could not have come to accomplishment. Professor Cerny is an extraordinary wealth of knowledge and energy, exemplary in his dedication to making projects successful. Apart from his leadership and the strict work progress verification, he provided the necessary industrial relations, directing the project toward applications that are applied to the real industrial world. He provided me with invaluable technical advice through deep discussions of the subject matter of my research, enlarging substantially my knowledge in Electronic Design Automation and mathematics. Not to mention that he provided me with the opportunity to participate in many technical conferences.

- Thanks to all those who participated in the Power and Timing Verification Project. Especially Jindrich Zejda, M. Sidi Aourid, and Aisha Bensalem.

- Nortel Networks provided office space and access to proprietary information and machines to conduct experiments. More importantly, Thomas Krodel, Carol Bachelu, and Spiros Boucouris, experts in the field of timing verification, provided precious technical assistance and help in an exceptionally friendly professional environment!

- Nortel Networks and Functionality Inc. provided us with InCore data structure software that includes Verilog and SDF parsers.

- Parts of the experiments were done on workstations on loan from the Canadian Microelectronics Corp.

Funding for the project was provided partly by Natural Sciences and Engineering Research Council of Canada (NSERC) - Nortel North America Cooperative R&D Grant No. 169880.

Additional funding for my studies was provided by the following organizations:

- Ministère de l'Éducation du Québec aide financière aux études;

- Université de Montréal, entente de financement.

- NSERC Industrial Postgraduate Scholarship in association with Nortel Networks.

Last but not least, I would like to thank all my friends, family, and parents, especially Berthe who, despite all the difficulties we encountered, provided all the needed support.

# PREFACE

Electronic Design Automation (EDA) is a multi-billion-dollar industry that is struggling to keep pace with the increasing capability of silicon technology that is still following the Moore's Law. A common cause of increasing complexity is design methodology that is not uniform. EDA tools need to handle excessive number of special cases that make it impossible to hard-code their user interface. Most design tools are command line utilities, or shared libraries integrated using scripting extension languages like Tcl, which makes the learning curve steep and makes the design methodology open. In fact, too much of the capabilities of the tools are exposed to designers who can easily abuse them. The complexity of the user interface makes the EDA industry adopt methods that are easy to code, validate, integrate, and use. For instance, although too pessimistic, topological analysis is still the basis of many commercial timing verifiers because of its simplicity. The result is an industry that is expanding horizontally; little effort is available for advanced research.

Academia is, however, more relaxed, and one can still dedicate effort to investigate a new method, hoping to provide new scientific solutions that EDA and the scientific community in general may benefit from. This thesis presents the results of the investigation we conducted on a new timing verification method based on waveform narrowing, inspired by logic constraint programming and interval arithmetic.

It was a great challenge to write this thesis as it deals with complex subjects related to optimization techniques, electrical engineering, and to computer science. We did our best to make the thesis highly illustrated, self-contained, requiring no in-depth knowledge in any of the subjects mentioned, however, mathematical maturity is a prerequisite for the understanding of this work.

# **CHAPTER I**

# **INTRODUCTION**

Advances in very large scale integration (VLSI) technology have made digital electronics essential for a wide spread of applications. In the 1960's, circuits were fabricated using millimetric scale discrete components such as transistors, resistors and capacitors. Recently, Motorola succeeded in fabricating a microprocessor device using a new 0.1 micron process technology [1]. Current standard fabrication processes use 0.35, 0.25, 0.18, and 0.11 microns for the transistor size, enabling the integration of a complete system containing millions of transistors on a single silicon chip.

The increasing complexity led the designers' community to formalize the design flow, and made essential the use of computer assisted design and verification tools. Simulation based verification of gigantic designs has become practically impossible due to the exponential state explosion problem (e.g. A processor with 16 registers, 32 bits each, has  $2^{512}$  possible states). Consequently, formal verification, an approach exploiting mathematical techniques in order to prove certain functional properties without having to enumerate all existing states, has emerged. Numerous problems are subject to formal verification, such as the equivalence of two state machines or two logic circuits, proof that a system stays alive (no deadlock), or verifying that timing constraints of memory elements are satisfied in a sequential circuit.

The subject of this thesis is the development of a "static" timing verifier for synchronous sequential circuits. The attribute "static" is used instead of formal to comply with timing verification literature.

The remainder of this chapter introduces the principal subject as well as related subjects that are necessary to the understanding of the subsequent parts of the thesis.

# **1.1 Design Flow**

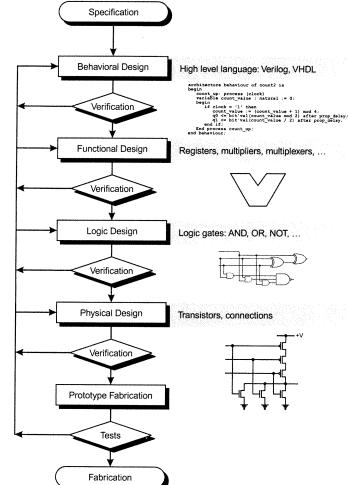

Figure 1 shows a simplified design flow of integrated circuits. Starting from specifications (function, response time, power dissipation, etc.), the design process follows a descending hierarchical approach. Each level of abstraction has to be verified as functionally equivalent to the one above it, and, that different constraints such as power dissipation and response time are satisfied.

Obviously, the process is iterative, and the purpose of design and verification tools is to minimize the number of iterations, especially at lower levels, where the fabrication of prototypes is very expensive.

## **Different Levels of Abstraction:**

**Behavioral Level:** The system is defined using a high-level hardware description language (HDL) such as Verilog or VHDL.

- **Register Transfer Level:** The description of the system in terms of functional blocks (multipliers, multiplexers, registers, etc.) This description is obtained using a compiler for the behavioral level, i.e., the high-level language, or by manual translation.

- **Logic Gate Level:** The definition of the system is in terms of logic gates and memory elements (AND, OR, NOT, flip-flops, etc.). The logic synthesizer generates this description from the Register Transfer Level.

- **Transistor Level:** The lowest level in the hierarchy. This level is an assembly of transistors and metal connectors. A technology mapper is used to rewrite the logic gate level in terms of gates from a well-characterized library (e.g., TGC1000 from Texas Instruments). Then, placement and routing tools are applied to generate the physical layout.

### **1.2 Post-Fabrication Testing**

The production of integrated circuits is a complex lithographic process that yields a success ratio lower than 1. The success rate varies depending on the process technology and the chip area.

Two major models of fabrication defects are used:

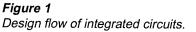

- **Stuck-at Fault**: the output of a logic gate g is said to be stuck-at-1 (0) if its logic level remains 1 (0) regardless of its input levels. For example, the output of an AND gate is 1, even if one of the inputs is 0. To detect such a defect, a test vector must be applied to the circuit inputs, propagating the fault to at least one of the outputs. Fig. 2 shows a simple example.

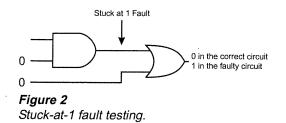

- **Delay Fault**: a gate can have an excessive delay due to a fabrication defect. A common cause of such a defect is an excessive interconnect resistance caused by a very thin open that still permits conduction by tunneling effect. To detect such a defect, two test vectors must be applied successively to the circuit inputs in order to trig-

ger a transition that propagates to a circuit output through the defect, as shown in the example of Fig. 3.

Finally, for a specific design, a set of test vectors is generated to detect possible defects. Manufactured chips are tested before delivery as indicated in Fig. 4. Automatic Test Pattern Generation (ATPG) is a domain that has been widely studied in the last 30 years [31-55]. Contributions in this domain offer a rich set of heuristics [32,33,35] that help resolve the satisfiability of a Boolean formula.

#### Figure 3 Delay fault testing.

**1.3 Timing Verification**

Verifying timing properties of a synchronous sequential circuit consists of determining whether it functions properly at a certain clock frequency (e.g. 500 MHz), or determining the maximal safe clock frequency. This verification can be applied to any level of abstraction. The highest precision is obtained only after the actual physical design is available, where the different circuit components are precisely characterized. Before reaching this stage, approximate delays are assumed for each circuit component and interconnect.

Note that the violation of timing constraints of circuit components depends on the clock frequency, functioning semantics, and circuit topology. The following section

defines default semantics for synchronous sequential circuits, adopted throughout this thesis, unless stated otherwise.

#### **1.3.1 Simplified Model of a Synchronous Sequential Circuit**

A model of a combinational logic circuit is a directed acyclic graph. Nodes represent logic gates and each arc represents a connection (connects the output of a gate to the input of another gate). The circuit input (output) terminals are represented by nodes with no incident (exiting) arcs.

A synchronous sequential circuit is an implementation of a state machine. The state is stored in a register and the next state is calculated by a combinational logic circuit as shown in Fig. 5. The state register consists of memory elements for which the memorizing action is triggered by the system clock.

The default operation semantics assumes that a new state is calculated every clock cycle.

*Figure 5* Sequential synchronous circuit.

Therefore, the clock period must be long enough for the combinational circuit to finish its calculations and for the memory elements to store the new state at the next active clock edge.

#### **1.3.2 Constraints of Memory Elements**

Two types of memory elements are used: Edge-sensitive flip-flops, and level-sensitive transparent latches. The most common ones used for state memorization are the flipflops sensitive to the rising edge of the clock (transition from 0 to 1, see Fig. 6). When the logic level of the clock CLK changes from 0 to 1, the logic level of input D is memorized and becomes present at the output Q. Like every physical device, the memorization operation is not instantaneous; its timing behavior is characterized by three parameters [12]:

CLK to Q Delay: This delay represents the time necessary for the memorized logic level to get to the output Q.

Figure 6 Rising-edge-triggered flip-flop.

2, 3)Setup Time (t<sub>S</sub>), Hold Time (t<sub>H</sub>) Constraints: They represent the timing constraints on the

> logic level of D to be memorized correctly. D must be valid (stable) in the interval  $[t_R - t_S, t_R + t_H]$  where  $t_R$  is the arrival time of the rising edge of CLK.

The timing verifier must check that setup and hold constraints are satisfied for each flip-flop.

Note that the setup time constraint tends to be violated when higher clock frequency is used, whereas, hold time constraint tends to be violated due to the circuit topology, resulting in a system that does not function properly with any given clock frequency. In the circuit of Fig. 7, the flip-flop does not memorize correctly the new state computed by the inverter due to the premature disappearance of the previous value. Violation of the hold time constraint is due to very short paths in the combinational circuit, and to clock skew (non-simultaneous arrival time of the clock edge at different flip-flops).

Flip-flops sensitive to the falling clock edge (sensitive to the transition from 1 to 0 of the clock) are defined in a similar manner.

The behavior of the level sensitive latch (transparent latch) is slightly different. Consider the latch sensitive to the high level (see Fig. 8), when the clock C is at 1, the output follows the input (Q = D). When C falls to 0, Q keeps its last value. Its temporal behavior is characterized by four parameters [12]:

- C to Q Delay: Time before Q starts to follow D, after C rises to 1.

- D to Q Delay: When C = 1, it is the events (logic level change) propagation time from D to Q.

High level sensitive latch.

3, 4) **Setup Time, Hold Time Constraints**: The same definition as for the falling edge flip-flop (the edge of the clock after which the latch keeps its last value).

The low level sensitive latch is defined similarly.

Hold time constraint violation prevented by the use of a transparent latch.

Transparent latches are frequently used in industrial circuits to avoid violation of hold time constraints of edge-triggered flip-flops. Fig. 9 shows a revised version of the circuit in Fig. 7: the low level sensitive latch prevents the premature disappearance of the previous state by delaying it to the falling edge of the clock. When CLK rises to 1, the value of Q1 becomes D1 after 1 time unit (CLK-to-Q1), then D2 becomes  $\overline{Q1}$  after 1 time unit, but Q2 keeps its old value until CZ falls back to 0. Of course, the latch timing constraints must also be satisfied.

#### **1.3.3 Verification of a Flip-Flop's Constraints**

According to the operation semantics of the synchronous sequential circuit, the new value that each flip-flop stores has been computed from values stored on the previous clock cycle. To verify the constraints of a flip-flop, the combinational sub-circuit that does the computation is observed and the flip-flop setup and hold time constraints are studied separately. Considering the example in Fig. 7, only one flip-flop is present and the sub-circuit that does

Unfolding clock cycles.

the computation is the inverter. The flip-flop is broken down in two parts: one receives the data computed by the combinational circuit, and the other injects a value into that same circuit (see Fig. 10). For a period of 10 units of time, data is injected at time 0, and sampled at D at time 10.

Verifying the setup time constraint comes down to verifying that D stabilizes before  $10 - t_S$ , meaning that it is the maximal delay of the combinational circuit that comes into play. On the other hand, to check the hold time constraint, assuming that the flip-flop injects a value at time 0, it must be verified that the previous value of D does not disappear before  $t = 0 + t_H$ . In this case, it is the minimal delay of the combinational circuit that has to be considered.

In summary, the problem of deciding whether the setup or hold constraints are satisfied comes down to comparing the maximal and minimal circuit delays to certain given values.

Chapter 2 explains the major methodologies for computing the maximal combinational circuit delay proposed in literature.

#### 1.3.4 Synchronizing Clocks

In Section 1.3.1, the synchronous sequential circuit was introduced without exploring thoroughly the subject of synchronizing clocks. Designers of synchronous circuits face many practical and conceptual problems:

Maximal Fan-out Capability: In a real circuit,

it is not possible for a single gate output to

drive an indefinite number of gates without risking loss of data. Therefore, the clock signal is distributed to a number of buffers; each can then send it to a number of memory elements and / or other buffers.

- **Clock Skew**: To avoid violations of the hold time constraints, delays are inserted in the clock tree to minimize the time window in which the memory elements are activated.

- **Multiple Clocks**: For certain applications, such as the digital filter shown in Fig. 11, it is useful to use multiple clocks. In this particular case, for every voice sample, many cycles are needed to perform the filtering function.

- **Gated Clocks**: power dissipation in Complementary Metal Oxide Semiconductor (CMOS) circuits, is directly related to the number of signal transitions (change of logic level) on circuit nodes. To reduce power dissipation, logic gates are inserted to prevent the clock from propagating to the parts of the circuit that are irrelevant to the current operation.

A timing verifier must be able to deal with multiple and gated clocks without excessive user intervention.

#### **1.3.5 Component Delays**

The delay of a component is the time necessary for it to respond to a stimulus. Logic gate delays are related to fabrication technology. A CMOS circuit is essentially a network of P and N transistors interconnected by metal connections. Transistors act as switches (closed or open-circuit).

Gate delays: The logic level at the output of a

gate changes from 1 to 0 when the paths that lead to +V become all open and at least one path to ground (0 volt) becomes closed. Transistor switching time is not negligible, the electrical signal changes gradually instead of instantaneously. Fig. 12(a) shows a CMOS implementation of an inverter with its electrical response to a rising transition at its input. Fig. 12(b) shows the logic abstraction of this circuit. One particularity of CMOS gate delays is that they are inertial: two successive events (impulse) at the input of a gate that have time separation (pulse width) less than the gate delay do not affect the output; it is absorbed by the inertial gate delay.

**Interconnect delays**: as opposed to gate delays, interconnect delays are not inertial. They propagate events as waves.

## **1.3.5.1 Factors Affecting Component Delays**

#### **Gate Delays:**

Gates do not have fixed delay values; their dynamic properties are affected by many factors:

**Fabrication Process**: The silicon atom is an element of group 4 on the periodic table. It forms liaisons with four other atoms to make a non-conducting crystal. To construct transistors, the silicon chip is doped with atoms of group 3 such as gallium to get positive charge carriers (type P regions), and with atoms from group 5 (arsenic) to get negative charge carriers (N type regions). Fig. 13 shows the structure of Metal Oxide Semiconductor (MOS) transistors of types P and N. Feature size and doping density variations introduce uncertainty in the tran-

*Figure 13 P* (left) and N type transistors.

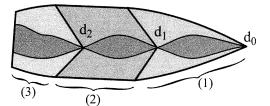

sistor switching time. The fabrication of chips is done on silicon wafers (see Fig.14). It is generally accepted that component features vary depending on the position within a wafer and from one wafer to another. On the same wafer, if A is a point where the doping density is  $d_A$ , then the density at a point B is contained within  $[d_A-f(AB), d_A+f(AB)]$ , where f is a positive non decreasing function such

law between the different gate delays on the same silicon chip. This law will be later elaborated by considering the effect of the fabrication process along with the effects of power supply and temperature. The relationship between doping density and gate delay is monotone, it can be increasing or decreasing depending on the process technology.

that f(0) = 0. The latter translates into a correlation

Figure 14 Silicon wafer.

- **Supply Voltage**: Fluctuations in supply voltage implies a change in gate delays. Generally, the delay increases as voltage decreases.

- **Temperature**: Ambient temperature and transistor switching activity cause temperature variations in the different regions of the silicon chip. Generally, the clock distribution network is at the highest temperature. A gate delay increases as the temperature rises.

- Slew Rate: When a signal at the input of a gate switches slowly, the gate response is also slower, resulting in a higher delay.

#### **Interconnect Delays:**

Metal connections are fabricated by depositing a conductor on the silicon substrate using a chemical process. This is done over several layers due to the fact that circuits are generally non-planar. An interconnect delay is affected by the depositing process, the chips geometry, and the temperature.

#### **1.3.5.2 Delay Models and Components Correlation**

Integrated Circuit (IC) manufacturers specify the variation margins of the different factors influencing gate delays. Fabrication process, electric power supply and temperature are the most noticeable. A delay value is defined by a set of three values ( $d_{min}$ ,  $d_{nom}$ ,  $d_{max}$ ). The actual delay is contained within the interval [ $d_{min}$ ,  $d_{max}$ ].

d<sub>min</sub>: Minimal value of the delay with respect to the three factors.

- d<sub>nom</sub>: Nominal value, defined over a predetermined condition of the three factors (e.g., temperature 25°, supply voltage 5 volts and doping density d).

- d<sub>max</sub>: Maximal value of the delay with respect to the three factors.

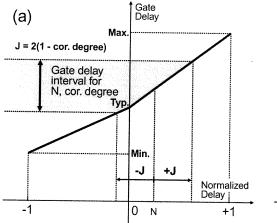

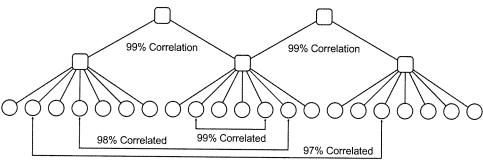

The effect of the influencing factors on gate delays of the same silicon chip, apart from signal slew rate, makes it impossible for different gates to have arbitrary values within the associated intervals  $[d_{min}, d_{max}]$ . For example, when the delay of a gate A has its maximum value  $d_{maxA}$ , the delay of a gate B is necessarily in the interval  $[d_{maxB} - \varepsilon, d_{maxB}]$ .  $\varepsilon$  is a positive value that depends on the degree of correlation, a number between 0 and 1 (0: no correlation, 1: 100% correlation). An elaborate delay correlation model is presented in chapter 4.

## 1.3.6 Maximal Delay of a Combinational Circuit

A combinational logic circuit  $\xi$  with *m* inputs and *n* outputs implements a logic function  $f: B^m \to B^n$  where  $B = \{0, 1\}$ . Due to gate and interconnect delays, the response of

$\xi$ , following an input stimulus, is not instantaneous and a certain lapse is necessary before the outputs stabilize at valid values.

- **Definitions and Terminology:**

- **Path**: a path of  $\xi$  is an alternating sequence of connections and gates which are connected one to the next.

- **Path Length**: the length of a path is the sum of the delays of its gates and connections.

| Α | В | NOT(B) | AND(A,B) |

|---|---|--------|----------|

| 0 | 0 | 1      | 0        |

| 0 | 1 | 0      | 0        |

| 0 | x | x      | 0        |

| 1 | 0 | 1      | 0        |

| 1 | 1 | 0      | 1        |

| 1 | x | x      | x        |

| x | 0 | 1      | 0        |

| x | 1 | 0      | x        |

| x | x | x      | х        |

Table I: Floating algebra.

- Maximal Topological Delay: the length of the longest (slowest) path of  $\xi$ .

- **Input Vector**: an input vector for  $\xi$  is an element of  $B^m \times R$ . This represents logic values applied at the inputs of  $\xi$  at a certain time t.  $(e_1, e_2, ..., e_m, t)$  is written  $(e_1, e_2, ..., e_m)_t$ .

- Sequence of Input Vectors: a sequence of k input vectors for  $\xi$ ,  $(v_{t1}, v_{t2}, ..., v_{tk})$ , is an element of  $(B^m \times R)^k$ , it is assumed that  $t_i < t_{i+1}$  i=1,k-1. Furthermore, when  $v_{ti}$  is applied at time  $t_i$ , it remains applied until time  $t_{i+1}$ . Obviously,  $v_{tk}$  remains applied indefinitely.

- Floating Algebra: it is the Boolean algebra augmented with an unknown uncorrelated value, denoted x. Table I defines the logic functions NOT and AND over  $F = \{0, 1, x\}$  (other functions are deduced in a straight-forward fashion). Many methods use this algebra to define and compute the delay of a combinational circuit. In that case,  $\xi$  computes  $f: F^m \to F^n$ .

- **Maximal Delay of Sequences of Vectors**: the maximal delay of sequences of vectors of  $\xi$ , denoted  $dmax^{S}(\xi)$  is:  $dmax^{S}(\xi) = \min \{t \ge 0 \mid \forall sv = (v_{-\infty}, \dots, v_{0}), \text{ all outputs of } \xi$  are stable after time t when sv is applied}. Intuitively, it is the maximal time for  $\xi$  to compute its logic function for every pos-

sible value of an input vector applied at time 0, assuming the inputs were previously arbitrarily changing.

- **Maximal Transition Delay**: The maximal transition-mode delay of circuit  $\xi$ , denoted  $dmax^{T}(\xi)$  is:  $dmax^{T}(\xi) = \min \{t \ge 0 \mid \forall (v_{-\infty}, v_{0}), t\}$  all outputs of  $\xi$  are stable after time t when  $(v_{-\infty}, v_{0})$  is applied}. It is the maximal time for  $\xi$  to compute its logic function for every possible value of an input vector  $v_{0}$  applied at time 0, assuming the inputs were previously stable at arbitrary levels.

- **Maximal Floating Delay**: The maximal floating delay of circuit  $\xi$ , denoted  $dmax^{F}(\xi)$  is:  $dmax^{F}(\xi) = \min \{t \ge 0 \mid$  $\forall (v_{-\infty}, v_{0}) \in ((\{x\}^{m} \times \{-\infty\}), (B^{m} \times \{0\})), \text{ all outputs of } \xi \text{ are stable after time } t \text{ when } (v_{-\infty}, v_{0}) \text{ is applied} \}.$  Note that the circuit outputs stabilize at values in B.

Fig. 15 shows examples of input signals for each of the previously defined delays. Note that the transition delay is not a valid model for sequential circuits because the state register changes value at every clock cycle. Devadas et al determined in [82] that the transition delay is valid when it is greater than  $(\frac{1}{2} \times \text{topologi$  $cal delay})$ .

Sequence of Vectors

Figure 15 Examples of input stimuli.

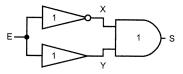

Lam and Brayton have shown in [102] that, for real circuits, floating and sequences of vectors delays are equal. The difference exists only in artificial cases such as the one shown in Fig. 16. In a real circuit, the probability of having two paths of exactly the same length is null. Consequently, the correlation between X and Y in the circuit in Fig. 16 is highly improbable.

Max. Delay for Sequences of Vectors = 0(X =  $\overline{Y}$  at all times, S = 0)

*Figure 16* Difference between floating and sequences of vectors maximal delays. **Monotone Speed-up Property**: A method for maximal circuit delay calculation that uses fixed delay values (max.) instead of intervals is said to satisfy the monotone speed-up property if the following holds:

Let C be a circuit for which the method calculates a max. delay of d. The method calculates a max. delayless than or equal to d for any circuit C' that is the same as C except that some of its components are faster.

In other words, speeding-up components of a circuit C does not result in a slower one (as calculated by the method).

## **1.3.7 Minimal Delay of a Combinational Circuit**

Definitions of minimal delays for a combinational circuit  $\xi$  are expressed in a symmetrical fashion with maximal delays.

- Minimal Topological Delay: the minimal topological delay of  $\xi$  is the length of its shortest path.

- Minimal Delay of Sequences of Vectors: the minimal delay of sequences of vectors of circuit  $\xi$ , denoted  $dmin^{S}(\xi)$  is:  $dmin^{S}(\xi) = \max \{t \ge 0 \mid \forall sv = (v_{-\infty}, v_{0}, ...), all outputs of <math>\xi$  are stable before t when sv is applied}. Intuitively, it is the time before which the outputs of  $\xi$  remain stable after applying  $v_{0}$  and assuming that, subsequently, inputs change arbitrarily.

- **Minimal Transition Delay**: the minimal transition delay of circuit  $\xi$ , denoted  $dmin^{T}(\xi)$  is:  $dmin^{T}(\xi) = \max \{t \ge 0 \mid \forall (v_{-\infty}, v_{0}), \text{ all outputs of } \xi \text{ are stable before } t \text{ when } (v_{-\infty}, v_{0}) \text{ is applied} \}.$

- **Minimal Floating Delay**: The minimal floating delay of circuit  $\xi$ , denoted  $dmin^F(\xi)$ is:  $dmin^F(\xi) = \text{maximum } \{t \ge 0 \mid \forall (v_{-\infty}, v_0) \in ((B^m \times \{-\infty\}), (\{x\}^m \times \{0\})),$ all outputs of  $\xi$  remain stable before t when  $(v_{-\infty}, v_0)$  is applied}.

#### 1.3.8 The False Path Problem

Fig. 17 shows a circuit that has a floating delayless than its topological delay. This phenomenon is caused by the fact that, in general, not all signal paths in a circuit can propagate transitions (so called false paths). When the longest paths are false, e.g., path A-C-D-F-G in the circuit of Fig. 17, the actual circuit delay is less than its topological delay. Hrapcenko [57] presented early an extended discussion on the subject, and proved that even minimal circuits may have their longest paths false. He noticed also that false paths appear naturally in accelerated carry-skip adders. This phenomenon makes the problem of deciding whether the maximal circuit delay is less than a certain value NP-complete, as shown in [76].

## 1.4 Original Contributions of this Thesis

The major contributions of this thesis are summarized as follows:

• Established the mathematical foundations of the *waveform narrowing* method for the purpose of floating-mode delay calculation, the original method was formulated around the transition-mode.

- Developed a spatial correlation procedure that was effective in reducing the pessimism of the method on standard and industrial benchmark circuits.

- Developed the *Timing Dominators* concept that was very successful in eliminating false violations with minimal added execution time complexity  $(n \times \log(n))$ .

- Developed a case analysis procedure able to find a test vector, or prove that no violation is possible. The procedure is guided by heuristics inspired by ATPG techniques, namely the controllability measure of [23] and the FAN algorithm of [33]. The procedure uses a novel partitioning strategy based on timing dominators.

In order to provide support for state of the art industrial circuits, we extended the method as follows:

- Developed an intuitive formalism able to express arbitrary complex clocking schemes, along with a procedure to deduce correct default edge selection for setup verification.

- Defined a delay correlation domain based on three-valued delay annotation (min, typ, max) using the novel concept of *normalized delays*. The resulting constraints can be used to build complex correlation networks able to model arbitrary complex component delay correlation, like position dependence, rising-delay vs. falling-delay, etc.

- Defined more than 70 constraint primitives able to model industrial cell libraries.

- Developed a hard multiplexer primitive that reduces the inherent pessimism of the floating delay model.

- Developed and automated a general concept for modeling combinational cells. And added cell aware constraints that remove the pessimism induced by path delays of unknown polarities.

- Added support for automatic handling of combinational loops, still present in some synchronous industrial designs.

• Implemented an industrial-grade version of the timing verifier in the object oriented language C++, and evaluated the Waveform Narrowing method on industrial circuits provided by Nortel Networks.

## 1.5 Plan of the Thesis

Chapter 2 presents an overview of the methods for computing maximal circuit delays proposed in the literature.

Chapter 3 contains the proposed timing verification method, along with the results on the standard ISCAS'85 benchmark suite.

Chapter 4 presents the extensions we implemented to enable the method to be applied to state of the art industrial designs, along with the results on industrial circuits provided by Nortel Networks.

Chapter 5 concludes the thesis.

## CHAPTER II LITERATURE REVIEW

In this chapter we review the major methodologies for computing the maximal delay in combinational logic circuits as presented in the literature. These methods have evolved from a simple topological sort of the PERT project by Kirkpatrick and Clark in 1966 [56] to more recent methods that consider the circuit functionality and automatically eliminate false paths.

#### Motivation

In the early 1980's, the increasing complexity of logic circuits made the use of simulators such as SPICE [9] futile for timing verification. SPICE solves differential equations to deduce the waveform at the output of a circuit, given a precise waveform at each input. Execution time was estimated to about a minute for each circuit transistor on a typical computer of that era. To compute the transition delay of a circuit, an exponential number of simulation runs is required in order to account for all possible situations. Therefore, a trade-off had to be made between execution time and precision.

## First Approach: Limited Worst Case Simulation - Case Analysis