Université de Montréal

Timing Verification of Interface Specifications and Controllers

par Fen Jin

Départment d'informatique et de recherche opérationnelle Faculté des arts et des sciences

Thèse présentée à la Faculté des études supérieures en vue de l'obtention du grade de Philosophiæ Doctor (Ph.D.) en informatique

août, 2000

<sup>©</sup> Fen Jin

QA 76 254 2001 4.002

- 1

Université de Montréal Facuté des études supérieures

Cette thèse intitulée

# Timing Verification of Interface Specifications and Controllers

Présentée par Fen Jin

a été évaluée par un jury composé des personnes suivantes:

Dr. El Mostapha Aboulhamid

Dr. Eduard Cerny

directeur de recherche

président-rapporteur

Dr. Yvon Savaria

membre du jury

Dr. Marco A. Escalante

examinateur externe

Thèse acceptée le:

## Résumé

text

# Vérification des spécifications tempe des interfaces et des contrôleurs

De nos jours, les systèmes micro-électroniques se composent généralement de composants tels des (ASICS), de circuits intégrés dédiés et d'autres IPs (Intellectual properties). Ces composants sont la plupart du temps conçus par différentes équipes travaillant dans différentes organisations. Dans ces systèmes, les composants communiquent entre eux via des interfaces. Il est donc très important de s'assurer de la compatibilité de ces interfaces, et aussi de s'assurer que les implémentations de ces interfaces respectent les spécifications de ces dernières.

Ce présent travail traite de la vérification des spécifications temporelles des interface et de la vérification de implémentations.

La vérification des spécifications temporelles des interface inclut la notion de compatibilité et aussi d'autres propriétés temporelles qu'il faut garantir. Dans ce travail, nous résolvons les problèmes de vérification des spécifications temporelles en utilisant le temps maximum de séparation entres les événements dans un graphe de contraintes tire des spécifications. Les interfaces en question sont spécifiées comme des boucles exprimées avec le langage HAAD (Loop over a leaf Hierarchical Annotated Action Diagram). Nous appliquons notre solution pour la vérification de certaines propriété temporelle qu il faut garantir dans la modélisation de la modélisation de la spécification d'une opération de lecture répétée d'un microprocesseur d'une mémoire.

La vérification des contrôleurs d'interfaces, avec leur spécification consiste a que l'implémentation produira les bons événements aux bons moments, comme décrits dans la spécification, en supposant que les événements aux entrées du contrôleur sont émis temps ainsi spécifiés dans la spécification. Dans ce travail, nous présentons une méthode pour vérifier si l'implémentation d'une machine à états pseudo-synchrone (entrée échantillonnée) d'un contrôleur en temps réel satisfait les spécifications de son diagramme temporel.

On applique notre méthode a un contrôleur de bus qui provient d'un design industriel et nous vérifions deux cycles d'ECRITURE avec la modélisation de la spécifi-

#### Abstract

#### **Timing Verification of Interface Specifications and Controllers**

Microelectronic systems are normally composed of components such as Application Specific Integrated Circuits (ASICs), custom integrated circuits and other intellectual properties. These components are generally designed by different teams from different organizations. In the systems, components are connected and communicated with each other through interfaces. To make the systems work, it is very important to verify that the interface specifications of components are compatible with each other and the implementations of interfaces are correct with respect to their specifications.

This work deals with timing verification of interface specifications and the verification of the interface controller implementations against their specifications.

The timing verification of interface specifications includes compatibility and the verification of the safety timing property. In this work, we solve the timing verification problems using maximum time separation between events in constraint graphs transformed from the specifications. The interested interfaces are specified as loops over a leaf Hierarchical Annotated Action Diagram (HAAD) language. We apply our solution technique in verifying several safety timing properties of a specification modeling a repeated READ operation of a microprocessor from a memory.

The verification of interface controllers against their specification consists in making sure that the implementation will produce correct events on time as given in the specification, under the assumption that the inputs events fed to the controller are on time as also stated in the specification. In this work, we present a method for verifying whether a pseudo-synchronous (sampled input) finite-state machine implementation of a real-time controller satisfies its timing diagram specification. We apply our method to a bus controller from an industrial design and check against its timing diagram specification modeling two consecutive asynchronous WRITE cycles.

All the algorithms and verification methods in this work are implemented in a Constraint Logic Programming environment based on Relational Interval Arithmetic.

# **Table of Contents**

| List of Figures iv                                                        |

|---------------------------------------------------------------------------|

| List of Tables vi                                                         |

| Acknowledgement vii                                                       |

| Glossary viii                                                             |

| Chapter 1: Introduction                                                   |

| 1.1 Timing Verification of Interface Specifications                       |

| 1.1.1 Specification Languages 16                                          |

| 1.1.2 Timing Properties on Interfaces                                     |

| 1.2 Verification of Interface Controllers Against Their Specifications 10 |

| 1.3 Contributions of the Work                                             |

| 1.4 Organization of the Thesis                                            |

| Chapter 2: Interface Specification and Verification                       |

| 2.1 HAAD Specifications of Interfaces                                     |

| 2.2 Verification of Interface Specifications                              |

| 2.3 From Verification of Timing Diagrams to Maximum Time Separation 40    |

| 2.4 Related Work                                                          |

| Chapter 3: The Maximum Time Separation Problem                            |

| 3. 1 Constraint Graphs                                                    |

| 3. 2 Well-formed Constraint Graphs 51                                     |

| 3.2.1 Events Along a Max Cycle 53                                         |

| 3.2.2 Events Along a Linear or a Mixed Cycle                              |

| 3. 3 Finite Unfolded Constraint Graphs                                    |

()

i

| 3. 4 Maximum Time Separation of Events - Problem Definition 58                    |

|-----------------------------------------------------------------------------------|

| Chapter 4: Maximum Time Separation in Finite Linear-plus-latest systems 62        |

| 4.1 The Variation Algorithm                                                       |

| 4.2 Proof of the Algorithm 4.1                                                    |

| 4.3 Examples                                                                      |

| 4.4 Complexity of the Variation Algorithm                                         |

|                                                                                   |

| Chapter 5: Maximum Time Separation Algorithms inr Cyclic Systems 78               |

| 5.1 Cyclic Linear-Only Systems                                                    |

| 5.2 Cyclic Linear-plus-Latest Systems                                             |

| 5.2.1 Algorithm to Compute $\Delta^{\alpha}$                                      |

| 5.2.2 Algorithm for Cyclic Linear-Plus-Latest Constraint Systems 87               |

| 5.2.2.1 Repetition of $sd(s_{\alpha}, v_j)$                                       |

| 5.2.2.2 Repetition of $\Delta(s_{\alpha}, v_j^*)$                                 |

| 5.2.2.3 Repetition of $\Delta(s_{\alpha}, v_j)$                                   |

| Chapter 6: Maximum Time Separatations in Causal Linear-plus-latest Cyclic Systems |

| 101                                                                               |

| 6.1 Restricted Constraint Graphs                                                  |

| 6.2 Simplification of Algorithm 4.1 in Restricted Acyclic Graphs 103              |

| 6.3 Maximum Time Separation in Restricted Cyclic Constraint Graphs 106            |

| 6.4 Sufficient Causal Conditions 120                                              |

| 6.5 Conclusion                                                                    |

| Chapter 7: Verification of Real Time Controllers Against Timing Diagram Specifi-  |

| cations                                                                           |

| 7. 1 Introduction                                                                 |

| 7. 2 Problem Definition                                                           |

| 7.2.1 A pseudo-synchronous controller                                             |

|                                                                                   |

# ii

| 7.2.2 Timing Diagrams                                                  | 129       |

|------------------------------------------------------------------------|-----------|

| 7.2.3 The Verification Problem                                         | 130       |

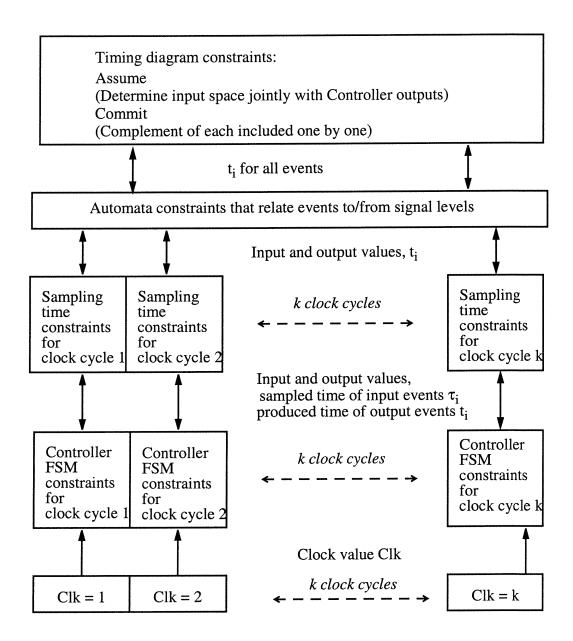

| 7.3 The Verification Method                                            | 136       |

| 7.3.1 The Set of Timed Traces of TDTA                                  | 137       |

| 7.3.2 The Set of Timed traces TR                                       | 139       |

| 7.3.3 Putting It All Together - the Verification Procedure             | 142       |

| 7. 4 Implementation in CLP(BNR) Prolog                                 | 144       |

| 7. 5 Efficiency Considerations and Experimental Results                | 150       |

| 7.5.1 Encoding state-transition relations                              | 150       |

| 7.5.2 Redundant constraints                                            | 151       |

| 7.5.3 Comparison with rule-based Prolog clauses                        | 151       |

| 7. 6 Example Results                                                   | 152       |

| napter 8: Verifying Two Continuous Write Cycles of an Interface Contro | oller 154 |

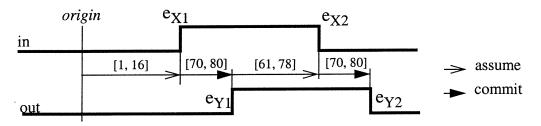

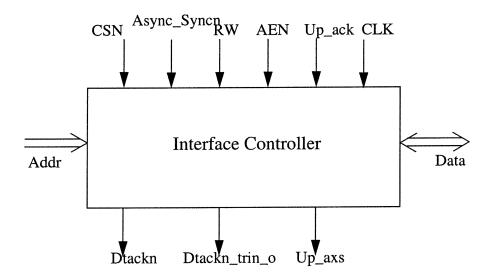

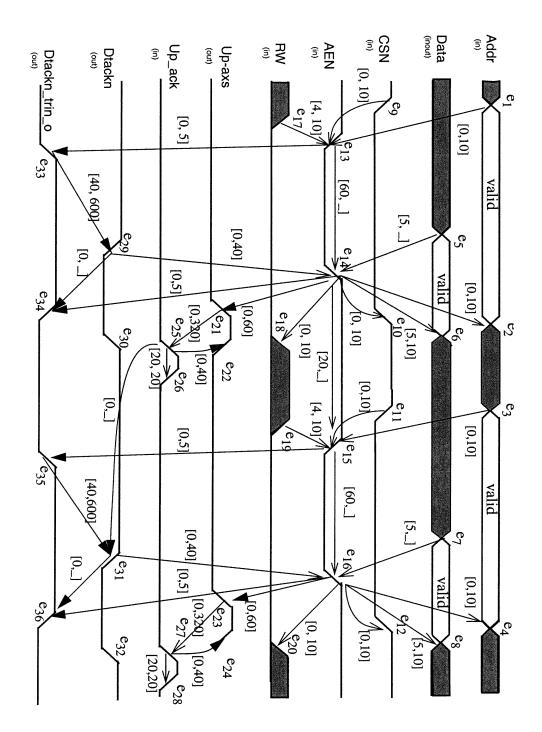

| 8.1 Specification of the Interface Controller                          | 155       |

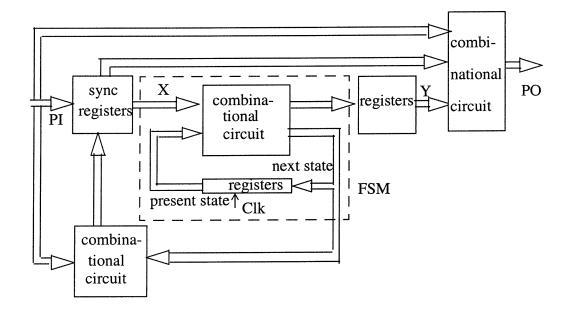

| 8.2 Implementation of the Controller                                   | 158       |

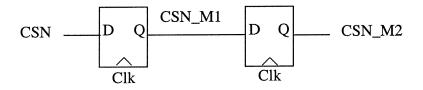

| 8.2.1 Synchronous Registers                                            | 159       |

| 8.2.2 Outputs of the Controller                                        | 160       |

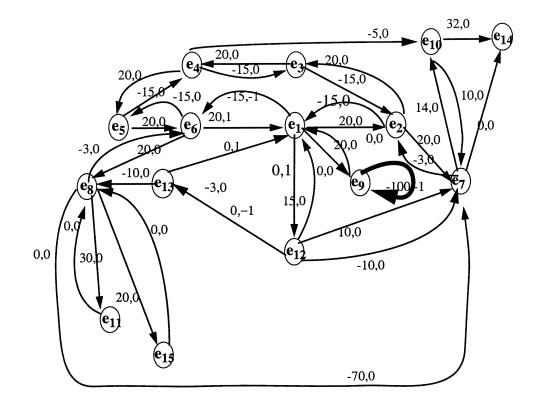

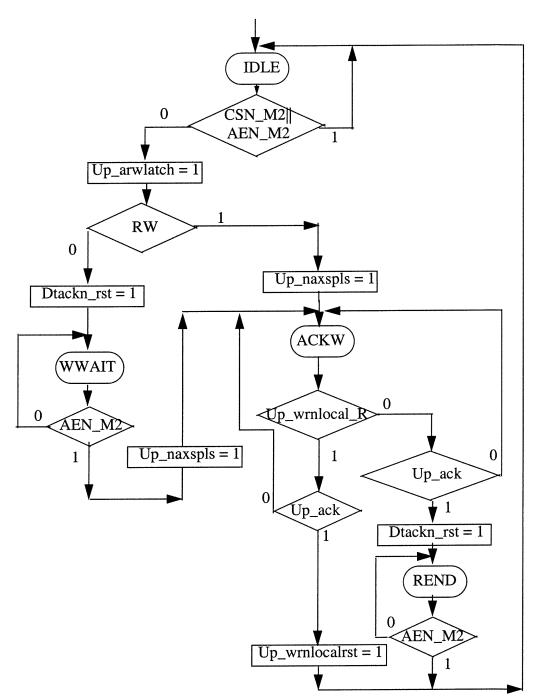

| 8.2.3 FSM Diagram                                                      | 160       |

| 8.3 Verification Procedure                                             | 163       |

| 8.4 Redundant constraints to improve efficiency                        | 164       |

| 8.5 Experimental Results and Conclusions                               | 165       |

| hapter 9: Conclusions and Future Work                                  | 167       |

| 9.1 Contributions                                                      | 167       |

| 9.2 Future Work                                                        | 168       |

| bliography                                                             | 170       |

| ppendix                                                                | 182       |

# List of Figures

| Figure 2.1: Hierarchical Loop over a leaf timing diagram                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2: A timing diagram specification of a RAM interface (end of a read cy-<br>cle - a write cycle - beginning of another read cycle)              |

| Figure 2.3: A timing diagram specification of a controller interface (End of a read<br>- write cycle - beginning of another read cycle)                 |

| Figure 3.1: HAAD hierarchy for a repetitive microprocessor READ from a memo-<br>ry                                                                      |

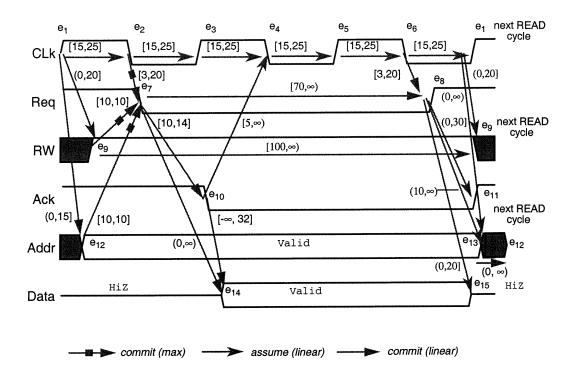

| Figure 3.2: A leaf timing diagram specifying one READ cycle of a microprocessor                                                                         |

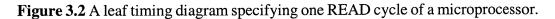

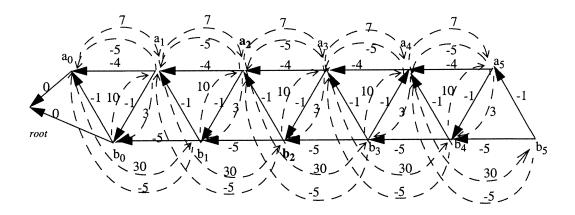

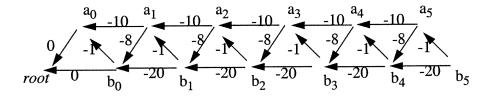

| Figure 3.3: A constraint graph specifying a repeated microprocessor READ from a memory derived from the HAAD specification in Figure 3.1 and Figure 3.2 |

| Figure 3.4: A well formed constraint graph 54                                                                                                           |

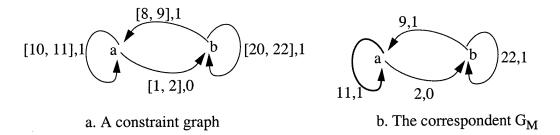

| Figure 4.1: A constraint graph $G^{f}$ for Example                                                                                                      |

| Figure 4.2: Gfm for constraint graph Gf in Figure 4.1                                                                                                   |

| Figure 4.3: An inconsistent constraint graph                                                                                                            |

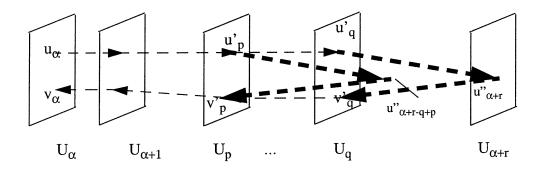

| Figure 5.1: The shortest path from $u_{\alpha}$ to $v_{\alpha}$                                                                                         |

| Figure 5.2: The constraint graph G for Example 5.1                                                                                                      |

| Figure 5.3: The graph $G_m^6$ of constraint graph in Figure 5.2                                                                                         |

| Figure 5.4: Gm of the constraint graph in Figure 3.3                                                                                                    |

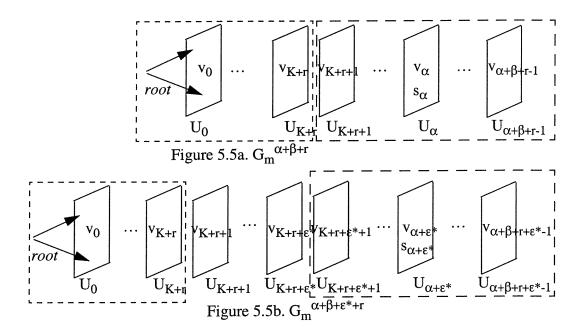

| Figure 5.5: The $G_m^{\alpha+\beta+r}$ and $G_m^{\alpha+\beta+\epsilon^*+r}$                        |

|-----------------------------------------------------------------------------------------------------|

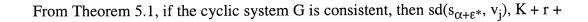

| Figure 6.1: Block partition of the constraint graph of Figure 3.3 107                               |

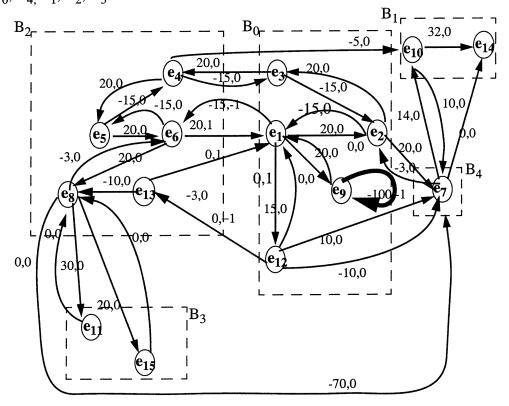

| Figure 6.2: A constraint graph G and its correspondent $G_M$ 115                                    |

| Figure 6.3: The $G_m^6$ of the constraint graph in Figure 6.2                                       |

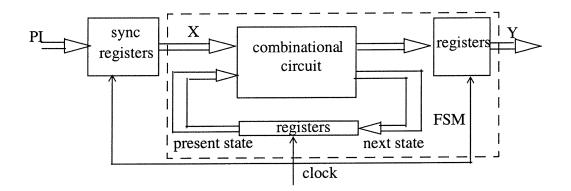

| Figure 7.1: An implementation of a pseudo-synchronous controller 129                                |

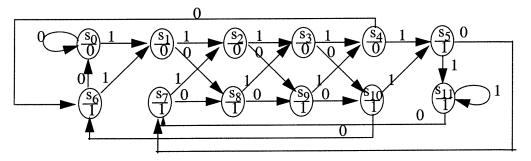

| Figure 7.2: Example FSM                                                                             |

| Figure 7.3: A TD specification for the example in Figure 7.2 130                                    |

| Figure 7.4: Constraints modeling the state transition of the FSM 140                                |

| Figure 7.5: Constraints modeling the state transitions of WTAY 141                                  |

| Figure 7.6: Constructing the constraint system 149                                                  |

| Figure 7.7: Constraints modeling the next state of the FSM after optimization (~ is a negation) 150 |

| Figure 8.1: Interface controller block diagram 155                                                  |

| Figure 8.2: The timing diagram specification of two asynchronous write cycles                       |

|                                                                                                     |

| Figure 8.3: The implementation of the interface controller 158                                      |

| Figure 8.4: Cascade registers sampling CSN 159                                                      |

| Figure 8.5: Asynchronous interface control FSM 161                                                  |

v

# List of Tables

| Table 2.1: Constraints for the timing diagram in Figure 2.2.          | 35  |

|-----------------------------------------------------------------------|-----|

| Table 2.2: Constraints for the timing diagram interface in Figure 2.3 | 36  |

| Table 7.1: Next State Function of the FSM in Figure 7.2               | 134 |

| Table 7.2: Experimental Results                                       | 153 |

| Table 8.1: Experimental Results of the Bus Controller                 | 165 |

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Eduard Cerny, for giving me the chance to work in the hardware verification area and for spending time on me in the last five and half years. Without his encouragement and guidance, I doubt that I can finally finish this work.

Second, I want to thank the examiners of the dissertation, especially Dr. Marco A. Escalante, for their insight and detailed comments.

I also want to thank my family members, my parents for taking care of my girl in the first two years after I came to Canada, my husband for his full support and sacrifice, and my lovely daughter Kathy who accompanied me in the university drawing her dreams on many weekends while I was working.

Last, I thank my friends. Many thanks to JiaHao Wu and his family, with whom I spent all my christmas evenings in the last six years, they made me feel home and let me see the hope of future. Many friends in Lab Lasso and CRT also deserve my thanks, they made my life in UdM more enjoyable and memorable.

# Glossary

| А                                                     | set of assume constraints                                                                                    |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| В                                                     | a block partition                                                                                            |

| С                                                     | set of commit constraints                                                                                    |

| E                                                     | set of events                                                                                                |

| E <sub>IN</sub>                                       | set of input events                                                                                          |

| E <sub>OUT</sub>                                      | set of output events                                                                                         |

| G = <e, r=""></e,>                                    | (cyclic) constraint graph                                                                                    |

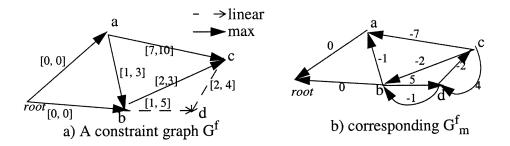

| $G^{f} = \langle E^{f}, R^{f} \rangle$                | acyclic finite constraint graph                                                                              |

| $G^{\alpha} = \langle E^{\alpha}, R^{\alpha} \rangle$ | $\alpha$ unfolded constraint graph of G                                                                      |

| $G^{\infty} = \langle E^{\infty}, R^{\infty} \rangle$ | infinite unfolded constraint graph of G                                                                      |

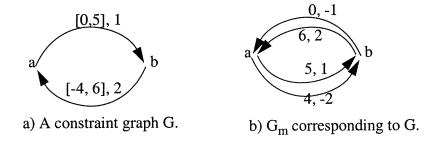

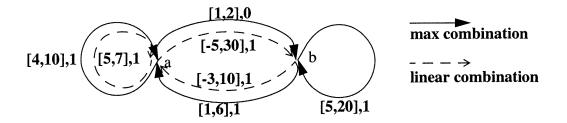

| $G_m = \langle E_m, R_m \rangle$                      | correspondent graph of G containing both bounds of linear constraints and lower bounds of latest constraints |

| $G_{M} = \langle E_{M}, R_{M} \rangle$                | correspondent graph of G containing both bounds of linear constraints and upper bounds of latest constraints |

| М                                                     | controller machine                                                                                           |

| R                                                     | set of rule edges                                                                                            |

| TD                                                    | timing diagram specification                                                                                 |

| TDTA                                                  | TD transition automaton                                                                                      |

| $U_{\alpha}$                                          | set of events in unfolding $\alpha$ of a constraint graph G                                                  |

| W                                                     | set of waveforms                                                                                             |

| WTA                                                   | waveform transition automaton                                                                                |

| WV                                                    | vector of waveform values of a TD                                                                            |

|                                                       |                                                                                                              |

| WV <sub>IN</sub>                                                               | vector of values of waveforms for input ports of a TD                                                |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| WV <sub>OUT</sub>                                                              | vector of values of waveforms for output ports of a TD                                               |

| e <sub>v</sub> , v                                                             | an event                                                                                             |

| $(e_u, e_v, [b_{uvmin}, B_{uvmax}])$                                           | timing constraint from $e_u$ to $e_v$ involved in linear combination                                 |

| (e <sub>u</sub> , e <sub>v</sub> , [d <sub>uvmin</sub> , D <sub>uvmax</sub> ]) | timing constraint from $e_u$ to $e_v$ involved in latest combination                                 |

| $(e_u, e_v, [T_{uvmin}, T_{uvmax}])$                                           | timing constraint from $e_u$ to $e_v$                                                                |

| m(v), sd(s,v)                                                                  | shortest distance from s to v                                                                        |

| msources(v)                                                                    | set of source events of constraints to v represented in $G_{\rm m}$ .                                |

| preds(v)                                                                       | set of source events of constraints to v involved in a max combination                               |

| trigs(B)                                                                       | triggers of B                                                                                        |

| $\delta(s, e)$                                                                 | minimum time separation from s to e                                                                  |

| $\Delta$ , $\Delta$ (s, e, $\beta$ )                                           | maximum time separation from s to e with index dif-<br>ference $\beta$ in a(cyclic) constraint graph |

| $\Delta^{m lpha}$                                                              | time separation from $s_{\alpha}$ to $e_{\alpha+\beta}$ in an acyclic graph                          |

| $\Delta(s, e)$                                                                 | time separation from s to e in an acyclic graph                                                      |

| R                                                                              | set of real                                                                                          |

| τ(ν)                                                                           | occurrence time of event v                                                                           |

ix

# **Chapter 1**

## Introduction

This work deals with interface timing verification problems in microelectronic systems. Microelectronic systems are normally implemented as a hierarchy of functional blocks. The blocks communicate with each other through interfaces. The functional blocks can be Application Specific Integrated Circuits (ASICs) or custom Integrated Circuits (ICs). With design reuse methodology, the ASICs and custom ICs can be intellectual properties (IPs). As a result, the systems are composed of blocks which are possibly designed and verified by different design teams from different organizations. This makes the system-level verification task to assure correctness of interfaces between blocks one of the most challenging problems in microelectronic system design.

Interfaces in a microelectronic system are places where different blocks meet and communicate with each other. An example of interfaces is the place where a microprocessor interacts with a memory. When blocks are connected to form a system, each block is connected through interfaces to the environment composed of the other blocks in the system. For a block to work properly in a system, the environment must respect assumptions made on the interface of the block. This verification can be achieved by a compatibility checking of the environment specification with respect to the specification of the block. If the environment is verified as incompatible with the interface specification of that block, then an interface transducer has to be designed to bridge the differences between the block and its environment. In this work, we are concerned with timing property (compatibility and other safety timing property) verification of interface specifications and the verification of implementations of interface controllers against their specifications.

We use mathematical methods to check the complete behaviour of interface speci-

fications and controller implementations. The work is thus in the domain of formal verification. We use a subset of Hierachical Annotated Action Diagrams (HAAD) [17] language, which was developed specifically for interface specification and verification in the laboratoire LASSO, University of Montreal, as the specification language of interfaces. We use finite state machine (FSM) derived from models in hardware description languages such as Verilog [68] or VHDL [75] as the implementation of the interface controllers.

In the first part of the work, we concentrate on algorithms for computing the maximum time separations between events in constraint graphs describing timing relationship between events in interface specifications. The algorithms are directly applicable for compatibility verification of interface specifications. They can also be applied to check other safety timing properties of interface specifications. In the second part of the work, we propose a methodology to verify the correctness of an interface controller implementation with respect to its specification. In both cases, we implemented the solution techniques in a constraint logic programming (CLP) environment based on Relational Interval Arithmetic (RIA) and domain narrowing [66].

In this introduction, we first describe in more detail the two problems of interest to us, namely timing verification of interface specifications and verification of realtime controllers against their specifications, in Sections 1.1 and 1.2, respectively. We then summarize the contributions of our work in Section 1.3, and give a plan of the thesis in Section 1.4.

### **1.1 Timing Verification of Interface Specifications**

The work on timing verification of interface specifications started about a decade ago. Several members in the laboratoire LASSO have worked on this subject ([17][20][36][37][50] etc.). Their work is mainly on semantics and timing verification of HAAD specifications. Their timing verification method is applicable to in-

terfaces specified by leaf HAAD specifications, a subset of the HAAD language[17]. There, the timing verification problems are solved by finding the maximum time separation of events in constraint graphs extracted from the specifications. The original motivation of the first part of our work is to extend the solution techniques of computing the maximum time separation to specifications modeling a more general cyclic interface behaviour (Loop over a leaf HAAD specification [17]). We show that the maximum time separation solution techniques developed in this thesis can be used to solve compatibility and other safety timing verification problems. We apply our solution technique to verify several safety timing properties of an interface specification modeling a repeated microprocessor READ access to a memory.

In this section, we first survey formal specification models related to system and timing property specifications. Then we give the reasons for adopting the HAAD language [17] as the formal specification language. After that, we summarize the work on the timing verification of interface specifications.

#### 1.1.1 Specification Languages

An interface specification describes the communication protocol on an interface. Traditionally, interface specifications in general specifications (GS) of a device are given in the form of timing diagrams. There are normally additional textual annotations written in natural languages such as English, and the timing constraints usually appear in tables describing timing relationships between signal transitions on ports of the interfaces. The annotations are necessary for designers to understand the specification, but they make it difficult to model the specification in a formal language for analysis, because there is no formal semantics for such descriptions. In the following, we first summarize related formal specification languages, and then illustrate why these models are not powerful enough to specify interface behaviours directly.

In the literature, there are many formal specification models such as Timed Temporal Logics, Real-Time Logics, Timed Process Algebras, Timed Automata, Time Trace Structures, Timed Petri Nets, etc., which can model real-time systems and properties. These timed specification models have been used to specify and verify timing properties in real time systems, software engineering, and VLSI CAD communities. In the following, we briefly describe these timed models.

Temporal Logics are languages based on propositional or first order logic with special operators for reasoning about qualitative time (e.g.,  $\diamond$  for "eventually" and  $\Box$ for "always"). Different mechanisms have been used to include quantitative time information in temporal logics. The popular ones include the use of bounded-time temporal operators (e.g.,  $\diamond_{[2,4]}$  meaning "eventually within 2 to 4 time units."), introduction of an explicit clock variable, and temporal quantification of time variables. Examples that use bounded temporal operators are Real-Time Computational Tree Logic (RTCTL) [24], Timed Computational Tree Logic (TCTL) [2], Metric Temporal Logic (MTL) [54]. An example of using explicit clock variables is Real-Time Temporal Logic (RTTL) [67]. An example of using temporal quantification of time variables is Timed Propositional Temporal Logic (TPTL) [3].

Real Time Logics (RTL) was developed by Jahanian and Mok to specify, verify, and synthesize real time systems [46]. RTL is a restricted form of First Order Logic. A special occurrence function is used to keep track of the n-th occurrence of an event, which leads to a fairly expressive logic. However, theories in RTL are undecidable. In [45], decision algorithms were developed to verify safety timing properties for systems expressed in a subset of RTL. Later in [63], Millet extended the work in [45] for verifying safety timing properties expressed in an extended subset of RTL. To specify more complex real time systems, a hierarchical graphical specification language Modechart was developed [46] with RTL as its semantics. Modes and transitions are used as the basic structure representing the control state and the control flow of a specification. Since the underlying semantics of Mode-

chart is RTL, general theories in Modechart are undecidable, and whether a particular Modechart satisfies a particular RTL formula is also undecidable. A Modechart toolset [46] was developed for specifying and verifying safety timing properties for real time systems. The tool verifies whether a timing property expressed in RTL satisfies a real time system described in Modechart. Several subsets of RTL in which the verification problem is decidable were described in [76]. In the Modechart toolset, a model checking technique is used to check the truth of a safety timing property expressed in RTL with respect to a computation graph which is a finite representation of all the behaviours of the Modechart specification. Like all data structures used in model checking, the computation graph suffers from the state explosion problem.

Process algebra such as CCS, CSP and ACP were developed for describing and analysing communicating concurrently executing systems. A process algebra consists of a language with precisely defined semantics and a notion of equivalence. To verify a system using a process algebra, one writes a specification as an abstract process and an implementation as a detailed process. To prove correctness, the two processes are shown to be equivalent or a preorder between the two processes is shown. Recently, several timed process algebra were developed by adding the notion of time and including a set of timed operators to the untimed process algebras. Extensions of CCS include the Algebra of Communicating Shared Resources, ACSR [12][56]; Temporal CCS [64]; Timed CCS [82]; Algebra of Timed Processes ATP [65]; and Algebra of Communication Timing Charts (ACTC) [8] which was proposed especially for the specification and verification of interface behaviours. Extensions of CSP include Timed CSP [73] and Timed LOTOS [10]. The latter is based on CSP and was applied to several industrial projects. ACP was extended to Timed ACP in [6], [34].

Alur and Dill [1] proposed an extension of Büchi and Müller  $\omega$ -automata to include metric dense time. Transitions are labelled by time constraints on 'clock variables', and while executing a transition, a clock can be reset to zero. A trace is accepted by

a timed automaton if its transitions are performed at times that satisfy all clock constraints. A tool, KRONOS [60], was developed to assist the user with validating complex real-time systems. The tool checks whether a real-time system modelled by a timed automaton satisfies a timing property specified by a TCTL formula. KRONOS was used to verify a variety of time-dependent protocols and MOS circuits [60].

Dill [27] used trace theory to specify and verify speed-independent circuits. In trace theory, circuit behaviour is described by sets of traces, where a trace is a sequence of transitions. Dill's approach does not include metric integrate time in the model. Burch [14] extended Dill's work by incorporating discrete time and various delay models into the trace theory analysis, aiming at hardware design verification. Automata-based techniques were used to do the verification. The run time is exponential in the number of components and heavily dependent on the size of the delay values in the model.

Petri nets are a graph model that was also used extensively to model concurrent systems. They are bi-partite graphs composed of two types of nodes called places and transitions. Many different models of time were defined for Petri nets, mostly by imposing timing constraints on the enabling and firing rules of untimed Petri nets. These constraints can be represented by constants or functions. The former includes Timed Petri nets which treat a timing constraint as a single delay[40], [70], [71], Time Petri nets which treat a timing constraint as a time interval defined by a lower and an upper bound [59], [61], [72], and Timing Constraint Petri nets which associate each place with a time interval and each transition with a duration [77]. The latter includes Stochastic Petri nets [58] which treat a timing constraint as a probability function of the transition firing rate, and ER nets [32] which treat a timing constraint as a function of coloured tokens in input places. Time Petri nets were used for analysing the recoverability of communication protocols and the safety of real time systems. Timed and Stochastic Petri nets have also been used for performance evaluation. Timing Constraint Petri nets which are more like the graphical representation of the subset of RTL described in [45] were used to check schedulability of a specification, where a specification is defined as schedulable if every event in the system can be assigned an occurrence time satisfying all the imposed timing constraints [77].

In [29][30][31], Escalante et al developed an "interface specification" to model behavior of a component in a system. An interface specification consists of two parts: a timed signal transition graph (a probablistic timed petri net), and a restriction on the component's environment (a set of constraint rules). Then the system behaviour is described by "merging" interface specifications of all the components in the system. They proposed a verification technique to check time consistency for the socalled "closed systems", a type of systems that are self-contained and do not interact with any environment. In their approach, all the delays are represented by random variables.

Unfortunately, it is far from trivial to specify interface timing directly by the above formal timed specification models. The reasons are twofold. On the one hand, it is difficult to extract a formal interface specification from the data sheet in the GS. On the other hand, timing constraints describing the timing relationship on interfaces in the GS such as latest, earliest and linear constraint combinations, and delay correlation between constraints which are necessary to reason about interface timing behaviour are too complex when expressed by the existing specification models.

Efforts have been made in two directions to address these problems. One is to formalize timing diagrams, and the other one is to extend formal specification models to handle complicated timing constraints. The combination of the efforts in these two directions lead to a formal language called Hierachical Annotated Action Diagram (HAAD) [17] which was inspired by Timing Diagrams and Process Algebras.

The HAAD language was developed to specify systems with complex timing and functional behaviour on interfaces. In the HAAD language, timing information on

interfaces is shown through timing constraints over actions on interface ports and internal signals, while the functional behaviour on interfaces is described by annotating actions using variables, predicates and procedures. In this way, the timing information is presented orthogonally to the functional behaviour. Formal semantics has been defined for the HAAD language without annotation. This is sufficient as a specification language for the purpose of formal timing verification. In this work, we are only interested in the timing behaviour on interfaces, we thus adopt the HAAD specification without annotation as the interface specification language (from now on, we will use "HAAD" instead of "HAAD without annotation" for notational simplification).

### 1.1.2 Timing Properties on Interfaces

To the best of our knowledge, Brozozowski et al [13] are the first ones to address the problems of checking timing properties on interface specifications. In [13] and [35], they pointed out that constraints that require the device environment to provide the proper inputs (denoted as assume constraints) and those that specify what the environment can expect from the device if the input conditions are met (denoted as commit constraints) should be distinguished. They proposed two timing properties that should be verified to guarantee the correct interaction between connected blocks in a system. The two properties are consistency and satisfiablility. A timing diagram specification is consistent if occurrence times can be assigned to all actions without violating any constraints. Interface satisfiablility of two timing diagram specifications is defined to hold if the time separation between each pair of actions implied by a commit constraint of one timing diagram is tighter than the separation between the same pair of actions implied by the assume constraints of the other timing diagram.

It was demonstrated later by Cerny et al [17][20][50] that the notions of consistency and satisfiablility of timing diagrams in [13][35] are not sufficient for verifying that two or more blocks will interact correctly when built according to their local specifications. They define formal operational semantics of the leaf TDs based on a block machine which is derived from interface specifications in the form of leaf TDs. They give sufficient conditions in [50] for a specification to be realizable (causal) and further prove that a block machine derived from a realizable specification has the same timed traces as those from the specification itself. They define the compatibility of an interface specification as follows:

All combinations of the block machines derived from realizable specification are free of dead lock.

They guarantee that a causal implementation of compatible specifications can interact correctly in a system. They further proposed compatibility conditions for leaf timing diagrams of a HAAD specification with linear timing constraints [17][50]. It is illustrated there that the conditions can be verified by finding the maximum time separation between events in constraint graphs transformed from the interface specifications. The work was extended by Girodias et al. [36][37] to verify the compatibility of leaf timing diagrams of HAAD specifications containing linear, max (latest) and min (earliest) constraints. The solution technique can also deal with delay correlation between the timing constraints.

In a HAAD specification, leaf timing diagrams model elementary operations on the interface (e.g., READ, WRITE of a processor to a memory). The complete interface behaviour is modeled by a hierarchy of leaf timing diagrams using composition operators. The solution techniques in the previous work ([17][20][50]) can only verify behaviour modeling elementary operations on interfaces.

We are interested in verifying timing properties of interface specifications which can describe more general interface behaviours than those described in [36][37] (e.g., repeated READ or WRITE of a microprocessor to a memory). More specifically, we are interested in verifying interface specifications modeled by the HAAD language containing hierarchical operators. In the first part of this work, we consider "Loop" operator over a leaf action diagram (a timing diagram), a type of specification which can describe an infinite repetitive behaviour without a choice on an interface.

#### **1.2 Verification of Interface Controllers Against Their Specifications**

In this section, we introduce the problem of verifying an implementation of an interface controller against its specification and then discuss related literature.

In the design of Systems on a Chip (SoC) from predesigned building blocks, it is important to assure that these blocks can communicate correctly. This means that much effort is spent on designing and verifying bus controllers and other communication control logic. Even if the processor bus protocol is asynchronous, the controllers of such a bus in the connecting devices are often designed as synchronous finite state machine (FSM), operating on synchronized input signals from the bus. Timing simulation is the usual method for verifying that the controller can operate in the full range of the bus protocol. This is generally far from satisfactory due to the large number of different timing situations that could exist on the input signals. To perform this verification exhaustively, yet without the full explicit enumeration of all situations, we propose a method based on Constraint Logic Programming for verifying whether a pseudo-synchronous (sampled input/output) finite-state machine (FSM) implementation of a real-time controller satisfies its leaf TD specification.

The problem can be defined as follows: given an implementation of an interface controller in the form of an FSM, a clock frequency and a specification in the form of a leaf TD, we check whether the FSM implementation always produces the correct outputs and within the timing constraints stated in the specification, provided that the inputs meet the assumptions as also stated in the specification.

Although there are many published results regarding static timing verification of

synchronous sequential circuits, most of them are concerned with set-up and hold time checks on sequential elements (flip-flops, latches, memories etc.). In our work, we are interested in the timing information as determined by the functionality of the circuit, i.e., a mixture of timing and behavioural verification over a number of clock cycles. This kind of verification could potentially be carried out using models based on Timed Automata (TA) [2] or timed Petri Nets [40], however, the TA models and the accompanying verification techniques based on reachability analysis of the derived region graphs are unnecessarily difficult and complex in this practical context of verifying realistic RTL designs of hardware interface controllers.

Clocksin [26] at University of Cambridge used logic programming to carry out simulation of synchronous sequential circuits. He used rule based unit clauses which resemble standard truth tables to model relations in the modules of the circuit to be simulated. As we shall show, such an approach leads to exponential time explosion, because most of the possible FSM executions are enumerated. Instead, we use constraints rather than rule based clauses to model the execution of sequential circuits in real time. This consists of unrolling the FSM over a sufficient number of clock cycles to cover the range of time implied by the TD specification, expressing the unrolled instances of the FSM as a series of constraints. We then link these constraints to the timing constraints from the TD using a set of automata that convert event occurrences on signals in the TD to signal levels required/produced by the controller FSM. In addition, since we inherently deal with uncertainty intervals as to the time of occurrence of events, we can carry out this verification under variations in the clock frequency and delay correlation, similarly as in [17][36].

The representation of the sets of states, the output traces of the TD automata, and the implementation FSM is compact (linear with time) in terms of the number of constraints, while the number of traces thus characterized may grow exponentially with time. Although we verify only finite behaviours as described by the leaf timing diagram, most realistic bus protocols usually return to an initial state after executing a particular operation cycle. We can thus verify that at the end of the finite trace the final state of the automaton and the maximum separations of the last events on each port correspond to the initial state. In a more general approach, we plan in future work to estimate an upper bound on the number of unfoldings required of the combined TD plus FSM system before all the maximum event separations start to repeat. The approach can be compared to model checking on finite computations derived from a Kripke structure using a satisfiablility procedure [7].

#### **1.3 Contributions of the Work**

The contributions of this dissertation can be summarised in three main points.

a) We developed a method for performing compatibility and other safety timing property verification of interfaces specified by a HAAD language in the form of Loop over leaf TDs. We solve the verification problems by providing algorithms for computing the maximum time separation of events in infinite constraint graphs derived from the specifications.

b) We propose a method for verifying the correctness of an interface implementation in the form of an FSM against its leaf HAAD specification.

c) Applications: We verified causality and several safety timing properties on a HAAD specification modeling a repeated microprocessor READ operation (inspired by MC68360) from a memory; we also verified the FSM implementation of a bus controller with respect to its leaf HAAD specification.

Regarding the algorithms of finding the maximum timing separation between events in constraint graphs transformed from HAAD specifications in the form of Loop over leaf TDs, we show the way to transform the HAAD specification with linear-plus-latest timing constraints to constraint graphs. We derive well-formedness conditions of these constraint graphs, and define the maximum time separation problem in the constraint graphs. We propose algorithms for computing the maximum time separations in constraint graphs with linear-only, linear-plus-latest, and restricted linear-plus-latest constraints which relates to realizable (causal) specifications.

In the case of linear-only constraint systems, the proposed algorithm is polynomial in the number of events in the constraint graph which is also the number of events in the leaf timing diagram of the HAAD specification.

In the case of linear-plus-latest constraints, we show that the time separations will become periodic functions of event indices. The number of unfoldings needed for the time separations to become periodic depends on the delay values in the specification. We give a sufficient condition to determine when this happens and propose an algorithm for computing the maximum time separation. The algorithm consists of a step by step unfolding of the constraint graph and computing the time separation in the unfolded constraint graphs. The computation continues until the time separation becomes a periodic function and no further unfolding is need. Since the number of unfoldings required for the time separation to become periodic depends on the delay values in the specification, the algorithm is not practical for real complex problems. We then restrict the linear-plus-latest constraint graphs to causal ones which correspond to realizable specifications. In such causal constraint graphs, we are able to give an upper bound on the number of unfoldings that one has to consider in order to compute the maximum time separation. Unlike the case of linear-only systems where the upper bound is dependent only on the number of events in the constraint graph, the upper bound here is also dependent on the delay values in the specification. But the value of the upper bound can be determined after a time separation calculation in a finite process graph containing events and constraints of a number of unfoldings. For most practical application, this number is fairly small. We then obtain an exact and efficient algorithm for computing the maximum time separation in causal constraint graphs with linear and latest constraints.

Regarding the problem of verifying the correctness of real time interface controllers against their specifications, the contributions can be stated in more detail as follows:

- Modeling a timing diagram specification as communicating "TD" automata that accept event traces respecting the timing constraints;

- The representation of the finite unfolding of the implementation FSM, the finite execution of the TD automata and timing requirements in the form of constraints;

- Formulating the FSM versus TD timing verification problem as a consistency check of a series of constraint systems;

- Implementation of the method using Constraint Logic Programming within a Relational Interval Arithmetic environment;

- Acceleration of the convergence of the implemented algorithm by adding redundant constraints.

We applied the solution techniques to real designs. We verified the causality and two safety timing properties of an interface specification modeling repeated microprocessor READ operations (inspired by MC68360) from a memory. It is based on computing the maximum time separation of events in restricted constraint graphs containing linear-plus-latest constraints. We also verified that the FSM model of a real-time controller extracted from its RTL Verilog description satisfies its timing diagram specification.

Part of this work has been published in [18] [19] [49].

### **1.4 Organization of the Thesis**

The thesis consists of two major parts. The first part, Chapter 2 through Chapter 6, describes algorithms for solving the maximum time separation problem in constraint graphs transformed from HAAD specifications, and their application in safety timing property verification of interface specifications. The second part, Chapter 7 and Chapter 8 describes a solution technique for verifying pseudo-synchronous interface controllers against their leaf HAAD specifications, and its application to a real industrial design.

Chapter 2 is an introduction to the first part of the work. We first describe HAAD specifications, and then demonstrate that for a block in a system to interact correctly, the interface specifications involved must satisfy the causality and compatibility conditions. We then show that the causality and compatibility conditions can be verified by the maximum time separations between events in constraint graphs transformed from HAAD specifications.

In Chapter 3, we define the constraint graphs extracted from HAAD specifications in the form of Loop over leaf timing diagrams. We then give well-formedness conditions of such graphs and formally define the problem of maximum time separation of events in such constraint graphs. We show through a real example that the maximum time separation can be used to verify other interesting safety timing properties on interfaces.

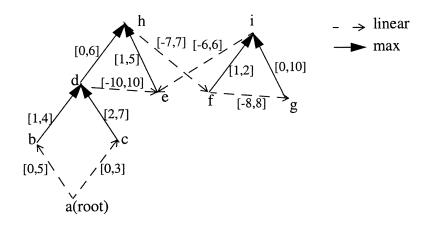

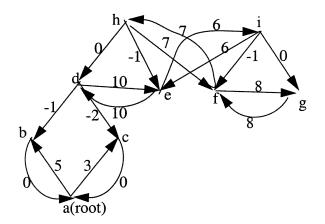

In Chapter 4, we develop and prove the correctness of an algorithm for computing the time separation of events in finite unfolded constraint graphs. The algorithm is a variation of the one proposed by McMillan and Dill [62]. The difference between the two algorithms is that ours finds the maximum time separation from one start event to all the events in the graph while the one in [62] finds the time separations between all pairs of events in the graph. We use extensively the variation algorithm to solve the maximum time separation problem in the infinite constraint graphs of interest in Chapter 5 and Chapter 6.

In Chapter 5, we discuss algorithms for finding the maximum time separation of events in constraint graphs extracted from HAAD specification in the form of Loop over leaf timing diagrams. In the case of linear-only systems, we propose and prove the correctness of an algorithm which is polynomial with the number of events in the leaf timing diagrams. In the case of linear-plus-latest systems, we show that the maximum time separation will become periodic functions of event occurrence index. We give a sufficient condition to check when this happens. The speed of convergence of the iteration algorithm depends on delay values in the specification, which makes the algorithm impractical for real complex problems.

In Chapter 6, we restrict the constraint graph in such a way that events in unfolded constraint graphs can be partitioned into a set of topologically ordered blocks that respect the causality conditions. The restricted graphs reflect realizable designs and can be used to model most realistic systems. We propose and prove a practical and exact algorithm of computing the maximum time separations between events in the restricted constraint graphs. We then simplify the algorithm of finding a time separation in a restricted finite graph with linear-plus-latest constraints. After that, we derive an algorithm of computing the maximum time separation in causal cyclic constraint graphs. Since the causality conditions of constraint graphs need the information of the maximum time separation between events, there is an interleaving between computing the maximum time separations and the causal conditions of the cyclic constraint graph. We give sufficient causal conditions based on the maximum time separation between events under the assumption that the system is causal. Finally, we apply the solution technique to verify causality and two safety timing properties of interface specifications modeling continuous READ of the microprocessor from the memory.

In Chapter 7, we describe the methodology for verifying finite state machine (FSM) implementation of a real-time controller against its timing diagram specification. We use constraints to model the execution of the implementation in real time. We solve the problem by formulating the verification problem as a consistency check-ing of a constraint system. The consistency check is implemented in a Constraint Logic Programming environment (CLP) based on relational interval arithmetic (RIA) [66].

In Chapter 8, we apply the method developed in Chapter 7 to an industrial design. We verify that the implementation of a bus controller meets the specification under all timing situations.

In Chapter 9, we conclude the work and give some future directions of research.

# Chapter 2

## **Interface Specifications and Verification**

This chapter serves as an introduction to the first part of the work (Chapter 2 through Chapter 6). It consists of 4 sections. In Section 2.1, we describe specifications of interfaces using Hierarchical Annotated Action Diagram (HAAD). In Section 2.2, we summarize the causality and compatibility conditions of interface specifications. In Section 2.3, we show that these conditions can be verified by finding the maximum time separations between pairs of events in constraint graphs derived from interface specifications. In Section 2.4, we give a survey of the work related to computing the maximum time separations.

#### **2.1 HAAD Specifications of Interfaces**

Timing Diagrams as given in the data sheets of GS have been used for decades by designers to describe timing relations between signal transitions on interface ports. They are easy to understand, but they are an informal language with no formal semantics to interpret them unambiguously.

In [11], Borriello proposed a formalized timing diagram. A formalized timing diagram is a hierarchy of segments which consist of a collection of events and timing constraints between the events. It supports the hierarchical operators: Parallel, Choice, Sequential Composition and Loop. It has been used for the synthesis of interface transducers.

However, since formalized timing diagrams do not distinguish the constraints that characterize the assumptions on the environment and those produced or guaranteed by the device, the formalized timing diagrams cannot specify the assumption and reaction relationship between signal transitions on interface ports. In [53], a structured language, Hierarchical Annotated Action Diagrams (HAAD) were developed for describing the behaviour of digital systems as seen from their interfaces. In the HAAD language, the interface behaviour is captured as a hierarchy of timing diagrams. In the hierarchy, leaf timing diagrams model elementary behaviours (operations such as READ, WRITE), complex behaviours are formed hierarchically using composition operators such as Concatenation, delayed Choice, Concurrency, Loop, and Exception. In the following, we first introduce the Loop operator and then give a definition of leaf timing diagrams. We do not include the definitions of the other hierachical operators here, since they are not used later on in this thesis. The interested reader can refer to [17] for the formal definition of all the hierarchical operators and formal semantics of the HAAD language.

A Loop over a leaf timing diagram as shown in Figure 2.1 models the following interface behavior: the same behaviour described in the leaf TD repeats an infinite number of times.

Figure 2.1 Hierarchical Loop over a leaf timing diagram

A leaf timing diagram TD is composed of a set of waveforms and a set of timing constraints. A waveform is a sequence of signal transitions (events)<sup>1</sup> between steady state signal values. Timing constraints relate waveform events. The constraints are of two possible intents: assume and commit [20]. Assume constraints express assumptions on the occurrence times of input events, and commit constraints define the limits on occurrence times of the output events to be satisfied by

<sup>&</sup>lt;sup>1</sup>A signal transition on a waveform corresponds to an action in HAAD specification and an event in a leaf TD specification

the implementation under the input assumptions. More formally, a leaf timing diagram TD is defined as follows [17].

**Definition 2.1:** A leaf timing diagram TD is a 4-tuple, TD = (W, E, A, C), where

- W=  $\{w_1, ..., w_m\}$  is the set of waveforms;

- $E = \{e_1, ..., e_n\}$  is the set of events on the waveforms;

- $A = \{A_1, ..., A_p\}$  is the set of assume constraints;

- $C = \{C_1, ..., C_q\}$  is the set of commit constraints.

A timing constraint ( $e_u$ ,  $e_v$ , [ $T_{uvmin}$ ,  $T_{uvmax}$ ])  $\in A \cup C$ ,  $T_{uvmin} \leq T_{uvmax}$ ,  $T_{uvmin}$ ,  $T_{u-vmax} \in \Re$  (the set of real numbers), from  $e_u$  (the source event of the constraint) to  $e_v$  (the sink event) represents the following inequality between the occurrence times  $t_u$  and  $t_v$  of  $e_u$  and  $e_v$ , respectively:

$$T_{uvmin} \le t_v - t_u \le T_{uvmax}.$$

(2.1)

A timing constraint can be one of two types, that is, precedence or concurrence constraint. A precedence constraint  $(T_{uvmin} \ge 0)$  from  $e_u$  to  $e_v$  denotes that  $e_u$  must precede  $e_v$  in occurrence time, while a concurrence constraint  $(T_{uvmin} \le 0, T_{uvmax} \ge 0)$ from  $e_u$  to  $e_v$  means that there is no definite order in the occurrence times of the two events. In a TD, it is possible that two or more constraints sink at the same event  $e_v$ , all these constraints are combined together to determine the occurrence time of  $e_v$ . For an event  $e_v$ , let U be the set of all u such that  $e_u$  is an event and  $(e_u, e_v, [T_{uvmin}, T_{uvmax}])$  is a constraint to  $e_v$ . A HAAD specification allows three types of constraint combinations defined as follows. **Definition 2.2:** If the constraints to  $e_v$  are combined using a linear operator, then the occurrence time  $t_v$  must lie within the intersection of the intervals  $[t_u + T_{uvmin}, t_u + T_{uvmax}]$ , for all  $u \in U$ . In other words, all the constraints to  $e_v$  are to be satisfied simultaneously as given in (2.2).

$$\max_{u \in U} \{t_u + T_{uvmin}\} \le t_v \le \min_{u \in U} \{t_u + T_{uvmax}\}$$

(2.2)

**Definition 2.3:** If the constraints to  $e_v$  are combined using the max operator, then the earliest (latest) occurrence time  $t_v$  is determined by the source event  $e_u$  which makes  $t_u + T_{uvmin} (t_u + T_{uvmax})$  be the maximum among all the u's as given in (2.3). All the constraints to  $e_v$  must be precedence.

$$\max_{u \in U} \{t_u + T_{uvmin}\} \le t_v \le \max_{u \in U} \{t_u + T_{uvmax}\}.$$

(2.3)

This composition can model, for instance, the timing behaviour of a rising transition on the output of an AND gate caused by the rising transitions on the inputs of the gate.

**Definition 2.4:** If the constraints to  $e_v$  are combined using the min operator, then the earliest (latest) occurrence time  $t_v$  is determined by the source event  $e_u$  which makes  $t_u + T_{uvmin} (t_u + T_{uvmax})$  be the minimum among all the u's as given in (2.4). All the constraints from  $e_u$  to  $e_v$  must be precedence.

$$\min_{\mathbf{u}\in\mathbf{U}}\{\mathbf{t}_{\mathbf{u}}+\mathbf{T}_{\mathbf{u}\mathbf{v}\min}\} \le \mathbf{t}_{\mathbf{v}} \le \min_{\mathbf{u}\in\mathbf{U}}\{\mathbf{t}_{\mathbf{u}}+\mathbf{T}_{\mathbf{u}\mathbf{v}\max}\}.$$

(2.4)

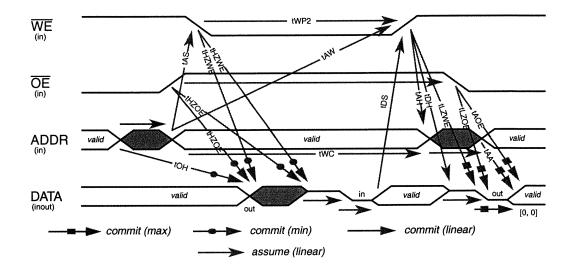

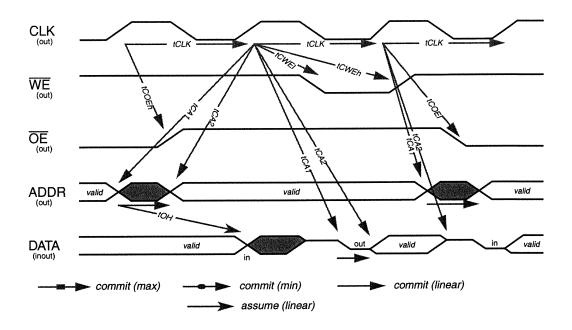

This composition can model, for instance, the timing behaviour of a falling transition on the output of an AND gate caused by falling transitions on the inputs of the gate. Figure 2.2 and Figure 2.3 show leaf timing diagrams of a memory device and of a memory controller. The operations on the interfaces are an end of a read cycle, followed by a write cycle and then beginning of another read cycle.

Figure 2.2 A timing diagram specification of a RAM interface (end of a read cycle - a write cycle - beginning of another read cycle)

| Name | Delay Value (ns) | Name  | Delay Value (ns) |

|------|------------------|-------|------------------|

| tAA  | (0, 10]          | tHZOE | (0,∞)            |

| tAH  | (0,∞)            | tHZWE | (0, 7]           |

| tAOE | (0, 7]           | tLZOE | (0, 7]           |

| tAS  | (0,∞)            | tLZWE | (9,∞)            |

| tAW  | (10, ∞)          | tOH   | (9, ∞)           |

| tDH  | (0,∞)            | tWC   | (15,∞)           |

| tDS  | (8,∞)            | tWP2  | (12,∞)           |

Table 2.1: Constraints for the timing diagram in Figure 2.2

**Figure 2.3** A timing diagram specification of a controller interface (End of a read - write cycle - beginning of another read cycle)

|   | Name  | Delay Value (ns) | Name  | Delay Value (ns) |

|---|-------|------------------|-------|------------------|

| F | tCA1  | [18, 19.8]       | tCOEh | [31.8, 33]       |

|   | tCA2  | [18, 20]         | tCWEl | [22, 28]         |

|   | tCLK  | [25.73, 25.73]   | tCWEh | [38.8, 45]       |

|   | tCOEl | [16, 18]         | tOH   | (3,∞)            |

Table 2.2: Constraints for the timing diagram interface in Figure 2.3

# 2.2 Verification of Interface Specifications

In this section, we summarize the formal semantics and the verification of causality and compatibility of interface specifications as discussed in [36], [50]. The semantics of causality and compatibility guarantees that causal HAAD specifications are realizable (can be simulated by a causal system [50]) and components of compatible specifications can interoperate correctly when forming a system. We show that causality and compatibility conditions can be verified by computing the maximum time separations between events in constraint graphs extracted from the specifications.

In [50], the realizability of a leaf HAAD specification is stated in terms of the existence of a causal block machine derived from the specification, the derivation is based on a partition of the action set of the specification. The authors in [50] proved that all causal block machines derived from an action diagram have the same timed trace set as that of the TD specification. The compatibility of an interface specification is then defined as the absence of dead lock when any combinations of causal block machines are executed. It is thus guaranteed that the components included in a compatible specification can interoperate correctly in a system. In the case of systems with linear-only constraints, the authors in [50] give the compatibility conditions. The compatibility conditions consists of realizability of each interface specification, consistency and satisfiability of the composition of the interface specifications. The work is extended later in [36] to systems specified by leaf TDs containing linear, latest, earliest constraints and also delay correlation.

In the following, we summarize the consistency, causality and compatibility conditions from [13][36][50] which are applicable to leaf HAAD specifications.

The consistency condition of a timing diagram is as given in [13] and [35]: A TD is consistent if all events in the TD can be assigned an occurrence time without violating any timing constraint.

To state causality and compatibility conditions, we first give a definition of the maximum and minimum time separation between events satisfying all constraints in a TD.

**Definition 2.5:** Given a TD = (W, E, A, C), a start event s and an end event e, s, e  $\in$  E, the maximum ( $\Delta$ (s, e)) and the minimum ( $\delta$ (s, e)) time separations from s to e are defined as:

$$\Delta(s, e) = \max(\tau(e) - \tau(s)) \tag{2.5}$$

and

$$\delta(s, e) = \min(\tau(e) - \tau(s)) \tag{2.6}$$

subject to the constraints in  $A \cup C$

The causality conditions of a TD are developed in [50]. We need the following definitions to state the causality conditions.

**Definition 2.6:** A block B of a TD = (W, E, A, C) is a nonempty subset of events in E, i.e.,  $B \subseteq E$ . A block partition P of a TD is a set of disjoint blocks of all the events in E, i.e., a collection of blocks satisfying the following two conditions.

a)  $\forall B_1, B_2 \in P$ , either  $B_1 = B_2$  or  $B_1 \cap B_2 = \emptyset$  and

b)  $\cup_{B \in P} B = E$ .

For every block B of a partition P, there are **triggers** and **local constraints** of the block. A **trigger** of a block is the source event in another block whose sink event is in the block, i.e.,

$$\operatorname{trigs}(B) = \{ e_u \mid (e_u, e_v, [T_{uvmin}, T_{uvmax}]) \in A \cup C, e_u \notin B \text{ and } e_v \in B \}.$$

(2.7)

The **local constraints** of a block B are the constraints that either relate events in the block or relate triggers of the block to the events in the block, i.e., the local constraints are  $\{(e_u, e_v, [T_{uvmin}, T_{uvmax}]) \in A \cup C \mid e_u \in trigs(B) \cup B and e_v \in B\}$ . Let B(v) denote the block containing event  $e_v$ .

The causality conditions of a TD can now be stated as follows ([20][50]): A leaf TD is causal if a partition P of the TD satisfying the following three conditions can be found.

Causality Condition 1: *In* and *out* actions do not share a block B of P, where *In* (*out*) actions correspond to signal transitions on input (output) ports,

Causality Condition 2: For all events  $e_v \in B$  and for all triggers  $e_u \in trigs(B(v))$ ,

$$\delta(\mathbf{e}_{\mathrm{v}}, \mathbf{e}_{\mathrm{u}}) \le 0, \tag{2.8}$$

where  $\delta(e_v, e_u)$  is the minimum time separation from  $e_v$  to  $e_u$  satisfying the local constraints of B. In other words, the triggers must be in the past of all  $e_v \in B$  (well-defined triggers [50]).

Causality Condition 3: for all  $B \in P$ , the maximum time separations between pairs of triggers of B computed using all the constraints in the TD are strictly tighter than those between the same pairs of triggers computed using the local constraints of B.

Interface specifications  $TD_1$ , ...,  $TD_n$  are compatible if the following three conditions are satisfied [36][50]:

Compatibility Condition 1: Each  $TD_i$ , i = 1, ..., n, is causal.

Compatibility Condition 2: The composition TD of  $TD_i$ , i=1, ..., n, is consistent, where the composition TD is defined as a timing diagram that includes all the actions and all the commit constraints from all  $TD_i$ , i = 1, ..., n.

Compatibility Condition 3 (satisfiablility in [13] [35]): The maximum time separations between all pairs of events computed in the composition TD must be less than those between the same pairs of events computed in the TD including all the actions and all the assume constraints from all TD<sub>i</sub>, i = 1, ..., n.

In the next section, we shall show that the consistency, causality and thus the compatibility conditions can be verified by computing the maximum time separation of events.

#### 2.3 From Verification of Timing Diagrams to Maximum Time Separation

To verify the consistency of a TD, we can create a directed graph  $G = \langle E, R \rangle$ , based on the TD specification, where E, the set of events, represents actions in the TD; R, the set of rule edges, represents the timing constraints in the TD.

A TD is consistent if all actions in the TD can be assigned occurrence times without violating any timing constraint. That is, for any two events in G, it is possible to compute the maximum time separation between them. In the case of linear-only systems, a TD is consistent if there is no negative cycle in G [35], [20].

The second causality condition can be verified by computing the maximum time separation of events in the constraint graph derived from the composition TD. The condition can be verified by checking whether the minimum time separations from the events in the block to the related triggers are smaller than 0, i.e., the maximum time separations from the triggers to their related sink events in the block are greater than 0.

The third causality condition is explicitly stated as comparing the maximum time separation between the same pairs of events in two different constraint graphs.

Since the compatibility of interface specification can be verified by consistency and causality of individual or composition of timing diagrams involved in the specifications, we can conclude that compatibility verification can be solved by computing the maximum time separation of events in constraint graphs extracted from the specification.

## 2.4 Related Work

As illustrated in Section 2.3, the causality and compatibility verification of interface specifications can be reduced to computing the maximum time separations between pairs of events in constraint graphs. In Chapter 3, we shall show that the maximum time separation of events can also be applied to solve other safety timing properties of interface specifications.

The maximum time separation problem has been explored by many researchers from different fields. Algorithms have been proposed under various restrictions on the constraint systems ([21][22][37][50][62][78][80][83]). All the restrictions can be put into two categories: a) on the type of constraints, and b) on whether the events in the specification are allowed to occur repeatedly. When the events in the specification can occur only once, the problem is well solved in any combination of timing constraints. The complexity of the algorithms ranges from polynomial for the linear-only systems to NP-complete for max-plus-min-plus-linear systems. This can be summarized as follows:

For systems with linear-only constraints, a shortest path algorithm, e.g., Floyd-Warshall algorithm [33][35] can be used, the complexity of the algorithm is  $O(n^3)$ where n is the number of events in the constraint graph. Vanbekberge [78], and McMillan and Dill [62] proposed algorithms for max-only and min-only systems with complexity  $O(n^3)$ . Yen et al. [83] gave an algorithm to calculate the maximum separations in systems combining either max or min constraints with linear constraint in the complexity of  $O(n^3 \log n)$ . Walkup and Borriello [80][81] presented an algorithm for solving the same problem with the complexity of  $O(n^6)$  which is unproven. The complexity of the algorithm by McMillan and Dill [62] is pseudo polynomial in  $O(n^3 \sum_{ij} s_{ij})$ , where  $\sum_{ij} s_{ij}$  is the sum of all the initial timing separations (the timing bounds in Relations (2.2) and (2.3)). They showed that whenever both max and min constraints are present, the maximum time separation problem becomes NP-complete. A branch-and-bound algorithm based on an algorithm for max-plus-linear or min-plus-linear constraints is appropriate in such cases. Burks et al [15] proposed a branch-and-bound algorithm and a mixed integer linear programming method to compute the maximum time separation in systems containing min and max constraints. Girodias et al. [37] use Constraint Logic Programming (CLP) environment based on Relational Interval Arithmetical (RIA) to solve the maximum time separation problem for linear-only, max(min)-only, max(min)-plus-linear, and max-plus-min-plus-linear systems with similar complexity as the other algorithms. Their approach can also solve the problem when delay correlation exists in the system, a problem which is difficult to handle by the other approaches [36]. Chakraborty et al. [22] presented a polynomial-time approximate algorithm for computing the maximum time separations in systems containing min-plus-max constraints.

All the above algorithms are only applicable to acyclic finite specifications. Cycles are necessary to model repetitive interface behaviours (e.g., Loop over a leaf TD in

HAAD specifications). Cyclic behaviours make the problem more complicated because the effective number of events and constraints becomes infinite.